Fターム[5F058BD02]の内容

絶縁膜の形成 (41,121) | 無機積層絶縁膜の構造、材料 (4,921) | 三層以上 (272)

Fターム[5F058BD02]に分類される特許

261 - 272 / 272

半導体素子のパッシベーション膜形成方法及び半導体素子のパッシベーション膜構造

【課題】 本発明は、選択ソースラインと共通ソースライン間の漏れ電流を著しく減少させることが可能な半導体素子のパッシベーション膜形成方法及び半導体素子のパッシベーション膜構造を提供することを目的としている。

【解決手段】 半導体基板上に金属配線を形成する段階と、前記金属配線上にプラズマによる損傷を緩衝することが可能な第1パッシベーション膜のバッファ酸化膜を形成する段階と、前記バッファ酸化膜上に第2パッシベーション膜の高密度プラズマ(HDP)膜を形成する段階と、前記第2パッシベーション膜上に第3パッシベーション膜を形成する段階とを含んで半導体素子のパッシベーション膜を形成する構成としたことを特徴とする。

(もっと読む)

薄膜トランジスターの製造方法

【課題】 本発明の目的は、以下に記載の構成をとることにより従来と比較して優良な特性を有する薄膜トランジスターを作成するための方法を提供することにある。

【解決手段】 薄膜トランジスターは、アモルファスシリコンを堆積させ、ゲート構造を形成し、次いで、高圧酸化を用いて、層化構造を有する高性能ゲート酸化物を形成することにより作成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 遷移金属化合物膜を含むゲート絶縁膜を有する半導体装置のリーク電流及び閾値電圧のシフトを抑制する。

【解決手段】 半導体装置は、高誘電率材料である遷移金属化合物膜からなるゲート絶縁膜104と、n型又はp型のドーパントを含み且つ多結晶シリコン又はシリコン化合物からなるゲート電極105とを備え、ゲート絶縁膜104に含まれる炭素及びハロゲン元素の総量が0.1atomic%以下となっている。このような純度の膜は、遷移金属をターゲットとするスパッタ法によって成膜することによって実現でき、特に、純度が99.999atomic%以上の遷移金属をターゲットとして用いると確実に実現できる。

(もっと読む)

ウェハ用二層LTO背面シール

ウェハ用二層LTO背面シール。二層LTO背面シールは、第一の主要面と第二の主要面とを有する低応力LTO層を含み、この場合、低応力LTO層の第一の主要面はウェハの主要面の1つに隣接している。二層LTO背面シールは、更に、第一の主要面と第二の主要面とを有する高応力LTO層を含み、この場合、この場合、高応力LTO層の第一の主要面は低応力LTO層の第二の主要面に隣接している。  (もっと読む)

(もっと読む)

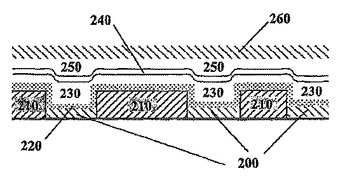

low−kスピンオン誘電体膜におけるクラッキングの減少

本発明は、low−k誘電体高分子のクラッキングを最小限に抑制するプロセスに関する。実施の一形態では、プラズマ蒸着された酸化シリコンSiOXで不動態化された金属層(220)上に配置される複合誘電体(230,240,250,260)を半導体基板(200)上に形成する方法がある。その方法は、プラズマ蒸着された酸化シリコンSiOX(220)で保護された金属層(210)上にスピンオン誘電体からなる第1の所定の厚さの第1の層を堆積させるステップ(310,320)を含む。次に、第2の所定の厚さの薄い応力緩和層(240)が、スピンオン誘電体からなる第1の層(230)上に堆積される(330)。薄い応力緩和層(230)上には、スピンオン誘電体からなる第3の所定の厚さの第2の層(250)が堆積される(340,350)。low−kスピンオン誘電体は、水素メチルシルセスキオキサン(HSQ)及びメチルシルセスキオキサン(MSQ)を含んでいてもよい。  (もっと読む)

(もっと読む)

空隙を有する半導体デバイスの形成方法および該方法によって形成された構造

【課題】半導体デバイスの形成方法および該方法によって形成されたデバイスを提供すること。

【解決手段】第1の誘電材料(12a〜f)と第2の誘電材料(14a〜f)の互層を付着させる。ここで、第1の誘電材料と第2の誘電材料は異なる速度で選択的にエッチング可能である。誘電材料の互層内に第1のフィーチャ(22、24)を形成する。誘電材料の互層を選択的にエッチングして、第1の誘電材料を有するそれぞれの層内の第1の誘電材料の少なくとも一部分(26)を除去し、第2の誘電材料は本質的にエッチングされていないままにしておく。

(もっと読む)

低k誘電体と導電材料との接着改善

導電材料と誘電体層間の接着層を堆積させるために基板を処理する方法が提供される。一態様においては、本発明は、基板を処理する方法であって、導電材料が基板表面上に配置された基板を配置するステップと、基板表面を還元化合物、シリコンベースの化合物、又はその双方に曝すステップと、基板表面の少なくとも一部と該還元化合物、シリコンベースの化合物、又はその双方とを反応させるステップと、炭化シリコン層を真空を破壊せずに堆積させるステップと、を含む前記方法を提供する。 (もっと読む)

high−kゲート誘電体プロセスインテグレーションのための界面酸化プロセス。

【課題】 high−kゲート誘電体プロセスインテグレーションのための界面酸化プロセスの提供。

【解決手段】 界面酸化層を有した微細構造物を形成する方法は、この微細構造物内のhigh−k層の形成と関係した基板の酸化特性を制御するように拡散フィルタ層を使用することにより提供される。拡散フィルタ層は、表面の酸化を制御する。界面酸化層は、拡散フィルタ層上へのhigh−k層の堆積の後に実行される酸化プロセス中に、または拡散フィルタ層上へのhigh−k層の堆積中に、形成されることができる。

(もっと読む)

多成分誘電体膜を形成するためのシステム及び方法

【課題】半導体用途における誘電体膜を形成するためのシステム及び方法、特に、混合気化前駆体を用いて基板上に多成分誘電体膜を作製するためのシステム及び方法を提供する。

【解決手段】本発明は、気化した前駆体の混合物が、原子層堆積(ALD)処理における単一パルス段階中にチャンバ内に一緒に存在して多成分膜を形成するような気化前駆体の混合をもたらすためのシステム及び方法を提供する。気化前駆体は、少なくとも1つの異なる化学成分から成り、そのような異なる成分が単層を形成して多成分膜を生成することになる。本発明の更に別の態様では、組成勾配を有する誘電体膜が提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜の埋め込み性が高く高集積化に適切に対応することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の上方に強誘電体キャパシタを形成した後、強誘電体キャパシタを覆うAl2O3膜を形成する。その後、Al2O3膜を覆う高密度プラズマ絶縁膜を、O2ガス及びSiH4ガスを用いて形成する。このとき、O2ガスの流量をSiH4ガスの流量の6乃至9倍とすると共に、半導体基板の温度を280℃乃至320℃とする。

(もっと読む)

多層配線構造部及びその製造方法

【課題】配線容量を低減した多層配線構造部。

【解決手段】下地11と、下地11上に設けられている第1の配線層12と、下地11上に第1の配線層12を被覆するように設けられていて、互いに隣接する第1の配線層12間に凹部22bを有するライナー絶縁膜22と、凹部22bに設けられている埋込み絶縁膜24と、埋込み絶縁膜24を被覆しているキャップ絶縁膜26と、キャップ絶縁膜26上に設けられている第2の配線層14とを具えていて、埋込み絶縁膜24は、ライナー絶縁膜22及びキャップ絶縁膜26よりも低い誘電率を有する絶縁性材料から構成されている。

(もっと読む)

多層配線構造体およびその製造方法

【課題】多層配線構造体の製造工程のSOG膜のエッチバック工程で、第1の金属配線を露出しない構造とする。

【解決手段】表面に段差23のある絶縁膜1上に選択的に第1の金属配線2を形成し、この第1の金属配線2上にメタル系絶縁膜であるチタン酸化膜3を形成する。その露出面に第1のP−TEOS膜4を形成する。チタン酸化膜3の直上を除く第1のP−TEOS膜4の表面にSOG膜5を形成し、チタン酸化膜3上とSOG膜5上に第2のP−TEOS膜6を形成する。最後に第2のP−TEOS膜6上に第2の金属配線7を形成して、多層配線構造体が完成する。ここでは2層の金属配線2、7を例に上げたが、さらに多層の配線構造体の場合も、同様に各膜を積層することで製作できる。

(もっと読む)

261 - 272 / 272

[ Back to top ]