Fターム[5F058BD02]の内容

絶縁膜の形成 (41,121) | 無機積層絶縁膜の構造、材料 (4,921) | 三層以上 (272)

Fターム[5F058BD02]に分類される特許

121 - 140 / 272

半導体装置及びその製造方法

【課題】配向が優れた誘電体膜の存在に基づいて高いスイッチング電荷量を得ることができる半導体装置及びその製造方法を提供する。

【解決手段】Ir膜23を形成した後、このIr膜23上にIr酸化膜を形成する。次に、MOCVD法によりIr酸化膜上に初期PZT膜25aを形成すると共に、Ir酸化膜を還元によりIr膜24aに変化させる。次に、初期PZT膜25a上に、初期PZT膜25aよりも厚く、初期PZT膜25aよりも酸化度が高いコアPZT膜25bを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】CMP研磨により上面を平坦化する際にスクラッチが生じにくい半導体装置およびその製造方法を提供する。

【解決手段】半導体基板SUBの主表面に形成された下地パターン層を覆うように第1の層間絶縁膜IL1が形成されている。第2の層間絶縁膜IL2は第1の層間絶縁膜IL1上に選択的に形成されている。第3の層間絶縁膜IL3は第1および第2の層間絶縁膜IL1、IL2上を覆うように形成され、かつ上面が平坦化されている。第2の層間絶縁膜IL2の半導体基板SUBの主表面からの最上部の位置が、第1の層間絶縁膜IL1の上記主表面からの最上部の位置よりも高い。

(もっと読む)

半導体装置の製造方法

【目的】パターン密度の違いによるエッチング差を抑制する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上にポロジェン材料を含む絶縁膜を形成する工程(S104)と、前記絶縁膜に含まれる前記ポロジェン材料の一部を除去する工程(S106)と、前記ポロジェン材料の一部が除去された前記絶縁膜に前記絶縁膜の底部を残すように開口部を形成する工程(S112)と、前記絶縁膜に含まれる前記ポロジェン材料の残部を除去する工程(S114)と、前記開口部の前記底部をエッチングする工程(S116)と、を備えたことを特徴とする。

(もっと読む)

絶縁膜の形成方法、コンピュータ読み取り可能な記憶媒体および処理システム

【課題】 CVD法によって絶縁膜を形成する場合に、シリコンと絶縁膜との界面の形状を極めて平坦化することが可能な絶縁膜の形成方法を提供する。

【解決手段】 複数の孔を有する平面アンテナ31によりチャンバ1内にマイクロ波を導入するプラズマ処理装置100を用い、シリコン表面を酸化して酸化珪素膜を形成する(ステップS1)。この酸化珪素膜上にCVD法により絶縁膜としての酸化珪素膜を成膜し(ステップS4)、さらに、プラズマ処理装置100を用い、チャンバ1内に希ガスと酸素を含む処理ガスを導入するとともに平面アンテナ31によりマイクロ波を導入し、6.7Pa以上267Pa以下の範囲内の圧力条件でプラズマを発生させ、該プラズマにより、絶縁膜を改質する(ステップS6)。

(もっと読む)

半導体装置およびその製造方法

【課題】十分なEM耐性および配線間TDDB寿命を確保しつつ、層間絶縁膜の低誘電率化を行っても絶縁膜ライナー膜厚を薄くすることができ、配線間の実効比誘電率Keffを低減した高速で高信頼性な配線を得ることができる。

【解決手段】第1の絶縁膜1には配線溝M1が形成されており、配線溝M1内にはCu膜2bが設けられている。Cu膜2bの上にはSiCN膜3a、SiCO膜3bおよびSiOC膜4aが順に設けられており、SiOC膜4aはSiCN膜3aおよびSiCO膜3bよりも低誘電率な絶縁膜である。SiCO膜3bの上面には、高密度化処理が施されて高密度膜3cが形成されている。

(もっと読む)

強誘電体膜、金属酸化物、半導体装置、及びそれらの製造方法

【課題】 強誘電体膜厚が薄く、長期のデータ保持特性を有する強誘電体メモリー装置に用いられる半導体装置、その製造方法、その製造装置、強誘電体膜及び強誘電体膜の製造方法を提供すること。

【解決手段】 強誘電体膜57は、膜材料として、Sr、Ta、及びNbを主成分とする強誘電体材料が用いられ、10日以上のデータ保持時間を有する。強誘電体膜を製造する方法は、強誘電体膜57を形成する膜形成工程と、前記強誘電体膜57を酸素ラジカル58によって酸化する酸素導入工程とを有する。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】金属薄膜上に金属酸化膜を形成する際に、金属薄膜の酸化を抑制させることが可能な半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】基板200上にチタン酸ストロンチウムまたはチタン酸ストロンチウムバリウムの薄膜を形成する工程を有する半導体装置の製造方法であって、薄膜を形成する工程は、基板上に二酸化チタンの層を数層形成する工程と、数層形成した二酸化チタンの層の上に酸化ストロンチウムと二酸化チタンとを含む積層膜、または酸化バリウムと酸化ストロンチウムと二酸化チタンとを含む積層膜を形成する工程と、を有する。

(もっと読む)

半導体装置、および半導体装置の作製方法

【課題】良好な品質を有する微結晶半導体膜を有する半導体装置及び該半導体装置の作製方法を提供することを課題とする。

【解決手段】微結晶半導体膜を用いて形成される薄膜トランジスタにおいて、成膜初期に形成される微結晶半導体膜の品質を向上するため、ゲート絶縁膜最上層に、蛍石型構造を持つイットリア安定化ジルコニア膜を形成する。その上に微結晶半導体膜を堆積させることにより、特に下地との界面付近は下地の結晶性に影響を受け良好な結晶性が得られる。また、微結晶半導体膜を形成する前に、表面プラズマ処理を行い、下地の結晶性に影響されやすい状態で微結晶半導体膜を堆積する。さらに、下地のイットリア安定化ジルコニアと微結晶半導体膜の結晶が一致しやすいように、微結晶半導体膜にゲルマニウムを添加する。

(もっと読む)

アモルファスカーボン膜の処理方法およびそれを用いた半導体装置の製造方法

【課題】エッチング加工後のアモルファスカーボン膜をウエット洗浄した際の酸化による劣化を抑制することができるアモルファスカーボン膜の処理方法を提供すること。

【解決手段】基板上に成膜され、ドライエッチング後にウエット洗浄処理が施されたアモルファスカーボン膜の処理方法であって、ウエット洗浄処理後、上層の形成前に、アモルファスカーボン膜の表面改質処理を行う。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】電荷蓄積層および制御ゲート電極層間に設けられる第2のゲート絶縁膜を通じて流れるリーク電流を抑制できるようにする。

【解決手段】ゲート間絶縁膜7が、浮遊ゲート電極FGと制御ゲート電極CGとの間に、浮遊ゲート電極FG側から制御ゲート電極CG側にかけて、シリコン窒化膜7aa/高誘電体絶縁膜7ab/シリコン酸化膜7ac/高誘電体絶縁膜7b/シリコン酸化膜7ca/シリコン窒化膜7cbによる積層構造により構成されているため、リーク電流を抑制できる。

(もっと読む)

ゲート絶縁膜の形成方法

【課題】ゲート絶縁膜に用いる高誘電体金属酸化膜又は高誘電体金属シリケート膜におけるリーク電流を低減できるようにする。

【解決手段】高誘電体金属シリケートからなるゲート絶縁膜の形成において、金属等を含む前駆体の暴露時間には、表面吸着反応により成膜レートが飽和する時間を用い、酸化剤の暴露時間には、金属酸化膜の組成が化学量論値の97%以上となる時間を用いてALD堆積を行う。

(もっと読む)

不揮発性半導体メモリ装置

【課題】フローティングゲート電極とコントロールゲート電極を積層したスタックゲート構成において、トンネル絶縁膜と電極間絶縁膜を改良した不揮発性半導体メモリ装置を提供する。

【解決手段】第1導電型の半導体基板10の主面上にトンネル絶縁膜11を介して選択的に形成されたフローティングゲート電極12と、フローティングゲート電極12上に電極間絶縁膜13を介して形成されたコントロールゲート電極14と、各ゲート電極12,14に対応して基板10の主面に形成された第2導電型のソース・ドレイン領域15とを備えた不揮発性半導体メモリであって、トンネル絶縁膜11は、少なくとも2種の金属元素(Al,Hf)と酸素(O)を含む高誘電体膜であり、膜の厚さ方向に対して金属元素の組成が連続的に変化し、かつ対称的な分布を有する。

(もっと読む)

成膜方法及び成膜装置

【課題】薄膜の膜質特性を精度良く制御することが可能な成膜方法を提供する。

【解決手段】複数枚の被処理体Wが収容されて真空引き可能になされた処理容器4内に、シラン系ガスと窒化ガスとを供給して被処理体の表面にシリコン窒化膜よりなる薄膜を形成する成膜処理を行うようにした成膜方法において、シラン系ガスを供給するシラン系ガス供給工程と窒化ガスを供給する窒化ガス供給工程とを交互に繰り返し行うと共に、繰り返される複数の窒化ガス供給工程にはプラズマを立てる窒化ガス供給工程とプラズマを立てない窒化ガス供給工程とを含ませることにより薄膜の膜質を制御する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタの性能向上を図ってスペーサを形成できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、ゲートを覆って、半導体基板上に、高誘電体材料を含むバリア絶縁膜を形成する工程と、バリア絶縁膜上に、スペーサ絶縁膜を形成する工程と、スペーサ絶縁膜を、異方性エッチングして、ゲートの側壁上にスペーサを残して除去する工程と、露出したバリア絶縁膜を除去する工程と、ゲート及びスペーサをマスクとして、半導体基板に不純物を注入し、エクステンションを形成する工程と、さらにサイドウォールを形成し、ゲート、スペーサ、及びサイドウォールをマスクとして、ソース/ドレイン領域を形成する工程とを有する。

(もっと読む)

半導体メモリ素子の素子分離膜形成方法

【課題】 本発明は、トレンチの底面に流動性の第1の絶縁膜を満たし、第2の絶縁膜を形成した後に乾式エッチング工程及び湿式エッチング工程を行ってトレンチの上部の幅を広げながら第2の絶縁膜に含まれるフッ素(F;fluorine;フローリン)の量を減少させることができる半導体メモリ素子の素子分離膜形成方法を提供することを可能にすることを目的としている。

【解決手段】 トレンチが形成された半導体基板が提供される段階と、トレンチを含む半導体基板上に第1の絶縁膜を形成する段階と、第1の絶縁膜の一部を除去する第1のエッチング工程を行ってトレンチの開口部の幅を広げる段階と、第2のエッチング工程を行って第1の絶縁膜内に含まれた不純物を除去する段階と、第1の絶縁膜を含む半導体基板上に第2の絶縁膜を形成する段階とを含む構成としたことを特徴とする。

(もっと読む)

積層体およびその製造方法ならびに半導体装置

【課題】低い比誘電率を有し、かつ密着性に優れた積層体およびその製造方法、ならびに該積層体を含む半導体装置を提供する。

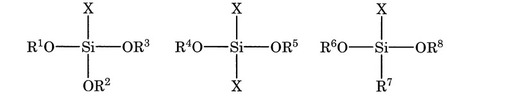

【解決手段】積層体は、シリカ系膜および有機系膜を含み、前記シリカ系膜と前記有機系膜とが、アルキル基、アシル基またはアリール基、と水素原子、フッ素原子、アルキル基、またはアリール基を有し2重結合を含む炭化水素基を有するアルコキシシランシラン化合物を硬化させて得られる層間膜を介して積層する。 (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率膜をゲート絶縁膜として用い、pチャネル型MISFETおよびnチャネル型MISFETのそれぞれに要求されるしきい値電圧を容易に実現できる相補型MISFETおよびその製造技術を提供する。

【解決手段】n型ウエル3およびp型ウエル4のそれぞれの表面に清浄な酸化シリコン膜5を形成した後、酸化シリコン膜5上に2A族元素の酸化物、3A族元素の酸化物、3B族元素の酸化物、4A族元素の酸化物、および5A族元素の酸化物等からなる酸素欠損調整層6と、高誘電率膜8と、水素に対する還元触媒効果を有する導電性膜12とを順次堆積し、H2を含む雰囲気中にて基板1に対して熱処理を施すことで酸素欠損調整層6と酸化シリコン膜5との間にダイポールを形成する。その後、導電性膜12、高誘電率膜8、酸素欠損調整層6および酸化シリコン膜5等をパターニングしてゲート電極およびゲート絶縁膜を形成する。

(もっと読む)

成膜方法、成膜装置及び記憶媒体

【課題】α-アルミナを含むアルミナ膜の成膜温度の低温化を図ることができる成膜方法等を提供する。

【解決手段】

処理容器2内に被処理体(ウエハW)を載置し、有機アルミニウム化合物を含む原料ガスと、水蒸気等の水素原子、酸素原子を含む酸化ガスとを当該処理容器2内に導入する。次いで当該処理容器2内の処理雰囲気を200℃以上500℃以下の温度範囲に加熱して、被処理体の上にダイアスポアを含む含酸素アルミニウム化合物の膜を形成し、当該被処理体を800℃以上、1,000℃以下の温度範囲で加熱して、当該含酸素アルミニウム化合物の膜を、α-アルミナを含むアルミナ膜に変化させる。

(もっと読む)

半導体装置の層間絶縁膜構造とその製造方法、及び半導体装置とその製造方法

【課題】Si系絶縁膜との密着性向上が図られたCFx膜を用いた半導体装置の層間絶縁膜構造を提供する。

【解決手段】半導体装置の層間絶縁膜構造は、下側のSi系絶縁膜と、上側のSi系絶縁膜と、下側及び上側のSi系絶縁膜に挟まれ、厚さ方向の中間のF組成xよりもSi系絶縁膜との界面のF組成xが小さいCFx絶縁膜とを有する。

(もっと読む)

セラミックス膜およびその製造方法ならびに半導体装置、圧電素子およびアクチュエータ

【課題】セラミックス膜の表面モフォロジを改善することができる、セラミックス膜の製造方法を提供する。このセラミックス膜の製造方法により得られたセラミックス膜を提供する。このセラミックス膜が適用された半導体装置および圧電素子を提供する。

【解決手段】セラミックス膜の製造方法は、原材料体20を結晶化することにより、セラミックス膜30を形成する工程を含み、原材料体20は、種類が異なる原料を混在した状態で含み、種類が異なる原料同士は、原料の結晶化における結晶成長条件および結晶成長機構の少なくとも一方が相互に異なる関係にある。

(もっと読む)

121 - 140 / 272

[ Back to top ]