Fターム[5F058BD02]の内容

絶縁膜の形成 (41,121) | 無機積層絶縁膜の構造、材料 (4,921) | 三層以上 (272)

Fターム[5F058BD02]に分類される特許

61 - 80 / 272

MIS型半導体装置及びその製造方法

【課題】半導体集積回路のトランジスタのゲート絶縁膜を、安定な高誘電率絶縁膜で構成した、リーク電流が小さくしかも駆動力の大きい、MIS型半導体装置を提供する。また、閾値電圧のバラツキの小さい、量産可能で安価な高誘電率ゲート絶縁膜の製造方法を提供する。

【解決手段】アルミニウム酸化物層と、ジルコニウムまたはハフニウムのシリコン酸化物層とを積層した積層ゲート絶縁膜を用いたMIS型半導体装置。ジルコニウムまたはハフニウムのシリコン酸化物層を、導電チャネル側に設置する。

(もっと読む)

半導体装置の製造方法

【課題】高い比誘電率が確保されており且つ熱的に安定なゲート絶縁膜を用いた半導体装置を実現できるようにする。

【解決手段】基板20上に、水素を含むHfO2 膜22Aを形成した後、HfO2 膜22Aに対して熱処理を行なうことにより、基板20側からシリコンをHfO2 膜22A中に拡散させてシリコン含有HfO2 膜22を形成する。その後、シリコン含有HfO2 膜22の上にゲート電極となるポリシリコン膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の向上に寄与し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10上にトランジスタ34を形成する工程と、半導体基板上及びトランジスタ上に複数の部分膜36a、38a、40a、42を積層することにより、複数の部分膜を有する第1の絶縁層44を形成する工程と、第1の絶縁層上に、第1の絶縁層とエッチング特性が異なる第2の絶縁層46を形成する工程と、第1の絶縁層をエッチングストッパとして、第2の絶縁層をエッチングすることにより、第2の絶縁層にコンタクトホールを形成する工程と、コンタクトホール内に露出する第1の絶縁層をエッチングする工程とを有し、第1の絶縁層を形成する工程では、複数の部分膜のうちの最上層の部分膜以外の部分膜に対して膜を収縮させるキュア処理を行い、複数の部分膜のうちの最上層の部分膜に対してキュア処理を行わない。

(もっと読む)

層間絶縁膜および配線構造と、それらの製造方法

【課題】 低誘電率で且つCFx、SiF4等のガスの発生がなく安定な半導体装置の層間絶縁膜とそれを備えた配線構造を提供する。

【解決手段】 下地層上に形成された絶縁膜を備えた層間絶縁膜において、前記層間絶縁膜は、実効誘電率が3以下である。配線構造は、層間絶縁膜と、層間絶縁膜に形成されたコンタクトホールと、前記コンタクトホール内に充填された金属とを備え、前記絶縁膜は、前記下地層上に形成され、表面が窒化されたフルオロカーボン膜を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】同一基板上に複数のゲート絶縁膜を有する半導体装置において、例えばコア部におけるHPトランジスタの高速性の確保と、例えばI/Oトランジスタ及びLPトランジスタのゲート耐圧の向上やゲートリーク電流の低減とを両立する。

【解決手段】半導体装置は、半導体基板11上に形成された複数のゲート絶縁膜を備えており、複数のゲート絶縁膜のうち、HPトランジスタ形成領域1Cにおける膜厚が最も薄いゲート絶縁膜は、シリコン酸化膜20よりなり、I/Oトランジスタ形成領域1A及びLPトランジスタ形成領域1Bにおける残りのゲート絶縁膜は、シリコン酸窒化膜16、17よりなる。

(もっと読む)

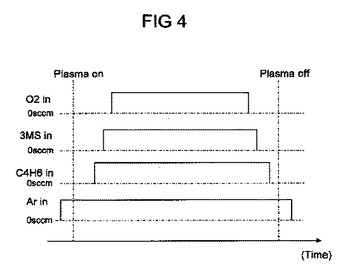

アモルファスカーボンのドーピングによるフルオロカーボン(CFx)の接合の改善

絶縁層上にアモルファスカーボン層を形成する方法は、プラズマ反応プロセスを用いることによってアモルファスカーボン層を形成する工程を有する。前記アモルファスカーボン層は、プラズマ励起ガス、一連のCxHyガス、シリコン含有ガス、及び酸素含有ガスを含む雰囲気中で形成される。  (もっと読む)

(もっと読む)

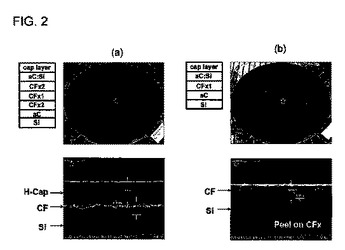

プラズマ処理方法

絶縁層としてフッ素化炭素層を持つ半導体装置を製造する方法であり、前記方法は:マイクロ波パワー励起プラズマを用いて第1のフッ素化炭素(CFx1)層を形成するステップ;及びRFパワー励起プラズマを用いて第2のフッ素化炭素(CFx2)層を形成するステップを含む。  (もっと読む)

(もっと読む)

超高品質シリコン含有化合物層の形成方法

【課題】ALDがCVDに比べて優れたコンフォーミティ(coformality)、成膜速度及び均一性を備えた気相堆積方法を提供する。

【解決手段】シリコンナイトライド層を含む、超高品質シリコン含有化合物層を形成するため、複数の順次的なステップ140が、反応チャンバー中で実施される。好ましい実施態様において、シリコン前駆物質としてトリシランを用いて、シリコン層が基板上に堆積100される。シリコン前駆物質は、反応チャンバーから除去される110。その後、シリコンナイトライド層が、シリコン層を窒化すること120によって形成される。窒素反応物質は、反応チャンバーから除去される110。これらのステップ100、110、120及び130を繰り返すことによって、所望の厚さのシリコンナイトライド層が形成される。

(もっと読む)

半導体装置

【課題】不揮発性メモリセルの電荷保持特性の劣化の抑制を図れる半導体装置を提供する。

【解決手段】不揮発性メモリセルは、トンネル絶縁膜2と、電荷蓄積層3と、絶縁層4(41,42)と、制御電極5と、ソース/ドレイン領域6とを含み、素子分離絶縁膜7とを備し、チャネル幅方向において、絶縁層4は、電荷蓄積層3の上面に接した第1の絶縁層41と、電荷蓄積層3の端部に接した第2の絶縁層42とを含み、かつ、第2の絶縁層42の外側にある素子分離絶縁膜7の上面は、トンネル絶縁膜2と電荷蓄積層3との界面よりも上にある。

(もっと読む)

半導体装置の製造方法

【課題】フッ酸に対する化学耐性を備え、650℃以下の低温で形成可能な窒化シリコンを堆積してキャパシタ電極のサポート用絶縁膜や薬剤浸透防止用の層間絶縁膜を備えた半導体装置の製造方法を提供する。

【解決手段】コンタクトプラグがその上端を露出するように埋込まれた下部層間絶縁膜上に、薬剤浸透防止用の窒化シリコンからなる第1層間絶縁膜を形成する工程と、第1層間絶縁膜上に第2層間絶縁膜を形成する工程と、第2層間絶縁膜上にキャパシタ素子の下部電極の立設を保持するための窒化シリコンからなるサポート用絶縁膜を形成する工程と、サポート用絶縁膜を一部残存させて、第2層間絶縁膜を湿式エッチングにより除去してキャパシタ素子の下部電極を形成する工程とを備え、第1層間絶縁膜及びサポート用絶縁膜の少なくとも一方を高密度プラズマCVD法で形成する半導体装置の製造方法とする。

(もっと読む)

半導体装置及びその製造方法

【課題】配線遅延の増大を防止すると共に、配線信頼性の低下を抑制する。

【解決手段】半導体装置は、基板の上に形成され、第1の配線2を有する第1の絶縁膜1と、第1の絶縁膜1及び第1の配線2の上に形成された第2の絶縁膜3と、第2の絶縁膜3の上に形成された第3の絶縁膜4とを有している。第2の絶縁膜3は、空孔を含んでいる。

(もっと読む)

MOSトランジスタ

【課題】MOSトランジスタを作成する。

【解決手段】MOSトランジスタであって、ゲート電極と、ゲート電極下地の頂部表面を有するチャンネル領域と、ゲート電極とチャンネル領域の頂部表面の間に挿入された誘電体スタックとを含み、前記誘電体スタックが、少なくとも高―k材料を含む高―k誘電体層と、少なくともケイ素および窒素を含む誘電体層と、前記高―k誘電体層と前記誘電体層の間に配設された中間層とを含み、該中間層が、少なくとも前記高―k材料、ケイ素および窒素を含み、前記ゲート電極がポリシリコンまたはポリシリコンゲルマニウムから作製される。

(もっと読む)

酸化ストロンチウムルテニウム界面

酸化ストロンチウムルテニウムは、ルテニウム伝導体と酸化ストロンチウムチタン誘電体との間に有効な界面を提供する。酸化ストロンチウムルテニウムの形成は、酸化ストロンチウムを形成するための原子層堆積の使用と、その後の酸化ストロンチウムルテニウムを形成するための酸化ストロンチウムの焼鈍とを含む。酸化ストロンチウムの第1の原子層堆積は水を酸素源として使用して行われ、続いて、その後の酸化ストロンチウムの原子層堆積がオゾンを酸素源として使用して行われる。 (もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極が微細化されても電流コラプスを抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】表面保護膜10を形成する際に、化合物半導体積層構造上に第1の絶縁膜10aを形成し、第1の絶縁膜10aの表面に、酸素原子又は窒素原子の少なくとも一方を第1の絶縁膜10aよりも多く含む第2の絶縁膜10bを形成し、第2の絶縁膜10bの上方に、第1の絶縁膜10aよりもSi−H結合を少なく含み、第1の絶縁膜10aよりも高い絶縁性を示す第3の絶縁膜10cを形成する。

(もっと読む)

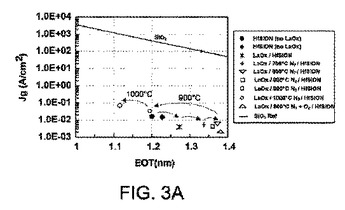

低減された等価酸化膜厚を有する高誘電率ゲートスタックの形成方法

低減された均等酸化物厚さ(EOT)を持つhigh−kゲートスタックを形成する方法を提供し、該方法は:シリコン含有基板を準備し;前記シリコン含有基板上に境界層を形成し、前記境界層が第一の等価酸化物厚さを有し;前記境界層上に第一のhigh−k膜を堆積し;前記第一のhigh−k膜及び前記境界層を、前記第一の等価酸化物厚さと等しいかそれより小さい第二の等価酸化物厚さを持つ変性境界層を形成する温度で熱処理し;及び前記変性境界層上に第二のhigh−k膜を堆積する方法である。ひとつの実施態様によると、前記第一のhigh−k膜がランタン酸化物を含み、前記第二のhigh−k膜がハフニウムシリケートを含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 CVD−MnOxをバリア膜に用いても歩留りの低下を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】 N層以上の銅、又は銅合金配線4、8を有し、これらN層の銅、又は銅合金配線4、8のバリア膜としてCVD−MnOx膜を使用する半導体装置の製造方法であって、第1層乃至第N−1層のCVD−MnOx膜3は、セルフリミットがかかる前に成膜を完了させ、第N層のCVD−MnOx膜7は、セルフリミットがかかるように成膜する。

(もっと読む)

有機電気装置のための封入方法

本開示は、障壁層を電子装置に封入するための使用に適した方法および材料を提供する。一実施形態では、たとえば、ケイ素含有結合材料およびセラミック材料の交互する層によって封入された、電気発光装置または他の電子装置を提供する。本封入方法は、たとえば、安定性および貯蔵寿命が増加した電子装置を提供する。本発明は、たとえばマイクロ電子装置の分野において有用である。別の態様では、基材上に配置された複数の構成要素層を含む電子装置と、障壁材料および架橋結合した材料の第1の対の層を含む封入部分とを含み、障壁材料がセラミック材料であり、架橋結合した材料がケイ素含有ポリマーである、封入された電子装置を提供する。 (もっと読む)

多層膜の形成方法及び表示パネルの製造方法

【課題】予め定めた形状にパターニングされた導電層の上下に配置されている絶縁層のそれぞれにコンタクトホールを形成し、これらコンタクトホールを介して互いに異なる層として形成された2つの導電層を互いに電気的に接続する場合であっても、導電不良が生じ難い多層膜の形成方法及び表示パネルの製造方法を提供する。

【解決手段】基板2上に成膜された第1導電層40上に第1絶縁層20を成膜し、前記第1絶縁層20上に第2導電層41を成膜し、前記成膜した第2導電層41をパターニングし、パターニングされた前記第2導電層41を覆うように前記基板2上に第2絶縁層25を成膜し、前記第2絶縁層25上に該第2絶縁層25よりもエッチング速度が速い第3絶縁層26を成膜し、前記第1絶縁層20、前記第2絶縁層25及び前記第3絶縁層26に対して前記第1導電層40の少なくとも一部を露出させるコンタクトホールを一括形成する。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】形成する薄膜の下地との界面の膜質向上、膜質制御を可能にする。

【解決手段】処理室内に載置された基板の表面に、第1の元素を含む第1の処理ガス及び第2の元素を含む第2の処理ガスを交互に供給して第1の薄膜を形成し、第1の元素を含み第1の処理ガスと異なる元素成分を有する第3の処理ガスを交互に供給して第1の薄膜の上に第1の薄膜と同じ元素成分を有する第2の薄膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、デバイス特性及び信頼性を向上させる。

【解決手段】半導体装置を、半導体基板6上に形成された化合物半導体積層構造1と、少なくとも化合物半導体積層構造1の表面に露出している部分を覆う第1絶縁膜4と、第1絶縁膜4上に形成された第2絶縁膜5とを備えるものとし、第1絶縁膜4を、引張応力が作用する膜とし、第2絶縁膜5を、第1絶縁膜4よりも水素を多く含んでおり、引張応力が作用する膜とする。

(もっと読む)

61 - 80 / 272

[ Back to top ]