Fターム[5F058BD02]の内容

絶縁膜の形成 (41,121) | 無機積層絶縁膜の構造、材料 (4,921) | 三層以上 (272)

Fターム[5F058BD02]に分類される特許

21 - 40 / 272

半導体装置の製造方法

【課題】希土類金属を含有するHigh-k膜のエッチング残渣を抑制するための半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に絶縁膜4を形成する工程と、絶縁膜4の上に希土類元素含有酸化膜7、12を形成する工程と、フッ酸、塩酸、硫酸を含む薬液により希土類元素含有酸化膜7、12をエッチングする工程とを有し、これにより希土類元素含有酸化膜7、12のエッチングを良好に行う。

(もっと読む)

半導体装置及びその製造方法

【課題】保護膜としてSiN膜が使用されている場合であっても、素子動作特性の変動を軽減することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置2は、ドレインドリフト領域12を有する半導体基板11と、ドレインドリフト領域12上に形成されたフィールド酸化膜17と、ゲート電極18と、中間絶縁膜17と、メタル層21,22と、これらを覆うSiN膜23と、SiN膜23上にO3−TEOSを用いたCVD法により形成され、カーボンを含有するPSG膜24とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】High-kゲート絶縁膜を用いたMOSFETにおいて、信頼性劣化、チャネル移動度低下及びEOTの増加を抑制する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板101上に、シリコン酸化物を含む第1絶縁層104を形成する工程(a)と、第1絶縁層104上に第1金属層105を形成する工程(b)と、第1金属層105上にゲート電極108を形成する工程(c)とを備える。第1絶縁層104及び第1金属層105からゲート絶縁膜を形成する。

(もっと読む)

成膜方法および成膜装置

【課題】凹凸形状部位にもリーク電流が小さく高誘電率のジルコニア系膜を確実に成膜することができる成膜方法および成膜装置を提供すること。

【解決手段】真空保持可能な処理容器内に被処理体を挿入し、処理容器内を真空に保持した状態とし、処理容器内にジルコニウム原料と酸化剤とをこの順に供給して被処理体上にZrO膜を形成する第1工程と、前記処理容器内にジルコニウム原料とシリコン原料と酸化剤とをこの順で供給して被処理体上にSiがドープされたZrO膜を形成する第2工程とを、それぞれの回数を調整して実施することにより、膜中のSi濃度を制御しつつ所定膜厚のジルコニア系膜を成膜する。

(もっと読む)

成膜方法及び処理システム

【課題】比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成することが可能な成膜方法を提供する。

【解決手段】絶縁層1が表面に形成された被処理体Wに対して成膜処理を施す成膜方法において、第1の金属よりなる第1の薄膜60を形成する第1の薄膜形成工程と、前記第1の薄膜を酸化して酸化膜60Aを形成する酸化工程と、前記酸化膜上に第2の金属を含む第2の薄膜62を形成する第2の薄膜形成工程とを有する。これにより、比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成する。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ポーラスLow−k膜の信頼性を向上させる。

【解決手段】プラズマCVD法によって層間絶縁膜IL2を形成する際にCVD装置内に供給するポロジェンの流量を、ポロジェンおよびメチルジエトキシシランの合計の流量の30%以上60%以下とすることで、層間絶縁膜IL2内に形成される空孔10の大きさを小さくし、プロセスダメージによって層間絶縁膜IL2の表面に変質層CLが形成されることを防ぐ。また、水分を含む変質層CLの形成を抑えることで、各配線を構成するバリア膜および主導体膜の酸化を防ぎ、各配線間の耐圧の劣化を防ぐ。これにより、層間絶縁膜IL2に隣接して形成される配線のEM寿命および前記配線の線間TDDB寿命の劣化を防ぐ。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】信頼性および再現性が優れるとともに、歩留まりが高く生産性が優れた薄膜トランジスタおよびその製造方法を提供する。

【解決手段】薄膜トランジスタの製造方法は、基板上にゲート電極を形成する工程と、ゲート電極を覆って基板上に第1の絶縁膜を形成し、第1の絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第2の絶縁膜を形成して、第1の絶縁膜、酸化物半導体膜および第2の絶縁膜からなる積層体を得る工程と、積層体の第1の絶縁膜、酸化物半導体膜および第2の絶縁膜をパターニングして、それぞれゲート絶縁層、活性層およびチャネル保護層を形成する工程と、ソース電極およびドレイン電極を形成する工程とを有する。第1の絶縁膜、酸化物半導体膜および第2の絶縁膜は、大気に曝されることなく連続して形成される。

(もっと読む)

半導体素子の窒化珪素膜、窒化珪素膜の製造方法及び装置

【課題】バイアスパワーを印加して成膜した窒化珪素膜から離脱する水素を適正に制御する半導体素子の窒化珪素膜、窒化珪素膜の製造方法及び装置を提供する。

【解決手段】プラズマ処理により基板19上に形成され、半導体素子に用いる窒化珪素膜において、当該窒化珪素膜が、水素の供給を遮断したい膜41と接する場合、当該窒化珪素膜を、基板19にバイアスを印加して形成したバイアス窒化珪素膜31と基板19にバイアスを印加しないで形成したアンバイアス窒化珪素膜32とを積層して構成すると共に、アンバイアス窒化珪素膜32を膜41に接する側に配置する。

(もっと読む)

半導体素子の窒化珪素膜、窒化珪素膜の製造方法及び装置

【課題】バイアスパワーを印加して成膜した窒化珪素膜の膜応力の変化を抑制する半導体素子の窒化珪素膜、窒化珪素膜の製造方法及び装置を提供する。

【解決手段】プラズマ処理により基板19上に形成され、半導体素子に用いる窒化珪素膜において、基板19にバイアスを印加して形成したバイアスSiN膜31を、基板19にバイアスを印加しないで形成したアンバイアスSiN膜32aとアンバイアスSiN膜32bとの間に挟み込む構造とする。

(もっと読む)

半導体装置の製造方法、基板処理方法及び基板処理装置

【課題】低誘電率、低エッチングレート、高絶縁性の特性を備える絶縁膜を形成する。

【解決手段】基板を収容した処理容器内にCVD反応が生じる条件下で所定元素含有ガスを供給することで、基板上に所定元素含有層を形成する工程と、処理容器内に炭素含有ガスを供給することで、所定元素含有層の上に炭素含有層を形成して所定元素および炭素を含む層を形成する工程と、処理容器内に窒素含有ガスを供給することで、所定元素および炭素を含む層を窒化して炭窒化層を形成する工程と、を1セットとしてこのセットを所定回数行うことで所定厚さの炭窒化層を形成する工程と、処理容器内に酸素含有ガスを供給することで、所定厚さの炭窒化層を酸化して酸炭窒化層を形成する工程と、を1サイクルとして、このサイクルを所定回数行うことで、基板上に所定膜厚の酸炭窒化膜を形成する工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】有機シロキサン系絶縁膜を用いて電気的特性に優れた半導体装置を製造する方法を提供する。

【解決手段】下層配線の上にこの順で形成された第1〜第3の絶縁膜をドライエッチングして該下層配線に至る開口部を形成し、該開口部の内面と該第3の絶縁膜の上にバリアメタル膜を形成し、該バリアメタル膜の上に該開口部を埋める導電層を形成し、該第3の絶縁膜上の該導電層と該バリアメタル膜、及び該第2、第3の絶縁膜の一部を除去し該下層配線に電気的に接続する上層配線を形成し、露出した該第2の絶縁膜と該導電層の表面を還元性プラズマ処理し、

該第2の絶縁膜は下記式で表されるアルキルアルコキシシランと非酸化性ガスとを用い、500Pa以下でプラズマCVD法により形成する

RwSixOy(OR´)z

R及びR´はCH3、wxzは正の整数、yは0または正の整数、(w/x)=2である。

(もっと読む)

シリコン酸化膜の形成方法及び太陽電池の製造方法

【解決手段】複数枚のシリコン基板を炉内で熱処理し、該基板表面にシリコン酸化膜を形成する方法であって、上記基板をこれら基板間に空隙を設けずに密着させ、上記炉の長さ方向に直立状態で重ね合わせて又は上記炉の高さ方向に積層して熱処理することを特徴とするシリコン酸化膜の形成方法。

【効果】本発明のシリコン酸化膜の形成方法を用いることで、熱酸化炉への充填枚数は飛躍的に増加するため、生産性が著しく向上する。本発明によれば、テクスチャ構造が必須となる結晶系の太陽電池の製造に極めて有効であり、また、太陽電池性能の低下も生じないため、効率のよい太陽電池の製造方法を提供できる。

(もっと読む)

成膜方法及び成膜装置

【課題】低誘電率膜への付着性が高く、低誘電率膜中への銅の拡散を効果的に防止できるバリア膜の成膜方法を提供する。

【解決手段】 成膜方法は、成膜装置100の処理容器1内に、絶縁膜が設けられたウエハWを配置する工程と、処理容器1内にTEOSなどのシリコン原子を含む化合物のガスと水蒸気などのOH基供与性ガスを供給し、絶縁膜の表面にSi−OH基を形成させる表面改質工程と、処理容器1内にマンガン含有材料を含む成膜ガスを供給し、CVD法によりSi−OH基が形成された絶縁膜の表面にマンガン含有膜を成膜する成膜工程と、を備えている。

(もっと読む)

結晶性太陽電池上の機能的および光学的グレーデッドARC層のための多層SiN

半導体装置の製造方法

【課題】本発明は、リーク電流が小さく、かつ容量の大きい容量絶縁膜を有するキャパシタを備えた半導体装置の製造方法を提供することを課題とする。

【解決手段】容量絶縁膜形成工程は、下部電極が形成された半導体基板を成膜装置内に設置する工程と、半導体基板の温度を第1の温度に保持する第1の温度調整工程と、下部電極を覆うように、第1の温度に保持された半導体基板上に第1の絶縁膜を成膜する第1の成膜工程と、半導体基板を第2の温度に保持する第2の温度調整工程と、第1の絶縁膜の表面を覆うように、第2の温度に保持された半導体基板上に第2の絶縁膜を成膜する第2の成膜工程と、第1の温度調整工程、第1の成膜工程、第2の温度調整工程、第2の温度調整工程、及び第2の成膜工程を繰り返し行うことで、前記容量絶縁膜を形成する繰り返し工程と、を含む。

(もっと読む)

キャパシタ及び半導体装置

【課題】高い絶縁破壊耐圧のMIMキャパシタを提供する。

【解決手段】半導体基板上に形成された下部電極12と、前記下部電極上に形成された第1の絶縁体膜13と、前記第1の絶縁体膜上に形成される第2の絶縁体膜14と、前記第2の絶縁体膜上に形成される第3の絶縁体膜15と、前記第3の絶縁体膜上に形成される上部電極16と、を有し、前記第1の絶縁体膜における密度は、前記第2の絶縁体膜における密度よりも高く、前記第3の絶縁体膜における密度は、前記第2の絶縁体膜における密度よりも高いことを特徴とする。

(もっと読む)

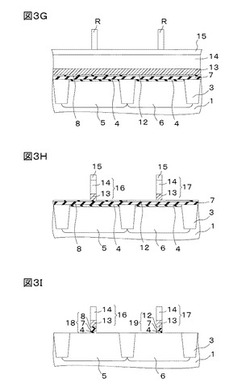

半導体装置及び半導体装置の製造方法

【課題】半導体装置の広幅の配線におけるディッシングの抑制と、抵抗の抑制と、を両立させる。

【解決手段】半導体装置100は、半導体基板1と、半導体基板1上に形成された配線層絶縁膜9と、を有している。配線層絶縁膜9には、第1配線用配線溝11と、第1配線用配線溝11よりも広幅の第2配線用配線溝12と、が形成されている。第1配線用配線溝11内には第1配線21が、第2配線用配線溝12内には第2配線22が、それぞれ形成されている。第2配線用配線溝12の底面の少なくとも一部分は、絶縁膜(例えば、絶縁膜4及びエッチングストッパー膜5)によって、第2配線用配線溝12の上端に達しない高さで第1配線用配線溝11の底面よりもかさ上げされた、かさ上げ部15となっている。

(もっと読む)

半導体装置の製造方法

【課題】後工程のダメージがなく、優れた特性を有する強誘電体キャパシタを提供する。

【解決手段】実施形態に係わる半導体装置の製造方法は、半導体基板の上方に、誘電体膜を下部電極と上部電極とで挟んでなるキャパシタ(200,300,400)を形成する第1の工程と、O3とTEOSを原料としたCVD法により、キャパシタ(200,300,400)を覆う酸化膜(122,125,128)を形成する第2の工程と、ALD法により、酸化膜(122,125,128)上に保護膜としてのAl2O3(123,126,129)膜を形成する第3の工程とを備える。

(もっと読む)

誘電体膜の製造方法

【課題】比誘電率の低下を軽減しつつリーク電流値を低減し、スパッタ率の低下による堆積速度の減少を抑制し、かつ、面内均一性に優れた誘電体膜の製造方法を提供すること。

【解決手段】本発明の一実施形態に係る誘電体膜の製造方法は、基板上に、AlとSiとOを主成分とする金属酸化物である誘電体膜を形成する誘電体膜の製造方法であって、Al元素とSi元素のモル比率Si/(Si+Al)が0<(B/(A+B))≦0.1であり、非晶質構造を有する金属酸化物を形成する工程と、該非晶質構造を有する金属酸化物に1000℃以上のアニール処理を施し、結晶相を含む金属酸化物を形成する工程と、を備える。

(もっと読む)

21 - 40 / 272

[ Back to top ]