Fターム[5F058BF52]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜の形成法 (10,542) | 基板、処理対象等の直接変換 (1,722) | 加熱変換 (1,052)

Fターム[5F058BF52]の下位に属するFターム

Fターム[5F058BF52]に分類される特許

61 - 80 / 84

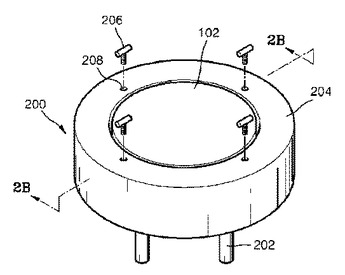

半導体粒子表面の珪素化合物被膜の形成方法及び光電変換装置並びに光発電装置

【課題】 多結晶シリコンのような半導体粒子を安定して高効率に結晶化するとともに高い結晶性を持った結晶シリコン粒子を低コストで製造することができる半導体粒子表面の珪素化合物被膜の形成方法を提供することである。

【解決手段】 半導体粒子101表面に珪素化合物被膜を形成する際に、半導体粒子101を載置した台板102を揺動または回転させることにより半導体粒子101と台板102との接触を低減させる半導体粒子101表面の珪素化合物被膜の形成方法を用いる。

(もっと読む)

急激な金属−絶縁体遷移を行うウェーハ、その熱処理装置及びこれを利用した熱処理方法

急激な金属−絶縁体遷移を行う基板と、基板上に電気伝導度及び熱伝導性の良好なペーストでコーティングまたは蒸着された金属層と、を備える金属−絶縁体遷移を行うウェーハである。これにより、ヒータや基板ホルダーに直接接着せず、直径の大きいウェーハを量産しうる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】酸化膜形成前の半導体層上にエッチング液の薬液成分が残留することを抑制できる半導体装置の製造方法を提供する。

【解決手段】第1の素子領域1a及び第2の素子領域1bそれぞれに第1の酸化膜3aを形成する工程と、第1の素子領域1aに位置する第1の酸化膜3aをマスク膜で覆う工程と、前記マスク膜をマスクとしたエッチングを行うことにより、第2の素子領域1bに位置する第1の酸化膜3aを除去する工程と、前記マスク膜をマスクとして酸化処理を行うことにより、第2の素子領域1bに、第1の酸化膜3aより薄い第2の酸化膜3cを形成する工程と、エッチング液を用いて前記マスク膜を除去する工程と、第2の酸化膜3cをエッチングにより除去する工程と、半導体層1を熱酸化することにより、第1の素子領域1aに位置する第1の酸化膜3aを厚くし、かつ第2の素子領域1bに位置する半導体層1に第3の酸化膜3dを形成する工程と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】3種類のゲート絶縁膜を有するMOS型半導体装置の製造において、トランジスタの特性異常等を防止できるようにする。

【解決手段】トレンチ分離領域105によって互いに分離されている入出力MOSFET活性領域、第1の内部MOSFET活性領域及び第2の内部MOSFET活性領域のそれぞれの上に、相対的に最も厚い第1のゲート酸化膜106を形成する。その後、第1の内部MOSFET活性領域上の第1のゲート酸化膜106を除去した後、第1の内部MOSFET活性領域上に、相対的に2番目に厚い第2のゲート酸化膜108を形成する。その後、第2の内部MOSFET活性領域上の第1のゲート酸化膜106を除去した後、第2の内部MOSFET活性領域上に、相対的に最も薄い第3のゲート酸化膜110を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】容易に製造することができ、小さな面積で高機能を付加することのできる、立体構造を有してなる半導体装置およびその製造方法を提供する。

【解決手段】シリコン(Si)半導体からなる基板1上に、部分的に基板1表面から浮き上がって形成された、立体構造のシリコン酸化膜2を有してなる半導体装置10とする。例えば、上記立体構造のシリコン酸化膜2上に抵抗素子や容量素子を形成し、これらを立体構造とすることで、平面構造の抵抗素子や容量素子に較べて、小さな面積で大きな抵抗値や容量値を付加させることができる。また、上記立体構造はシリコン酸化膜2が部分的にシリコン基板1表面から浮き上がって形成されたものであり、当該半導体装置10は、水素アニール処理によって容易に製造することができる。

(もっと読む)

電子デバイス材料の製造方法

【課題】電気的特性の優れた絶縁層や半導体層を備えた高品質のMOS型半導体等の電子デバイス材料の製造方法。

【解決手段】単結晶シリコンを主成分とする被処理基体上にCVD処理を施して絶縁膜を形成する工程と、前記被処理基体を、複数のスロットを有する平面アンテナ部材(SPA)を介して処理ガスにマイクロ波を照射することにより生成したプラズマに晒し、このプラズマを用いて前記絶縁膜を改質する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】全体の厚みを薄膜化しつつ高移動度を実現可能な半導体装置の製造方法を得ること。

【解決手段】半導体基板上に界面層として該半導体基板に接するシリコン酸窒化膜を形成する工程と、前記シリコン酸窒化膜上にゲート絶縁膜として前記シリコン酸窒化膜に接するハフニウムシリケート膜を形成し、前記シリコン酸窒化膜と前記ハフニウムシリケート膜との接触面において互いの構成元素を相互拡散させて前記シリコン酸窒化膜の膜厚を薄膜化する工程と、前記ハフニウムシリケート膜上にゲート電極を形成する工程と、を含む。

(もっと読む)

絶縁層が形成された太陽電池用基板およびその製造方法、ならびにそれを用いた太陽電池およびその製造方法

【課題】 ピンホール部の絶縁性が確保された絶縁層を含む太陽電池用基板およびその製造方法、ならびに、その基板を用いた太陽電池、および太陽電池の製造方法を提供する。

【解決手段】 (i)金属板11上に、ゾル・ゲル法で第1の絶縁材料からなる絶縁層12を形成する工程と、(ii)絶縁層12のピンホール部分に面する金属板11の表面に、第2の絶縁材料からなる絶縁部14を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 第1の活性領域には第1のゲート絶縁膜を、第2の活性領域には第2のゲート絶縁膜をそれぞれ分けて形成するに際して、エッチングによる表面損傷を回復させてトランジスタの十分な電気特性を得るとともに、設計自由度を拡張させて装置の更なる高集積化を可能とする。

【解決手段】 第2のゲート絶縁膜102の被加工端部102aが第1のゲート絶縁膜101の被加工端部101aと一部重畳するようにパターニングする(図2(a))。そして、第1及び第2のゲート絶縁膜101,102が上記のように一部重畳した状態で、表面回復処理を行う(図2(b))。

(もっと読む)

プラズマダメージ層の評価方法および半導体装置の製造方法

【課題】 シリコン基板の主面上に形成された非常に軽微なダメージのプラズマダメージ層であっても検出することのできる技術を提供する。

【解決手段】 シリコン基板上に例えば酸化シリコン膜からなる層間絶縁膜を形成し(ステップS1、S2)、この層間絶縁膜にコンタクトホールを形成するためプラズマエッチングする(ステップS3)。このプラズマエッチングはシリコン基板が露出するまで行われるため、シリコン基板の主面上にはプラズマダメージ層が形成される。このシリコン基板を酸化し(ステップS4)、シリコン基板上に形成された酸化膜の膜厚を測定(ステップS5)することで、プラズマダメージ層の検出、評価を行う。

(もっと読む)

半導体集積回路装置の製造方法

【課題】二酸化シリコン換算膜厚が5nm未満の極薄ゲート絶縁膜上にメタルゲート電極を形成したMISFETにおいて、メタルゲート電極を酸化させることなくゲート絶縁膜の欠陥を修復する。

【解決手段】単結晶シリコン基板1の主面上に形成した二酸化シリコン換算膜厚が5nm未満のゲート絶縁膜9A上にゲート電極材料であるW膜11Aを形成した後、水分/水素分圧比がW膜11Aを実質的に酸化せず、シリコンを酸化するような割合に設定された水分+水素混合ガス雰囲気中でシリコン基板1を熱処理することにより、W膜11A直下のゲート絶縁膜9Aの欠陥を修復する。

(もっと読む)

低誘電率を有するシリコン酸化物をベースとする材料を生成する方法

本発明は、低誘電率を有する材料(60)を生成する方法に関し、ヘリウム及びネオン以外の希ガスの注入で二酸化ケイ素中に空孔(66)を形成するステップを含む。本発明は、また、1016原子/cm2 より多い注入量でのヘリウム及びネオン以外の希ガスの注入により形成された空孔(66)を有し、低誘電率を有する二酸化ケイ素を含む領域が互いを隔てるところの複数の金属トラックを備える素子に関する。  (もっと読む)

(もっと読む)

半導体装置の製造方法、製造装置、シミュレーション方法、及びシミュレータ

【課題】 半導体装置製造プロセスを、テストピースなしに、所望の工程通り又は修正しながら進行することを可能とする半導体装置の製造方法を提供すること。

【解決手段】 複数の工程からなる半導体装置の製造方法において、前記複数の工程の少なくとも1つにおける実観測データを得る工程と、abinitio分子動力学プロセスシミュレータ又は経験的ポテンシャルを与えた分子動力学ミュレータにより、前記複数の工程の少なくとも1つにおける予測データを得る工程と、前記予測データと実観測データとを逐次、実時間で比較検定する工程と、前記比較検定により、製造工程因子の設定値と、前記実観測データから推測される前記複数の製造工程因子との間に有意差が認められた場合、前記製造工程因子を逐次実時間で修正処理する工程とを具備することを特徴とする。

(もっと読む)

半導体装置

【課題】同一半導体基板上に形成された複数種類のゲート絶縁膜の膜厚及び電気的特性のバラツキを防止する。

【解決手段】同一半導体基板1上に、互いに膜厚が異なる複数種類のゲート絶縁膜5,11をもって複数の素子形成領域3a,3bが形成されている。ゲート絶縁膜5,11上にポリシリコンからなるゲート電極13a,13bが形成されている。ゲート絶縁膜5,11は単層膜で形成されている。各々のゲート絶縁膜5,11上に形成されたゲート電極13a,13bは同一のポリシリコン膜から同時に形成されたものである。

(もっと読む)

トンネル酸化膜の窒化処理方法、不揮発性メモリ素子の製造方法および不揮発性メモリ素子、ならびにコンピュータプログラムおよび記録媒体

【課題】トンネル酸化膜の膜質のさらなる向上や、フローティングゲートにおけるデータ保持特性等のメモリ特性のさらなる向上を達成することができる不揮発性メモリ素子のトンネル酸化膜の窒化処理方法を提供すること。

【解決手段】不揮発性メモリ素子におけるトンネル酸化膜102に窒化処理を施すに際し、窒素ガスを含む処理ガスを用いたプラズマ処理により、トンネル酸化膜の表面部分に窒化領域103を形成する。

(もっと読む)

半導体装置と半導体装置の製造方法

ゲート絶縁膜として所望の特性を有するHf1−xAlx(0<x<0.3)の酸化膜を形成することのできる半導体装置の製造方法を提供する。

半導体装置の製造方法は、(a)反応室内でシリコン基板を加熱する工程と、(b)加熱したシリコン基板上に酸化シリコンより高い比誘電率を有し、Nを取り込んだHf1−xAlxO:N膜(0.1<x<0.3)を熱CVDで堆積する工程であって、原料ガスと窒化ガスと窒化促進ガスとを含む成膜ガスを前記シリコン基板の表面に供給する工程と、を含む。  (もっと読む)

(もっと読む)

半導体装置と半導体装置の製造方法

ゲート絶縁膜としてフラットバンド電圧の変化ΔVfbが小さなHf1xAlx(0<x<0.3)の酸化膜を形成することのできる半導体装置の製造方法を提供する。 半導体装置の製造方法は、(a)反応室内でシリコン基板を加熱する工程と、(b)前記加熱したシリコン基板上に酸化シリコンより高い比誘電率を有する高誘電率絶縁膜を熱CVDで堆積する工程であって、原料ガスと水素ガスとを含む成膜ガスを前記シリコン基板の表面に供給する工程と、を含む。  (もっと読む)

(もっと読む)

ゲート酸化膜の形成方法

【課題】 薄膜化されたゲート酸化膜の形成方法において、ラジカル酸化装置を用い、トランジスタの閾値電圧ばらつきを最小とする好適なゲート酸化膜形成方法を提供する。

【解決手段】 ラジカル酸化法を用いたゲート酸化膜の形成方法においては、シリコン界面における不純物の偏析を一定にするためOH種密度を均一にし、さらにOH種及び酸素種を含めた総酸化種密度を均一化させることによりトランジスタの閾値電圧ばらつきを最小にする。酸化膜厚の均一性のよい圧力より1〜2torr低い圧力範囲において、OH種密度ばらつきが最小となり、不純物偏析ばらつきを最小とすることでトランジスタの閾値電圧を均一にすることが出来る。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、微細な形状を有する半導体領域の形成方法を提供する。バラツキの少ない半導体装置の作製方法を提供する。また、少ない原料でコスト削減が可能であり、且つ歩留まりが高い半導体装置の作製方法を提供する。

【解決手段】 本発明は、半導体膜の一部にレーザ光を照射し、絶縁層を形成した後、該絶縁層をマスクとして半導体膜をエッチングして、所望の形状を有する半導体領域を形成した後、該半導体領域を用いる半導体装置を作製する。本発明では、公知のレジストを用いたフォトリソグラフィー工程を用いずとも、所定の場所に微細な形状を有する半導体領域を形成することが可能である。

(もっと読む)

半導体装置の製造方法

【課題】 p型ドーパントであるボロンの突き抜け防止のために、高誘電膜(High−k膜)中に入れる窒素が、High−k膜とシリコン基板との界面に達するのを防止する。

【解決手段】 シリコン基板400上のシリコン酸化膜411を酸化処理した後、その上にHigh−k膜412を形成する。このHigh−k膜412上にALD法などにより10Å以下の極薄のシリコン窒化膜413を形成する。その後、プラズマ活性化された窒素含有ガスによりシリコン窒化膜413を窒化処理してHigh−k膜412の表面を窒化する。

(もっと読む)

61 - 80 / 84

[ Back to top ]