Fターム[5F058BF52]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜の形成法 (10,542) | 基板、処理対象等の直接変換 (1,722) | 加熱変換 (1,052)

Fターム[5F058BF52]の下位に属するFターム

Fターム[5F058BF52]に分類される特許

21 - 40 / 84

半導体装置及びその製造方法

【課題】所望の仕事関数を得ると共にトランジスタの駆動力を劣化させない構造を有する半導体装置を提供する。

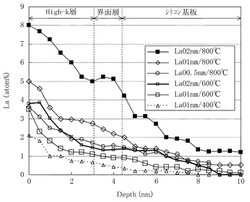

【解決手段】半導体装置は、半導体基板1と、半導体基板1の上に形成された界面層5と、界面層5の上に形成された高誘電率ゲート絶縁膜6と、高誘電率ゲート絶縁膜6上に形成されたゲート電極とを備える。高誘電率ゲート絶縁膜6はランタンを含有し、高誘電率ゲート絶縁膜6におけるゲート電極との界面に含まれているランタンの濃度は、高誘電率ゲート絶縁膜における界面層との界面に含まれているランタンの濃度よりも大きい。

(もっと読む)

酸化装置、酸化方法、面発光レーザ素子、面発光レーザアレイ、光走査装置、画像形成装置、光伝送モジュール及び光伝送システム

【課題】酸化距離のばらつきが小さい酸化装置を提供する。

【解決手段】水蒸気を発生させる水蒸気発生装置と、該水蒸気発生装置で発生した水蒸気を酸化温度近くまで加熱する水蒸気加熱装置5030と、該水蒸気加熱装置5030で加熱された水蒸気が供給され、該水蒸気の温度を維持するヒータを有する酸化反応器5040と、開閉可能な隔壁5060を介して酸化反応器5040と連結された準備室5050と、酸化対象物を加熱するヒータを有し、酸化対象物が載置されるテーブル装置と、該テーブル装置を駆動し、酸化開始時に酸化対象物を準備室5050から酸化反応器5040に移動させ、酸化終了後に酸化対象物を酸化反応器5040から準備室5050に移動させる駆動装置とを備えている。

(もっと読む)

半導体装置の製造方法、半導体装置、および電気光学装置

【課題】、ポリシリコン膜に含まれる結晶欠陥を電気的に略不活性化させた場合でも、その後の工程での処理温度が限定されることがなく、かつ、能動層とゲート絶縁層との間に良好な界面を形成することができる半導体装置の製造方法、半導体装置および電気光学装置を提供すること。

【解決手段】半導体装置10tの製造工程では、電界効果型トランジスタ30nの能動層となるシリコン膜1sを結晶化させた後、シリコン膜1sに酸素プラズマ照射OPを行う酸素プラズマ照射工程と、酸素プラズマ照射工程によりシリコン膜1sに形成された表面酸化物1rを除去する表面酸化物除去工程とを行う。その後、シリコン膜1sをパターニングする。

(もっと読む)

半導体装置の製造方法、熱酸化処理方法及び熱酸化処理装置

【課題】本発明は、熱酸化処理方法に関し、膜厚均一性の高いゲート酸化膜を形成することができる半導体装置の製造方法、熱酸化処理方法及び熱酸化処理装置を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、モニタウェハM1の裏面と第1の製品ウェハ#2の表面を対向させ、且つ第1の製品ウェハ#2の裏面と第2の製品ウェハ#3の表面を対向させ、且つモニタウェハM1、第1及び第2の製品ウェハ#2、#3それぞれの裏面にシリコン窒化膜23が形成された状態で熱酸化処理装置内に配置し、熱酸化処理装置によってモニタウェハM1、第1及び第2の製品ウェハ#2、#3それぞれの表面に熱酸化膜を形成する工程を具備することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】Cu配線中のMnの残留量を減らすことができる、半導体装置の製造方法を提供する。

【解決手段】第2バリア膜13の形成後に、SiH4を含むガスを用いたPECVD法により、Cu層20上にSiおよびOを含む絶縁材料からなる犠牲層21が積層される。犠牲層21にSiおよびOが含まれるので、犠牲層21の積層過程で、Cu層20と犠牲層21との界面にMnSiOからなる反応生成膜22が生じる。この反応生成膜22の生成にMnが使用されることにより、Cu層20に含まれるMnの量が減少する。よって、Cu層20からなる第2Cu配線中のMnの残留量を減らすことができる。

(もっと読む)

絶縁破壊寿命シミュレーション方法、シリコンウェーハ表面の品質評価方法およびプログラム

【課題】 絶縁体薄膜の信頼性評価において、絶縁破壊の確率過程にシリコンウェーハ表面の品質状態を数理統計的に組み込ませる。

【解決手段】 シリコンウェーハ上に形成した絶縁体薄膜をモンテカルロ法によりコンピュータシミュレーションする絶縁破壊寿命シミュレーション方法は、絶縁破壊の測定条件を設定するステップ、ウェーハ表面欠陥の分布および欠陥サイズを設定するステップ、絶縁体薄膜をセルにメッシュ分割し上記表面欠陥をセルにくり込むステップ、絶縁体薄膜の絶縁破壊に至る時間の基準尺度を算出するステップ、シリコンウェーハ上に設定する全キャパシタに亘りそれ等の絶縁体薄膜の絶縁破壊の確率過程をモンテカルロ法によりコンピュータシミュレーションするステップ、全キャパシタの絶縁破壊について統計処理するステップ、を有する。

(もっと読む)

半導体装置の製造方法

【課題】溝の側面に対する合金膜の付着性(サイドカバレッジ)を向上させることができる、半導体装置の製造方法を提供する。

【解決手段】合金膜18は、バイアススパッタ法により形成される。そして、そのバイアススパッタ法による合金膜18の形成時には、第2溝11およびビアホール12の内面に向けて飛散するスパッタ粒子のエネルギーにより、第2溝11およびビアホール12の底面に付着しているスパッタ粒子が弾き飛ばされ、その弾き飛ばされたスパッタ粒子が第2溝11およびビアホール12の側面に再付着(リスパッタ)するように、スパッタ粒子を加速するためのRFバイアスが設定される。

(もっと読む)

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

半導体装置及びその製造方法

【課題】メモリセルトランジスタ及びセレクトトランジスタともに良好な特性を有する優れた半導体装置を提供する。

【解決手段】半導体基板10上に設けられた第1の下層絶縁膜20aと、第1の下層絶縁膜上に設けられた第1の中間絶縁膜30aと、第1の中間絶縁膜上に設けられた第1の上層絶縁膜40aと、第1の上層絶縁膜上に設けられた第1のゲート電極50aと、を有するメモリセルトランジスタ100aと、半導体基板上に設けられた第2の下層絶縁膜20bと、第2の下層絶縁膜上に設けられた第2の中間絶縁膜32bと、第2の中間絶縁膜上に設けられた第2の上層絶縁膜40bと、第2の上層絶縁膜上に設けられた第2のゲート電極50bと、を有するセレクトトランジスタ100bと、を備え、第2の中間絶縁膜32bのトラップ密度は、第1の中間絶縁膜30aのトラップ密度よりも低い。

(もっと読む)

半導体装置の製造方法

【課題】 熱処理を行う際に、半導体基板の裏面側からの半導体構成原子の昇華を防止し得る半導体装置の製造方法及び半導体製造工程の管理方法を提供する。

【解決手段】 半導体基板10にゲート絶縁膜を形成する工程を有する半導体装置の製造方法であって、ゲート絶縁膜を形成する工程の前に、半導体基板の表面側及び裏面側を覆うように絶縁膜12を形成する工程と、半導体基板の表面側の絶縁膜をエッチング除去する工程と、半導体基板の裏面側に絶縁膜が存在している状態で、半導体基板を熱処理する工程とを有している。

(もっと読む)

絶縁膜の形成方法

【課題】高誘電率ゲート絶縁膜としての使用に適する高誘電率絶縁膜を良好な制御性をもって生産性良く形成する。

【解決手段】シリコン基体101の表層部を酸化してシリコン酸化膜102とする第1工程と、非酸化性雰囲気中においてシリコン酸化膜102の上に金属膜103を形成する第2工程と、非酸化性雰囲気中で金属膜103を希ガスプラズマに暴露することで、金属膜103を構成する金属原子をシリコン酸化膜102中に拡散させる第3工程と、金属原子が拡散したシリコン酸化膜102をラジカル酸化により酸化し、金属シリケート膜104を形成する第4の工程と、を備える。希ガスプラズマは金属膜103を構成する金属原子の原子量に最も近い原子量を有する希ガスを含む。

(もっと読む)

絶縁膜の形成方法

【課題】高誘電率ゲート絶縁膜としての使用に適する高誘電率絶縁膜を良好な制御性をもって生産性良く形成する。

【解決手段】シリコン基体101の表層部を酸化してシリコン酸化膜102とする第1工程と、非酸化性雰囲気中においてスパッタによりシリコン酸化膜102の上に金属膜103を形成する第2工程と、非酸化性雰囲気中での加熱を行うことで、金属膜103を構成する金属原子をシリコン酸化膜102中に拡散させる第3工程と、金属原子が拡散したシリコン酸化膜102をラジカル酸化により酸化し、金属原子とシリコン原子と酸素原子とを含む金属シリケート膜104を形成する第4工程とを備える。

(もっと読む)

ガス流分布が改善された熱反応器

本発明の実施形態は、熱処理中のガス分布を改善する装置および方法を提供する。本発明の一実施形態は、基板を処理する装置であって、処理空間を画定するチャンバ本体と、処理空間内に配置され、基板を支持して回転させる基板支持体と、チャンバ本体の入口に結合され、処理空間に第1のガス流を提供するガス入口アセンブリと、チャンバ本体の出口に結合された排出アセンブリとを含み、ガス入口アセンブリおよび排出アセンブリがチャンバ本体の両側に配置され、また排出アセンブリが、処理空間を拡張する排出空間を画定する装置を提供する。  (もっと読む)

(もっと読む)

半導体酸化工程の応力分布計算方法

【課題】酸化シミュレーションにおける応力分布計算の精度の劣化を抑えることができる半導体酸化工程の応力分布計算方法を提供する。

【解決手段】酸化種104の拡散方程式を解くことによりシリコン100の酸化に関する物理分布情報を取得し、半導体素子112の領域を等間隔で複数の補助メッシュ32に分割した補助メッシュ空間を設定し、物理分布情報を補助メッシュ32に設定して応力分布を計算し、応力分布を平均化した平均化応力分布を計算し、半導体素子112の領域を非等間隔で複数の実メッシュ34に分割した実メッシュ空間を設定し、補助メッシュ空間における平均化応力分布を実メッシュ空間における応力分布に変換し、変換後の応力分布に基づいて、半導体素子112の形状を更新する。

(もっと読む)

半導体装置

【課題】配線間におけるリーク電流の発生を防止することができる、半導体装置を提供する。

【解決手段】層間絶縁膜1は、SiO2からなる。層間絶縁膜1には、その上面から掘り下がった溝2a,2bが形成されている。この溝2a,2bには、CuMnからなる配線4a,4bが埋設されている。層間絶縁膜1および配線4a、4b上には、SiO2からなるバリア形成用膜5が積層されている。バリア形成用膜5上には、パッシベーション膜6が積層されている。また、配線4a,4bと層間絶縁膜1およびバリア形成用膜5との間には、MnSiOからなるバリア膜3a,3bが介在されている。このバリア膜3a,3bによって、配線4a,4bの全面が被覆されている。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】安定かつ良好な制御性をもって薄膜を形成する。

【解決手段】成膜装置40はウエハ2を処理する処理室41と、処理室41内に原料ガスを供給する原料ガス供給管56A、56Dと、処理室41内にオゾンガスを供給するオゾンガス供給管59Bとを備えており、処理室41内にオゾンガスを供給してウエハ2の表面にシリコン酸化膜を形成し、その後、原料ガスの供給とオゾンガスの供給とを連続して複数回繰り返すことで、シリコン酸化膜上に高誘電率膜を形成する。一つの処理室内で連続して界面層としてのシリコン酸化膜とハフニウムシリケート膜を形成できるので、効率的に極薄いシリコン酸化膜を界面にもつハフニウムシリケート膜を形成できる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜に形成されたダングリングボンドを効果的にキュアリングして向上した電気的特性を確保しうる半導体装置の製造方法を提供する。

【解決手段】基板100上にゲート構造物110が形成される。ゲート構造物110の形成された基板100に水素を含むガス雰囲気下で第1熱処理が行われる。基板100上に金属配線が形成される。これによって、ゲート絶縁膜パターン112のダングリングボンドがキュアリングされ、信頼性のある半導体装置が製造される。

(もっと読む)

半導体装置およびその製造方法

【課題】浮遊ゲート電極または制御ゲート電極の特性ばらつきを可及的に抑制し、トンネル絶縁膜の信頼性の低下を防止し、かつストレス誘起リーク電流を抑制することを可能にする。

【解決手段】第1導電型の半導体層を有する基板1と、半導体層に対向して設けられた一対の第2導電型のソース/ドレイン領域12と、ソース/ドレイン領域間の半導体層上に設けられた第1の絶縁膜14と、第1の絶縁膜上に設けられ、ソース/ドレイン領域が対向する方向に沿って亜粒界17が形成された単結晶の半導体を含む浮遊ゲート電極16と、浮遊ゲート電極上に設けられた第2の絶縁膜18と、第2の絶縁膜上に設けられた制御ゲート電極20と、を有するメモリセルと、を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極からのボロン漏れを抑制することができ、ゲート絶縁膜を薄膜化した場合でも、界面順位密度の増加及び膜中のプラスチャージの生成を抑制することが可能な半導体装置及びその製造方法を提供。

【解決手段】ゲート絶縁膜11の上面及び下面をフッ素原子によって終端した後、ゲート絶縁膜11の上面をエッチングすることにより、ゲート絶縁膜11の上面に新たなダングリングボンドを形成し、その新たなダングリングボンドを窒素原子によって終端させる。これにより、シリコン基板10と、シリコン基板10上に形成されたゲート絶縁膜11を有し、ゲート絶縁膜11は、上面のダングリングボンドがほぼ全体的に窒素原子で終端されており、シリコン基板10と接する下面のダングリングボンドがほぼ全体的にフッ素原子で終端された半導体装置を得る。

(もっと読む)

半導体集積回路装置

【課題】厚さが異なる2種類以上のゲート絶縁膜を有する半導体集積回路装置の信頼性を向上させることのできる技術を提供する。

【解決手段】半導体基板1の表面に形成された酸化シリコン膜6の上層に酸化シリコン膜7を形成し、次いで厚いゲート絶縁膜を形成する領域Aを覆ったフォトレジストパターン8をマスクとして、薄いゲート絶縁膜を形成する領域Bの酸化シリコン膜6,7を除去した後、フォトレジストパターン8および酸化シリコン膜7を除去し、続いて熱酸化処理を半導体基板1に施すことによって、厚さの異なるゲート絶縁膜を形成する。

(もっと読む)

21 - 40 / 84

[ Back to top ]