Fターム[5F058BF74]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜の形成法 (10,542) | 基板、処理対象等の直接変換 (1,722) | プラズマ処理 (498) | 窒化 (254)

Fターム[5F058BF74]に分類される特許

61 - 80 / 254

半導体装置の製造方法および基板処理装置

【課題】界面層および高誘電率絶縁膜下層部への窒素原子の導入を抑制することができる半導体装置の製造方法及び基板処理装置の提供。

【解決手段】MOSFETのゲートスタック形成工程は、ウエハ上に界面層を形成するステップと、界面層に第一ハフニウムシリケート膜を形成するステップと、第一ハフニウムシリケート膜にアニールを施すことで第一ハフニウムシリケート膜を緻密化もしくは結晶化するステップと、緻密化もしくは結晶化した第一ハフニウムシリケート膜上に第二ハフニウムシリケート膜を形成するステップと、第一ハフニウムシリケート膜および第二ハフニウムシリケート膜に対しプラズマ窒化を施すステップと、プラズマ窒化のプラズマダメージを回復する回復アニールステップと、を有する。窒素導入による移動度の劣化を抑制し、良好なMOSFET特性を得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】 高アスペクト比のトレンチ構造を有するポリシリコンに対し、プラズマを用いて均一な窒化処理を行なうことが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体基板上に、下部電極としてのポリシリコン膜102を形成する工程と、ポリシリコン膜102を窒化処理してシリコン窒化膜103を形成する窒化工程と、シリコン窒化膜103上に誘電体層104を形成する工程と、誘電体層104の上に、上部電極105を形成する工程と、を含む半導体装置の製造方法であって、上記窒化工程は、複数のスロットを有する平面アンテナにて処理室内にマイクロ波を導入して窒素含有プラズマを発生させるプラズマ処理装置により66.7Pa〜1333Paの処理圧力でポリシリコン膜102をプラズマ窒化処理する。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】半導体装置の製造方法に於いて、簡便な方法により、処理容器の内壁面をプラズマによりコーティングし、内壁面から酸素等の汚染原子が放出されることを抑止し、成膜品質を向上させる。

【解決手段】基板5を処理する処理容器1の内面を、プラズマ処理により反応ガス19でコーティング処理する工程と、前記処理容器内に基板を搬入する工程と、前記反応ガスを用いて基板をプラズマ処理する工程と、前記処理容器内から基板を搬出する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板との界面付近の窒素濃度の増加を抑制しつつ、逆側のゲート電極との界面付近の窒素濃度を高めたゲート絶縁膜を形成する。

【解決手段】窒素含有ゲート絶縁膜12を形成するステップが、シリコン単原子層を堆積するステップ及びシリコン単原子層を酸化するステップを順次に含み、半導体基板11上にシリコン酸化膜21を形成する酸化膜形成ステップと、シリコン酸化膜の表面部分21aを500℃未満の基板温度でプラズマ窒化法により窒化する窒化ステップと、シリコン単原子層を堆積するステップ及びシリコン単原子層を500℃未満の基板温度でプラズマ窒化法により窒化するステップを順次に含み、表面部分を窒化したシリコン酸化膜の表面にシリコン窒化膜22を形成する窒化膜形成ステップと、を有し、窒素含有ゲート絶縁膜とゲート電極13との界面での窒素濃度が、窒素含有ゲート絶縁膜と半導体基板との界面での窒素濃度よりも高い。

(もっと読む)

薄膜多層配線基板およびその製造方法

【課題】 剥離の発生の少ない薄膜多層配線基板とその製造方法を提案する。

【解決手段】 少なくとも一つの前記配線層が、下層の配線層上に形成された第一のSiO2薄膜と、前記第一のSiO2薄膜上に形成されたSiON薄膜と、前記SiON薄膜上に形成された第二のSiO2薄膜と、前記第二のSiO2薄膜に埋め込まれて形成された配線導体と、前記配線導体と接続しかつ前記第一のSiO2薄膜、前記SiON薄膜および前記第二のSiO2薄膜を貫通して前記下層の配線層の配線導体と電気的に接続するビア導体と、前記第二のSiO2薄膜上に形成されたSiN薄膜と、で構成されている。

(もっと読む)

成膜装置および成膜方法

【課題】ウエハ面内の膜厚均一性を高める装置と方法を提供する。

【解決手段】処理ガスをウエハ1に供給してウエハ1の上に膜をCVD法によって形成する成膜装置は、複数のウエハ1を互いに上下方向に離間して保持するボート2と、ウエハ1およびボート2を収容する処理室12と、ウエハ1を加熱するホットウオール形構造のヒータ14と、処理室12内に処理ガスを供給するガス供給管21と、処理室12内の雰囲気を排気する排気管16と、ウエハ1の処理中にウエハを回転させるためにボート2を回転させる回転軸19とを有する。

(もっと読む)

不揮発性半導体記憶装置のメモリセル

【課題】微細化を行っても、書き込み/消去特性、繰り返し特性、およびリテンション特性に優れたMONOS型メモリセルを提供する。

【解決手段】不揮発性半導体記憶装置のメモリセルは、MONOS型の構造をしており、電荷蓄積層が複数の絶縁物層から構成される。それらの絶縁膜の隣接する層間の伝導帯端エネルギーと価電子帯端エネルギーの関係は、トンネル絶縁膜からブロック絶縁膜に向かって、次第に大きくなるか、または、次第に小さくなるかのいずれかである。さらに、ブロック絶縁膜の比誘電率をεrとすれば、電荷蓄積層とブロック絶縁膜の間のエネルギー障壁は、電子に対して4.5εr-2/3(eV)以上、3.8eV以下、正孔に対して4.0εr-2/3(eV)以上、3.8eV以下である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造歩留まりを向上させる。

【解決手段】

半導体基板1の主面にゲート絶縁膜用の絶縁膜を形成する。それから、プラズマ処理装置51の処理室51a内で、半導体基板1の主面のゲート絶縁膜用の絶縁膜をプラズマ窒化する。その後、プラズマ処理装置51から半導体基板1をフープ31内に移送し、フープ31をベイステーションBSに移動させてそこで待機させて半導体基板1を保管する。ベイステーションBSに待機している間、半導体基板1を保管しているフープ31内に、フープ31に設けられた第1の呼吸口から窒素ガスを供給し、フープ31に設けられた第2の呼吸口からフープ31内の窒素ガスを排出する。その後、フープ31を熱処理装置52に移動させて、半導体基板1を熱処理装置52の処理室内に搬入して熱処理する。

(もっと読む)

電子デバイス材料の製造方法

【課題】極めて薄い膜厚を有する絶縁膜としてSiO2膜およびSiON膜を用い、電極としてポリシリコン、アモルファスシリコン、SiGeを用いた良好な電気特性を有する電子デバイス(例えば高性能MOS型半導体装置)構造の製造方法を提供する。

【解決手段】酸素、および希ガスを含む処理ガスの存在下で、ウエハW上に平面アンテナ部材SPAを介してマイクロ波を照射することにより、酸素と希ガスとを含むプラズマ(ないし窒素と希ガスとを含むプラズマ、または窒素と希ガスと水素を含むプラズマ)を形成する。このプラズマを用いて前記ウエハ表面に酸化膜2(ないし酸窒化膜2a)を形成し、必要に応じてポリシリコン等の電極13を形成して電子デバイス構造を形成する。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】膜中の炭素、水素、窒素、塩素等の不純物濃度が極めて低い絶縁膜を低温で形成することができる半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】基板を収容した処理容器内に所定元素を含む原料ガスを供給することで、基板上に所定元素含有層を形成する工程と、処理容器内に窒素を含むガスを活性化して供給することで、所定元素含有層を窒化層に改質する工程と、処理容器内に酸素を含むガスを活性化して供給することで、窒化層を酸化層または酸窒化層に改質する工程と、を1サイクルとして、このサイクルを少なくとも1回以上行う。

(もっと読む)

フラッシュメモリ素子のトンネル絶縁膜形成方法

【課題】800℃以上の高温のプラズマ窒化処理工程を含んでトンネル絶縁膜を形成することにより、トラップサイト(trap site)を減少させ、シリコン酸化窒化膜(SiON)の形成によってホウ素浸透を抑制して漏れ電流および絶縁破壊電圧特性などを改善することが可能なフラッシュメモリ素子のトンネル絶縁膜形成方法の提供。

【解決手段】半導体基板上に酸化膜を形成する段階と、800〜900℃のプラズマ窒化処理工程によって前記酸化膜の表面に窒素含有絶縁膜を形成する段階と、前記半導体基板と前記窒素含有絶縁膜の形成された前記酸化膜との界面に窒素蓄積層を形成する段階とを含む、フラッシュメモリ素子のトンネル絶縁膜形成方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性が高い半導体装置を製造できる半導体装置の製造方法を提供すること。

【解決手段】半導体装置1の製造方法は、基板11上に、シリコン酸化膜12を形成する工程と、シリコン酸化膜12に対して窒素を導入してシリコン酸窒化膜13を形成する工程と、シリコン酸窒化膜13上にZr、Hfの少なくともいずれかを含む絶縁膜14を形成する工程とを含む。基板11上にシリコン酸化膜12を形成する前記工程では、基板11上にシリコン酸化膜12を成膜した後、1050℃以上、1100℃以下でシリコン酸化膜12を熱処理する。

(もっと読む)

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

高誘電率膜を製造するための方法

超高純度ハフニウム含有有機金属化合物を使用して高K(誘電率)膜を作るためのプロセスが、開示される。高純度ハフニウム含有有機金属化合物で作られた高K膜を組み込むデバイスもまた、述べられる。  (もっと読む)

(もっと読む)

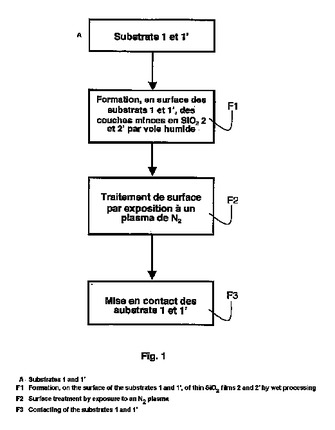

直接接合方法における窒素プラズマ表面処理

表面上にシリコン薄膜または酸化シリコン薄膜を各々が有する2つのウェハが、少なくとも1つのウェハの薄膜に、5nm未満の厚さを有する薄い酸窒化シリコン表面膜を形成する表面処理を施すことによって接合される。薄膜は、誘導結合プラズマ源によって発生した窒素系プラズマによって形成される。加えて、プラズマと前記ウェハを支持する基板ホルダとの間の電位差は、表面処理中、50V未満、有益には、15V未満、好ましくは、0である。これにより、接触ステップ後に実行される任意の熱処理の温度にかかわらず、欠陥がない接合界面を得ることができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 各種半導体装置の製造過程で、プラズマ窒化処理によって形成された窒素含有層を不必要な部位に残存させない半導体装置の製造方法を提供する。

【解決手段】 プラズマ窒化処理工程の後に、選択エッチング処理工程を設け、電極層107に形成された窒化珪素膜109を残しつつ、素子分離膜103および絶縁膜105の表面に形成された窒化酸化珪素膜111を除去する。選択エッチング工程により、素子分離膜103および絶縁膜105の表面に形成された窒化酸化珪素膜111が除去される。

(もっと読む)

半導体装置のゲート酸化膜上に窒化珪素層を形成し、窒化物層を熱処理する方法

【課題】従来技術の問題の少なくとも一つを解決する、ゲート酸化膜上に窒化珪素膜を形成する方法を提供する。

【解決手段】半導体装置におけるゲート構造の形成の一部として、ゲート酸化膜上に窒化珪素膜を形成する方法であって、窒化処理プロセスにより、半導体基板のゲート酸化膜の上部に、窒化珪素の層を形成するステップと、熱処理チャンバ内で、前記半導体基板を加熱するステップと、前記熱処理チャンバ内で、前記半導体基板をN2に暴露するステップと、前記熱処理チャンバ内で、前記半導体基板をN2およびN2Oの混合物に暴露するステップと、を有する方法。

(もっと読む)

半導体装置およびその製造方法

【課題】多値化を実現するのに十分なメモリーウインドウと電荷保持特性を両立できる半導体装置を提供すること。

【解決手段】半導体装置は、半導体基板101と、半導体基板101上に設けられたトンネル絶縁膜103と、トンネル絶縁膜103上に設けられ、第1および第2の電荷蓄積層104,105を含む電荷蓄積層と、電荷蓄積層上に設けられたブロック絶縁膜106と、ブロック絶縁膜106上に設けられた制御ゲート電極107とを備え、電荷蓄積層において、第2の電荷蓄積層105はブロック絶縁膜106側に最も近い側に設けられ、第1の電荷蓄積層104はトンネル絶縁膜103と第2の電荷蓄積層105の間に設けられ、第2の電荷蓄積層105は第1の電荷蓄積層104よりもトラップ密度が高く、第2の電荷蓄積層105は第1の電荷蓄積層104よりもバンドギャップが小さく、第2の電荷蓄積層105は第1の電荷蓄積層104、シリコン窒化膜よりも誘電率が高い。

(もっと読む)

半導体装置の製造方法

【課題】半導体層と絶縁層との間の界面特性である半導体層のキャリヤ移動度の低下を防止した半導体装置とその製造方法を提供する。

【解決手段】活性多結晶シリコンからなる半導体層12と、酸化ケイ素からなる絶縁層6との間に窒化ケイ素からなる界面層5を設けている。窒化ケイ素中の窒素元素が活性多結晶シリコン膜からなる半導体層12中に拡散し、この活性多結晶シリコン膜中の格子歪みを補償し、半導体層12と絶縁層6との所望の界面特性を満たす。

(もっと読む)

半導体装置及びその製造方法

【課題】EOTが小さく、界面準位密度の増加が抑制されたゲート絶縁膜を備え、微細化されてもリーク電流が抑制され、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、第1の領域102上に、第1の酸化膜203を形成する工程(a)と、半導体基板101にプラズマ窒化処理を行って、第1の酸化膜202に窒素を導入して第1のゲート絶縁膜203を形成する工程(b)と、半導体基板101に酸化性雰囲気下で熱処理を行って、第1のゲート絶縁膜203を酸化する工程(c)と、半導体基板101にプラズマ窒化処理を行って、第1のゲート絶縁膜203にさらに窒素を導入する工程(d)と、半導体基板101に酸素雰囲気下で熱処理を行って、第1のゲート絶縁膜203を酸化する工程(e)とを備えている。工程(b)で、半導体基板101は直接窒化されない。

(もっと読む)

61 - 80 / 254

[ Back to top ]