Fターム[5F058BH15]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜形成後の処理 (2,470) | イオン注入(後処理) (35)

Fターム[5F058BH15]に分類される特許

1 - 20 / 35

半導体装置の製造方法

【課題】半導体基板等にダメージを与えることなくゲート絶縁膜を形成する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に誘電体膜を形成する成膜工程と、前記誘電体膜を熱処理する熱処理工程と、前記誘電体膜上の一部に電極を形成する電極形成工程と、前記電極の形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、前記照射工程の後、ウェットエッチングにより、前記イオン化したガスクラスターの照射された領域における前記誘電体膜を除去するエッチング工程と、を有することを特徴とする半導体装置の製造方法を提供することにより上記課題を解決する。

(もっと読む)

半導体装置及び半導体基板の重水素処理装置

【課題】界面準位密度のゲート酸化膜/半導体界面が形成された半導体装置、および作製方法の提供。

【解決手段】半導体基板とゲート絶縁膜、層間絶縁膜、配線層、保護絶縁膜等の半導体装置に形成される膜又は層の界面近傍での重水素元素濃度が1x1019cm-3以上であることを特徴とする金属−絶縁膜−半導体(MIS)構造を有する半導体装置とする。シリコンカーバイド領域を含む半導体基板上に形成された金属-絶縁膜(あるいは酸化膜)-半導体(MISあるいはMOS)構造を有する半導体装置(電界効果型トランジスタ(MISあるいはMOSFET))に対して、高温に加熱された熱触媒体表面での重水素を含んだガスの熱触媒作用によって生成された活性化した重水素を用いることにより、600°C以下の低温においてゲート絶縁膜/シリコンカーバイド半導体界面近傍に存在するダングリングボンドの重水素終端を図る。

(もっと読む)

半導体装置の製造方法

【課題】溝部を絶縁膜で埋設する際に、溝部のアスペクト比が大きい場合であっても、内部にボイドを残存させることなく、溝部内に絶縁膜を充填する。これにより微細化した半導体装置の製造を容易に行うことを可能とする。

【解決手段】隣り合う凸部の間に形成される溝部の上端部においてオーバーハング形状を有すると共に、溝部の上部にボイドを有するように溝部内に溝部用絶縁膜を形成する。凸部の高さ方向に対して斜め方向から、溝部用絶縁膜に不純物をイオン注入することにより、溝部内に形成された溝部用絶縁膜の一部に不純物をドープする。溝部用絶縁膜の不純物がドープされた部分を除去した後、溝部内に溝部用絶縁膜を充填する。

(もっと読む)

半導体装置及びその製造方法

【課題】 膜ストレス低減を図った無機SOG膜を有した半導体装置及びその製造方法を提供する。

【解決手段】 本発明の半導体装置は、半導体基板1上に形成された下層配線3と、前記下層配線3上及び下層配線3間に形成され、不純物がイオン注入されることで圧縮応力を示す無機SOG膜5aと、前記無機SOG膜5aを含む層間絶縁膜7に形成されたコンタクトホールを介して前記下層配線に接続する上層配線とを具備することを特徴とする。

(もっと読む)

基板処理装置

【課題】ウエハホルダによるウエハのスリップや反り等の弊害の発生を防止する。

【解決手段】ウエハ1の下面に面接触してウエハ1を保持するウエハホルダ70をボート60に多数段装着しておき、多数段のウエハホルダ70にウエハ1をそれぞれチャージした状態で、処理室内にボートローディングし、ウエハ1のアニール処理後にボートアンローディングする。ボート60の多数段のウエハホルダ70からウエハ1をディスチャージする際に、ボート60の最上段領域Uのウエハホルダ70からウエハ1Aをディスチャージし、その後に、最下段領域Bに向かってウエハ1をディスチャージして行く。取り出そうとしているウエハ1から落下した異物は下側のウエハ1に付着するので、異物が下側のウエハホルダに付着するのは防止でき、ウエハホルダに付着した異物による次回のウエハ1でのスリップや反り等の弊害の発生を未然に防止できる。

(もっと読む)

半導体基板、半導体装置及び半導体装置の製造方法

【課題】半導体層の界面に生じるダングリングボンドをフッ素で終端することで、界面準位を低減することができ、また、低熱履歴のプロセスでも活性領域のみへ効率よくフッ素を導入することができる半導体基板を提供する。

【解決手段】フッ素拡散防止膜6と該フッ素拡散防止膜6上に形成されたフッ素を含有するシリコン酸化膜7からなる絶縁層9と、前記絶縁層9上に形成された半導体層8と、を含み、前記半導体層8とフッ素を含有する前記シリコン酸化膜7とが接触していることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】低コストかつ作業効率の高い半導体装置の製造方法を提供する。

【解決手段】シリコン基板110の上に回路パターンを形成し、回路パターンが形成されたシリコン基板110の上に層間絶縁膜140を形成する。層間絶縁膜140に対して第1の加速電圧でイオン注入を行い第1イオン層310を形成する。続いて第1の加速電圧より高い第2の加速電圧でイオン注入を行い第2イオン層320を形成する。その後、層間絶縁膜140を、第2イオン層320の波形上端部320Puが表出するまで研磨する。

(もっと読む)

SOI基板の作製方法

【課題】単結晶半導体層とベース基板との密着性を向上させ、貼り合わせ不良を低減することを目的の一とする。

【解決手段】半導体基板の表面にラジカル処理を行うことにより、半導体基板に第1の絶縁膜を形成し、第1の絶縁膜を介して半導体基板に加速されたイオンを照射することにより、半導体基板に脆化領域を形成し、第1の絶縁膜上に第2の絶縁膜を形成し、第2の絶縁膜の表面とベース基板の表面とを接合させた後に熱処理を行い、脆化領域において分離することにより、ベース基板上に第1及び第2の絶縁膜を介して半導体層を形成し、半導体層にエッチング処理を行い、エッチング処理が行われた半導体層にレーザビームを照射する。

(もっと読む)

半導体装置およびその製造方法、並びにMOS型電界効果トランジスタおよびその製造方法

【課題】III族窒化物系化合物半導体の表面上に酸化物を備えた半導体装置であって、上記III族窒化物系化合物半導体と上記酸化物との間の界面の界面準位密度を小さくでき、移動度を高くできるものを提供すること。

【解決手段】本発明の半導体装置では、III族窒化物系化合物半導体3の表面上に、Alを組成に含みスピネル構造をもつ酸化物4が形成されている。III族窒化物系化合物半導体3は、例えばGaNからなる。酸化物4は、例えばMgAl2O4、MnAl2O4、CoAl2O4、NiAl2O4からなる。

(もっと読む)

ダメージ回復処理の処理条件検査方法および処理条件最適化方法、ダメージ回復処理システム、記憶媒体

【課題】ダメージ回復処理単独でのプロセス確認を行うことができ、プロセス条件のずれを高感度で検出することができるダメージ回復処理の処理条件検査方法を提供すること。

【解決手段】エッチングおよびアッシングによりダメージを受けたLow−k膜に対して処理ガスによりOH基部分を改質するダメージ回復処理の処理条件検査方法は、OH基含有フォトレジスト膜が形成されたウエハを準備する工程と、そのフォトレジスト膜の初期膜厚を測定する工程と、初期膜厚測定後の基板にダメージ回復処理としてのシリル化処理を施す工程と、シリル化処理後のフォトレジスト膜の膜厚を測定する工程と、シリル化処理前後のフォトレジスト膜の膜厚差を求める工程と、その膜厚差に基づいてシリル化処理の処理条件の適否を判断する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の層間絶縁膜として用いられる有機SOG膜にコンタクトを形成する際のポイズンドビアの発生を抑制する。

【解決手段】半導体基板42上に配置した複数の下層配線46とその間隙47とを覆って、有機SOG膜を塗布し平坦化する。有機SOG膜をイオン注入により改質し、コンタクトホール56より深い位置まで改質SOG膜52に変える。特に、下層配線46の上からずれて形成されるコンタクトホール56bは、下層配線46の上面より低い位置まで到達する。改質SOG膜52は、このコンタクトホール56bが到達する深さより深い位置まで形成される。この改質SOG膜52の形成後、コンタクトホール56が形成される。コンタクトホール56の内部には、未改質の有機SOG膜50が現れず、プラグ60を埋め込む際にポイズンドビアとなることが防止される。

(もっと読む)

多層相互接続のための波形界面を有するデバイス(多層相互接続のための波形界面)

【課題】 相互接続積層物内の誘電層間にナノスケール波形界面を有するデバイス構造を提供する。

【解決手段】 相互接続積層物においてナノメートル・スケール波形界面を有する界面を含む誘電複合構造は、接着強度および界面破壊靭性の向上をもたらす。また、波形接着促進物層(114)を更に含んで固有の界面接着を更に向上させる複合構造も記載する。また、自己アセンブリング・ポリマー系およびパターン転送プロセスを用いてこれらの構造を可能とするための、ナノメートル・スケール波形界面を形成するための方法も記載する。

(もっと読む)

半導体装置及びその製造方法

【課題】 n型FET及びp型FETのドレイン電流の増加(電流駆動能力の向上)を図る。

【解決手段】 半導体基板に形成されたn型及びp型FETを有する半導体装置の製造であって、前記p型FETのゲート電極と前記半導体基板の素子分離領域との間の半導体領域を絶縁膜で覆った状態で、前記n型及びp型FET上にこれらのゲート電極を覆うようにして、前記n型FETのチャネル形成領域に引っ張り応力を発生させる第1の絶縁膜を形成する(a)工程と、エッチング処理を施して、前記p型FET上の前記第1の絶縁膜を選択的に除去する(b)工程と、前記n型及びp型FET上にこれらのゲート電極を覆うようにして、前記p型FETのチャネル形成領域に圧縮応力を発生させる第2の絶縁膜を形成する(c)工程と、前記n型FET上の前記第2の絶縁膜を選択的に除去する(d)工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極からのボロン漏れを抑制することができ、ゲート絶縁膜を薄膜化した場合でも、界面順位密度の増加及び膜中のプラスチャージの生成を抑制することが可能な半導体装置及びその製造方法を提供。

【解決手段】ゲート絶縁膜11の上面及び下面をフッ素原子によって終端した後、ゲート絶縁膜11の上面をエッチングすることにより、ゲート絶縁膜11の上面に新たなダングリングボンドを形成し、その新たなダングリングボンドを窒素原子によって終端させる。これにより、シリコン基板10と、シリコン基板10上に形成されたゲート絶縁膜11を有し、ゲート絶縁膜11は、上面のダングリングボンドがほぼ全体的に窒素原子で終端されており、シリコン基板10と接する下面のダングリングボンドがほぼ全体的にフッ素原子で終端された半導体装置を得る。

(もっと読む)

半導体装置とその製造方法

【課題】新規な特徴を有する半導体装置とその製造方法を提供すること。

【解決手段】シリコン基板10の上方に第1絶縁膜25を形成する工程と、第1絶縁膜25の所定の深さに不純物をイオン注入することにより、第1絶縁膜25に不純物層22を形成する工程と、不純物層22を形成した後、第1絶縁膜をアニールすることにより、不純物層22をバリア絶縁膜23に改質する工程とを有する半導体装置の製造方法による。

(もっと読む)

埋込み層に低抵抗コンタクトを形成する打込み領域を含んだ半導体デバイスの製作方法および関連したデバイス

半導体デバイスを製作する方法は、第1のドーパント濃度を有する第1の伝導型の第1の半導体層を形成すること、および第1の半導体層上に第2の半導体層を形成することを含む。第2の半導体層は、第1のドーパント濃度よりも低い第2のドーパント濃度を有する。第2の半導体層を貫通して延びて第1の半導体層に接触する第1の伝導型の打込み領域を形成するように、第2の半導体層中にイオンが打ち込まれる。第1の電極が第2の半導体層の打込み領域上に形成され、第2の電極が、第2の半導体層の非打込み領域上に形成される。関連したデバイスも述べられる。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】ゲート絶縁膜のリーク電流の増加を抑制することができる半導体装置を得ること。

【解決手段】シリコン基板1上にSiON膜12−1aを形成する工程と、SiON膜12−1a上にハフニウムと酸素とが結合したハフニウムオキサイドを含むハフニウムオキサイド膜12−2aを形成する工程と、ハフニウムオキサイド膜12−2a中にハフニウムをイオン注入する工程と、ハフニウムをイオン注入したハフニウムオキサイド膜12−2aをアニール処理して活性化させる工程と、ハフニウムオキサイド膜12−2a上にゲート電極となるPt膜を形成する工程と、Pt膜、ハフニウムオキサイド膜12−2a、SiON膜12−1aを所定の形状にパターニングする工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】膜特性が良好で窒化シリコン膜のリーク電流をさらに低減することを可能とする。

【解決手段】窒素原子を含むガスをプラズマによって活性化し、この活性化された窒素原子を含むガスによりシリコン基板100表面を窒化処理することにより、シリコン基板100表面に窒化シリコン膜を形成する半導体装置の製造方法において、窒化処理時のシリコン基板100の温度を600℃以上とし、シリコン基板100表面に厚さ4.0nm以上の窒化シリコン膜を形成する。

(もっと読む)

低エネルギープラズマシステムを用いた高誘電率トランジスタゲートを製造するための方法及び装置

本発明は、一般的には、基板上に高品質誘電体ゲート層を形成するように適合されている方法及び装置を提供する。実施形態は、標準窒化プロセスの代わりに金属プラズマ処理プロセスを用いて、基板上に高誘電率層を形成する方法を企図するものである。実施形態は、更に、二酸化シリコンのようなゲート誘電体層に対するイオン衝撃損傷を減少させるとともに金属原子の下に横たわるシリコンへの混入を避けるために比較的低エネルギーの金属イオンを“注入”するように適合された装置を企図するものである。一般に、プロセスには、高k誘電体を形成するステップと、次に、堆積された物質を処理して、ゲート電極と高k誘電物質との間の良好な接合部を形成するステップとを含む。実施形態は、また、高k誘電物質を形成し、高k誘電物質の表面を終了させ、望ましい後処理ステップを行い、ゲート層を形成するように適合されているクラスタツールを提供するものである。 (もっと読む)

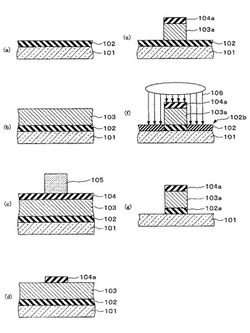

半導体装置の製造方法

【課題】シリサイド形成領域の隣接するゲート電極の間隔が狭い場合でも、不純物拡散層の接合リークを増大させずに、シリサイド領域と非シリサイド領域の双方に素子を備えた半導体装置を製造する。

【解決手段】シリサイド領域Rsiliおよび非シリサイド領域Rnonに、複数のゲート電極103および各ゲート電極103から露出する半導体基板101に拡散層104を形成する拡散層形成工程(a)と、半導体基板101上に第1絶縁膜107を形成する第1絶縁膜形成工程(b)と、非シリサイド領域Rnonの第1絶縁膜107を、不純物を添加して、第1絶縁膜107よりもエッチングレートが遅い第2絶縁膜107bを形成する第2絶縁膜形成工程(c)と、異方性エッチングにより第1絶縁膜107を後退させた(d)後に、ウェットエッチングによりシリサイド領域Rsili上に残留する第1絶縁膜107aを除去する工程を備える。

(もっと読む)

1 - 20 / 35

[ Back to top ]