Fターム[5F064BB37]の内容

ICの設計・製造(配線設計等) (42,086) | ICの機能 (7,082) | スイッチング (339)

Fターム[5F064BB37]に分類される特許

1 - 20 / 339

半導体集積回路

半導体集積回路

【課題】回路規模を低減しつつ任意の論理を実現可能な半導体集積回路を提供する。

【解決手段】実施形態の半導体集積回路は、第1論理ブロックを少なくとも1つ含む第1回路群と、第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、入力データを第1論理ブロックまたは第2論理ブロックへ入力する機能、および、第1論理ブロックまたは第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部とを含む。第1回路群は、第1スイッチブロックと、第1電源制御回路とを有する。第1電源制御回路は、第1回路群に含まれる第1論理ブロックおよび第1スイッチブロックに対する電力の供給および停止を共通に制御する。第2回路群は、第2スイッチブロックと第2電源制御回路とを有する。第2電源制御回路は、第2回路群に含まれる論理ブロックおよび第2スイッチブロックに対する電力の供給および停止を共通に制御する。

(もっと読む)

半導体集積回路およびそれを用いた光センサ機器

【課題】修正前の特性値がその特性値の出現頻度分布における平均値±2×(標準偏差)の範囲に入る製造品に対するヒューズ溶断本数を少なくする。

【解決手段】素子アレイ14には抵抗アレイを設け、特性値の分布の平均値を素子アレイ14で得られる合成抵抗値の中央値に対応付け、トリミング情報生成回路12における上記中央値より大きい合成抵抗値に対応するトリミング情報の配列を、10進数で「15」〜「8」の降順に、上記中央値以下の合成抵抗値に対応するトリミング情報の配列を、10進数で「0」〜「7」の昇順に設定する。変換回路13は、トリミング情報生成回路12からのトリミング情報を変換して、素子アレイ14の抵抗アレイから各合成抵抗値を得るためにオフする抵抗を選択する素子選択情報を生成する。こうして、上記分布における「平均値±2σ」の範囲内に対応付けられトリミング情報を生成する場合のヒューズ溶断数を大幅に削減する。

(もっと読む)

半導体集積回路の製造方法

【課題】常時動作領域と電源遮断可能領域とが混在する半導体集積回路を提供する。

【解決手段】半導体基板に設けられ、複数の基本セル(10)の配置が可能なセル配置領域と、空間的に前記セル配置領域と重なって設けられた基本電源配線(11)と、前記基本電源配線(11)から前記セル配置領域への電源供給を停止するスイッチセル(6)と、前記スイッチセル(6)に隣接して前記セル配置領域に配置され、前記スイッチセル(6)が前記セル配置領域への電源供給を停止した場合においても、前記スイッチセル(6)から電源供給を受ける常時動作セル(5)とを具備する。

(もっと読む)

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

不揮発性プログラマブルロジックスイッチ

【課題】メモリの選択的な書き込みを行う際のパストランジスタのゲート絶縁膜の破壊を防ぐとともにパストランジスタのゲート絶縁膜を薄くすることを可能にし、かつメモリの微細化によって書き込み効率が損なわれない不揮発性プログラマブルロジックスイッチを提供する。

【解決手段】第1端子と、第2端子と、メモリ状態を制御する制御信号を受ける第3端子とを有する第1メモリと、ソース/ドレインの一方が第2端子に接続される第1トランジスタと、第1トランジスタのソース/ドレインの他方にゲートが接続される第2トランジスタとを備えた、第1セルおよび第2セルを有する。第1セルの第1メモリの第3端子と、第2セルの第1メモリの第3端子は共通に接続され、第1セルに書き込みを行う場合、第3端子が書き込み電源に接続され、第1セルの第1端子は接地電源に接続され、第2メモリの第1端子は書き込み防止電源に接続される。

(もっと読む)

半導体集積回路

【課題】設計する回路の中で電流の多く流れる信号線を容易に見つけ出すことができ、容

易にその部分の電流を測定できるスタンダードセルを提供することを課題とする。

【解決手段】電流検出用テストパッドを少なくとも2つ有するスタンダードセルを自動レ

イアウトで配置する。そして、2つのテストパッド間を接続する配線を切断することで、

該2つのテストパッドを電流測定用テストパッドとして利用する。なお、スタンダードセ

ル内の2つのテストパッド間は、過電流が流れることにより電流の流れる経路が遮断され

る配線によって接続される構成としてもよい。また、2つのテストパッド間をつなぐ配線

部にメモリ又はアナログスイッチを設ける構成としてもよい。

(もっと読む)

再構成可能な集積回路ユニットを備えた論理回路及びその論路回路のエラー修正方法

【課題】エラー箇所の特定を実施する際に、システムを停止しないでエラー発生前の高信頼性までシステム性能を復帰させる。

【解決手段】同一動作を行う複数個の再構成可能な集積回路ユニットを備え、複数の該集積回路ユニットのそれぞれに複数のバンクを有する論理回路において、入力されたデータを、複数個の前記集積回路ユニットの各バンクに振り分けて入力する入力データ制御部と、複数個の集積回路ユニットの各バンクから出力されるデータを比較して、データ間の不一致を検出するエラー解析部と、エラー解析部から、データ間の不一致の通知を受けた場合に、複数個の集積回路ユニットの該当するバンクの再構成を行う構成情報制御部と、を備える。

(もっと読む)

半導体装置

【課題】少しの設計方法の変更で設計できる、一層低消費電力化した半導体装置の実現。

【解決手段】複数の電源供給領域23と、複数の電源供給領域に供給する電源の電圧を切り替える複数の電源切替ユニットSWA,SWBと、を有し、複数の電源供給領域に含まれる回路要素を組み合わせて少なくとも1つの機能ブロックが形成され、少なくとも1つの機能ブロックは、内部に異なる電圧で動作する回路要素を含む半導体装置。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において消費電力を低減するとともに、ノイズの発生を低減する。

【解決手段】半導体集積回路は、複数のDFFを有し、その少なくとも1つが冗長回路とされる。半導体集積回路が通常動作モードである際に、ANDゲート1によって冗長回路であるDFF3−3に印加されるクロック信号を停止する。冗長回路へのクロック信号が停止されると、当該冗長回路においてクロック信号が停止された状態における冗長回路のドレイン−グランド間容量よりもその容量を増加させる。

(もっと読む)

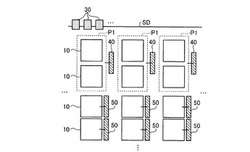

半導体集積回路

【課題】電源ノイズを抑制する。

【解決手段】電源電圧Vddまたは基準電圧Vssが印加される主配線(第1基準電圧幹線VSS1)と、複数の副配線(基準電圧枝線VSSB)と、複数の基準電圧枝線VSSBに接続されている複数の回路セル(不図示)と、入力される制御信号に応じて、複数の基準電圧枝線VSSBのうち、所定の回路セルが接続されている基準電圧枝線VSSBと第1基準電圧幹線VSS1との接続および遮断を制御する電源スイッチセルSW1,SW2,…と、複数の基準電圧枝線VSSBを相互に接続する補助配線50と、を有する。

(もっと読む)

電子回路網の信頼性を向上させるための装置および関連する方法

【課題】電子回路網の信頼性を向上させるための装置および関連する方法を提供すること。

【解決手段】上記装置は、装置の第1の構成に使用される第1のセットの回路要素と、装置の第2の構成に使用される第2のセットの回路要素とを含み、装置の第1の構成は、装置の信頼性を向上させるために、装置の第2の構成に切り替えられる。上記方法は、第1の構成に割り当てられた第1のセットの回路要素を使用することによって、第1の構成で集積回路(IC)を動作させることと、第2の構成に割り当てられた第2のセットの回路要素を使用することによって、第2の構成でICを動作させることとを含み、第1の構成でICを動作させた後に第2の構成でICを動作させるのは、ICの信頼性を向上させる。

(もっと読む)

半導体集積回路装置

【課題】電源遮断領域の信号配線の自由度を低下させないで、電源遮断用スイッチから電源遮断領域に至る電圧伝達経路における電圧降下を抑える。

【解決手段】半導体集積回路装置(80)は、電源遮断用スイッチ(90)と電源遮断領域(763)とが形成された半導体チップ(22)とを含む。半導体チップは基板(21)に結合される。上記電源遮断領域の外側に上記電源遮断用スイッチを配置することで、電源遮断領域内の配線チャネル数の低減を回避する。そして上記基板には、上記半導体チップ内から上記電源遮断用スイッチを介して上記半導体チップの外に伝達された電源電圧を再び上記半導体チップ内に伝達して上記電源遮断領域へ給電するための基板側給電路(30)を形成することで、上記電源遮断用スイッチと上記電源遮断領域との間の電圧降下を抑える。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電圧の供給を停止しても論理回路の結線状態を保持可能なプログラマブルロジックデバイスにおける処理速度の向上及び低消費電力化を図ることを目的の一とする。

【解決手段】論理状態を切り替え可能な複数の演算回路と、演算回路の論理状態を切り替えるコンフィグレーション状態切り替え回路と、演算回路の電源電圧の供給または停止を切り替える電源制御回路と、複数の演算回路の論理状態及び電源電圧の状態を記憶する状態記憶回路と、状態記憶回路の記憶情報に応じて、コンフィグレーション状態切り替え回路及び電源制御回路の制御を行う演算状態制御回路と、を有し、演算回路とコンフィグレーション状態切り替え回路との間に、酸化物半導体層にチャネル形成領域が形成されるトランジスタが設け、電源制御回路からの電源電圧の停止時に該トランジスタの導通状態を保持する。

(もっと読む)

半導体装置

【課題】プログラマブルなアナログデバイスを提供する。また、電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルにおいて、ユニットセルのスイッチとして、第1乃至第4のトランジスタを用い、第1のトランジスタと第2のトランジスタとが接続された第1のノード、及び、第3のトランジスタと第4のトランジスタが接続された第2のノードの電位を制御することで、ユニットセルの出力を導通状態、非導通状態、又はアナログ素子を介した導通状態のいずれかに切り替える半導体装置を提供する。

(もっと読む)

半導体装置

【課題】FETの駆動力性能や遮断性能などを向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備える。前記半導体素子は、前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、前記絶縁膜の上方に配置されるゲート電極と、前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

(もっと読む)

半導体集積回路および半導体集積回路の設計方法

【課題】半導体集積回路の面積を増大させることなく、配線性のよいテスト専用回路の電源遮断を実現する半導体集積回路を提供する。

【解決手段】テスト実行時のみ動作するテスト専用回路を有する半導体集積回路1であって、当該半導体集積回路1の内部回路領域(内部制御回路部100)に電源を供給する通常電源(通常動作用電源)104と、当該内部回路領域の全面にメッシュ状に配線され、テスト専用回路に電源供給するテスト用電源103と、テスト用電源103と通常電源104とを接続及び遮断して、通常電源104からテスト用電源103への電源供給を制御する電源遮断スイッチ109と、を備える。

(もっと読む)

半導体装置

【課題】回路規模が増大化する。

【解決手段】抵抗値が順に小さい値となって直列接続される複数のヒューズを備えるヒューズ部と、前記ヒューズ部の複数のヒューズのそれぞれ一端と、第1の電源電圧との間に接続される複数の選択スイッチと、前記第1の電源電圧から所定の電位差を有するヒューズ溶断用電圧を、前記ヒューズ部の最も小さい抵抗値のヒューズ側に出力するヒューズ溶融電圧出力回路と、ヒューズ溶断時に、前記ヒューズ溶融電圧出力回路が前記ヒューズ溶断用電圧を出力し、前記ヒューズ部の最も大きい抵抗値のヒューズに接続される選択スイッチから最も小さい抵抗値のヒューズに接続される選択スイッチまでを順に導通させる制御回路と、を備える半導体装置。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

半導体集積回路装置のレイアウト設計方法

【課題】チップサイズの増大を抑制できる半導体集積回路装置のレイアウト設計方法を提供する。

【解決手段】外部電源電圧が供給される第一電源線と第一電源線にスイッチとなる第二電源ドライバを介して接続される第二電源線とを備えた、SCRC方式を採用した半導体集積回路装置において、第二電源ドライバのレイアウト面積の増大を抑制するために、半導体集積回路装置の全回路を機能別回路に分割し、機能別回路領域毎に、SCRC方式による制御対象の回路であるSCRC使用動作回路のトランジスサイズに応じて第二電源ドライバとして用いるMOSトランジスタのサイズを決定する。

(もっと読む)

1 - 20 / 339

[ Back to top ]