Fターム[5F064CC21]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | ダイオード (156)

Fターム[5F064CC21]に分類される特許

141 - 156 / 156

半導体集積回路およびその設計方法

【課題】 半導体プロセスのうち金属配線形成時のプラズマ工程において発生するアンテナダメージを防止する事が可能な半導体集積回路を提供する。

【解決手段】 第2導電型ウェル11上に第1導電型拡散層21を設け、MOS型トランジスタのゲート電極13と第1導電型拡散層21をコンタクトホール31、32とCuからなる金属配線41を介して接続する。さらに、第1導電型ウェル12上に第2導電型拡散層22を設け、MOS型トランジスタのゲート電極13と第2導電型拡散層22をコンタクトホール33、34とCuからなる金属配線42を介して接続し、ゲート電極13と第2導電型ウェル11との間のダイオード1を、ゲート電極13と第1導電型ウェル12との間にダイオード2をそれぞれ設置する。これにより、MOS型トランジスタのゲート電極に発生するアンテナダメージを防止する。

(もっと読む)

レイアウト検証方法およびこれを用いた半導体集積回路装置の設計方法

【課題】

ゲートの受けるダメージを正確に検知することのできるレイアウト検証方法を提供する。

また本発明は、ゲートの受けるダメージを正確に検知するとともにプラズマチャ−ジングダメージを回避するための設計修正のための方向性を判断し、より作業性よく信頼性の高い設計方法を提供する。

【解決手段】

本発明に係るレイアウト検証方法では、アンテナ比と、当該トランジスタゲートの近傍のレイアウトによるプラズマチャージングダメージの変動率とに基づいて、トランジスタゲートダメージの推定値であるアンテナ値として出力するようにしたことを特徴とする。

(もっと読む)

半導体集積回路の設計方法

【課題】JIもしくはSIを用いた半導体集積回路の設計方法であって、寄生バイポーラトランジスタの影響やサージに対するガードリングを入れた効果等をシミュレーションにより予め解析することができ、製品コストを低減することのできる半導体集積回路の設計方法を提供する。

【解決手段】半導体基板の表層部において集積回路を構成する複数の半導体素子を、CAD上でレイアウトする第1ステップS1と、CAD上のレイアウト図から、半導体素子以外の寄生バイポーラトランジスタを抽出する第2ステップS2と、寄生バイポーラトランジスタの回路パラメータを、デバイスシミュレータ(TCAD)により抽出する第3ステップS3と、寄生バイポーラトランジスタを集積回路に組み入れて、回路シミュレータ(SPICE)により回路動作解析を行う第4ステップS4とを有する半導体集積回路の設計方法とする。

(もっと読む)

半導体集積回路

【課題】 降圧回路の配置や、電源間保護回路に対する均等配置の点において半導体チップの空きスペースを有効活用する。

【解決手段】 半導体チップに、複数の外部信号端子と、複数の外部電源端子と、複数のグランド端子と、前記外部電源端子から供給される外部電源電圧を降圧する複数の降圧回路(7)と、前記外部信号端子に接続され前記外部電源電圧を動作電源として用いる複数のバッファ回路(5)と、電源配線とグランド配線の間の高電圧変動に対する保護回路(6)とを有する。降圧回路は前記バッファ回路の矩形セル領域とは異なる矩形セル領域に配置し、降圧回路の一部であるクランプMOSトランジスタを分離してバッファ回路のセル領域に分散させることを行わない。半導体チップ四隅のコーナー部を活用して保護回路を配置することにより、ESD等の高圧サージに対する保護の信頼性向上に資することができる。

(もっと読む)

レイアウトパターン検証方法

【課題】

ウェルの電位を電源端子の電圧値に基づいて比較し、順方向バイアスとなるように電源が接続されたガードリング領域を検出する方法を提供する。

【解決手段】

レイアウトパターンからガードリング領域を抽出する第1工程と、半導体集積回路の電源端子と電気的に接続された電源配線を抽出する第2工程と、電源配線と電気的に接続されたガードリング領域を抽出する第3工程と、第1工程または第3工程において抽出したガードリング領域を含むウェルを抽出する第4工程と、第4工程において抽出したウェルと当該ウェルに隣接するウェルとで形成されるダイオードを抽出する第5工程と、第3工程で抽出したガードリング領域に接続する電源端子の電圧値に基づいて、ダイオードを形成するウェル間の電位差を算出し、当該電位差がダイオードの順方向バイアスとなる場合に、不具合レイアウトパターンとして判定する第6工程とを実行する。

(もっと読む)

半導体装置、ICカード、ICタグ、RFID、トランスポンダ、紙幣、有価証券類、パスポート、電子機器、バッグ及び衣類

【課題】 IDチップに用いる半導体装置において、役割が終了したり、失効したときにその後の動作を停止する半導体装置を提供することを課題とする。

【解決手段】 本発明は、絶縁基板上にアンテナ回路と、電圧検出回路と、電流増幅回路と、信号処理回路と、ヒューズとを有し、アンテナ回路に大電力が印加されたときに、電圧検出回路にて電圧を検出し、その電流に応じた電流を電流増幅回路で増幅し、ヒューズを溶断する。また、アンチヒューズが用いられる時は過大な電圧を加えて、アンチヒューズを短絡させる。このように信号処理回路の動作を停止させ、役割が終了した、または失効したときに無効とする機能を有する半導体装置であることを特徴とする。

(もっと読む)

検査可能な静電気放電保護回路

パワーMOSFET(308)などのMOSFETのためのボンディングパッド(301)と、ESD保護回路(306、307)のための分離されたボンディングパッド(302)とを有する半導体ダイを提供する。ボンディングパッド(301、302)同士を接続すると、MOSFET(308)を保護するべくESD保護回路(306、307)が作動する。ボンディングパッド同士を接続する前に、ESD保護回路(306、307)及び/またはMOSFET(308)を個々に検査することができる。MOSFET(308)を検査するときには、ESD保護回路(306、307)の作動電圧より高い電圧を用いることができる。フリップチップパッケージにおける基板へのダイアタッチやワイヤボンディングなどのパッケージング工程によって、検査後にボンディングパッド(301、302)を電気的に接続することができる。  (もっと読む)

(もっと読む)

レイアウト検証方法及び装置

【課題】 アンテナダメージを防止するためのレイアウト検証を効果的に行うことにより、効率的なレイアウトを実現し、半導体装置を小型化することを課題とする。

【解決手段】 ビアを介してゲートに接続される配線を着目配線としてその着目配線とそれに隣接する配線との間隔を取得する間隔取得ステップ(S401)と、着目配線と隣接配線の間隔、ゲートの面積及び着目配線の面積に応じてアンテナ比を演算する演算ステップ(S402〜S404)と、アンテナ比が所定値を超える場合にはアンテナダメージエラーを出力する出力ステップ(S404)とを有するレイアウト検証方法が提供される。

(もっと読む)

バッテリ充電制御装置

【課題】出力制御用のサイリスタチップのカソード電極にボンディングされる2本のワイヤにかかる負担を均等にして信頼性を向上させたバッテリ充電制御装置を提供する。

【解決手段】磁石式交流発電機の交流出力を直流出力に変換してバッテリに供給するコンバータ回路を構成するダイオードDuないしDw及びDxないしDzと、サイリスタThuないしThwとをヒートシンクHuないしHwに取り付ける。サイリスタThuないしThwとして、アノード電極がヒートシンクに接合されたチップ型サイリスタを用いる。各サイリスタのアノード電流を流すために2本のワイヤW2a,W2bを用い、各サイリスタのカソード電極Kに2本のワイヤW2a,W2bをボンディングする。ワイヤW2a,W2bがボンディングされるカソード電極K上の2つのボンディング点Ba及びBbをゲート電極Gからの距離が等しい位置に設定する。

(もっと読む)

半導体装置

【課題】 半導体装置の冗長用ヒューズの切断面で発生するESDサージから内部回路のトランジスタを保護することを目的とする。

【解決手段】 第1導電型不純物が添加された半導体基板と、前記半導体基板表面に形成された絶縁膜と、前記絶縁膜上に形成されたヒューズと、前記ヒューズと電気的に接続され、かつ第2導電型不純物が添加されて前記半導体基板表面に形成された第1拡散層と、

基板電位に接続され、かつ第1導電型不純物が、前記半導体基板に添加された前記第1導電型不純物よりも高濃度に添加されて前記半導体基板表面に形成された第2拡散層であって、前記第1拡散層、前記半導体基板とともにダイオードを構成する前記第2拡散層と、前記第1拡散層に電気的に接続されたトランジスタとを備えることを特徴とする半導体装置。

(もっと読む)

銀アイランドアンチヒューズ

【課題】改善された不揮発性メモリデバイス及びその回路構成要素の提供

【解決手段】銀アイランドアンチヒューズ(100)は、第1の電気導体(102)と、第1の導体(102)と接触している電気的に抵抗性の材料(104)と、第1の電気導体(102)の反対側において、電気的に抵抗性の材料(104)上に配置された少なくとも1つの銀アイランド(108)とを含む。銀アイランド(108)上に配置される第2の電気導体(106)が、銀アイランド(108)を電気的に抵抗性の材料(104)に密着させる。銀アイランドアンチヒューズ(100)の両端に臨界電位が印加されると、銀アイランド(108B)から電気的に抵抗性の材料(104)を貫通する金属フィラメント(300)が降下して、短絡を確立し、ひいては銀アイランドアンチヒューズ(100)を高抵抗から低抵抗に切り替える。

(もっと読む)

半導体装置

【課題】 内部回路への配線に制約を与えることなく、静電破壊の耐性を向上させることのできる半導体装置を提供することを目的とする。

【解決手段】 電源電圧が供給される電源パッド2及び3と、電源パッド2及び3に夫々接続される電源配線4及び5と、信号を入出力する入出力パッドP1、P2、・・・、P14と、該入出力パッドP1等に電気的に接続され、且つ電源配線4及び5を夫々介して電源パッド2及び3に電気的に接続される静電保護素子Q1、Q2、・・・、Q14と、信号配線R1等を介して入出力パッドP1等と電気的に接続される内部回路6と、を備えたICチップ1において、静電保護素子Q1等並びに電源配線4及び5を、入出力パッドP1等の外側に配置する。

(もっと読む)

半導体集積回路装置及び回路配線方法

【課題】 ゲート電極に繋がる配線に関し、アンテナ効果によるチャージングの影響を極力抑え、プラズマ処理を伴うウェハプロセスにおいても高信頼性が得られる半導体集積回路装置及び回路配線方法を提供する。

【解決手段】 配線部WR1はゲート電極13引き出し用の縦方向優先配線部として、最終的な配線前の配線層153まで配線面積を最小限とする。これにより、アンテナ効果対策として最良の配線構造が得られる。一方、配線部WR2は、アンテナ効果対象外の配線パターンとして、配線部WR1との接続以外の実質的な回路配線を構成する広域配線部である。また、必須パターンとして配線部WR1近傍にパターン端部153Eを配する。配線部WR3は最終接続配線部である。すなわち、配線部WR1は、配線部WR3によってはじめて他の必要な素子回路(配線部WR2)と接続関係を持つことになる。

(もっと読む)

静電放電保護回路

プログラム可能なポリシリコンフューズのような繊細な回路を有する集積回路が提供される。静電放電イベントの存在下において、繊細な回路がダメージと望ましくないプログラミングとを被らないように保護する静電放電(ESD)保護回路が提供される。静電放電保護回路は、ESD信号にさらされたときに、繊細な回路にわたる電圧レベルを最大電圧に制限し、繊細な回路から離れて電流を汲み上げる電力ESDデバイスを有し得る。静電放電保護回路はまた、最大電圧が繊細な回路にわたって印加されたときに電流が繊細な回路を流れないようにするのに役立つESDマージン回路をも含み得る。  (もっと読む)

(もっと読む)

ナノメートルスケールの再構成可能な抵抗器クロスバースイッチを用いたコンピューティングのアーキテクチャ及び方法

コンピューティングのアーキテクチャは、ナノメートルスケールのクロスバースイッチ(100)を含み、これらナノメートルスケールのクロスバースイッチ(100)は、ナノメートルスケールのクロスバースイッチ(100)において論理値をインピーダンスとして符号化する一連のパルスに応答して論理関数を実行するように構成されている。  (もっと読む)

(もっと読む)

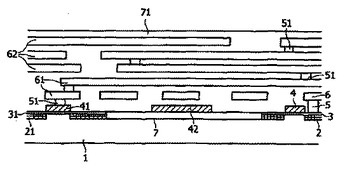

機密性を要する半導体製品、特にスマートカード・チップ

機密性を要する半導体製品、特にスマートカード・チップを提供するため、チップ設計によって実現されうる電気的に活性な構造(2、3、4、5、6)が、例えばシリコンからなるウェーハ(1)内及びウェーハ(1)上に、回路機能の形態で製造されるだけでなく、残りの領域に、それらの下に置かれた機密性を要する回路構造を解析するリバース・エンジニアを大幅に妨げる、互いに絶縁された充てん構造のさらなる導電性部分(42、61、62)(タイル)が設計プログラムによって形成される。形成された部分を説明された偶然の信号経路と連結するための形成された部分間のコンタクトは、「手で」、又は、当該設計プログラムと対応するルーティング・プログラムとの組合せによって配置されることができる。充てん導電性部分はさらに、さらなる回路機能(例えば解析回路)を提供するために、トランジスタ、ダイオード、抵抗器又はコンデンサなどの回路構成部品に接続されてもよい。  (もっと読む)

(もっと読む)

141 - 156 / 156

[ Back to top ]