Fターム[5F064CC21]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | ダイオード (156)

Fターム[5F064CC21]に分類される特許

41 - 60 / 156

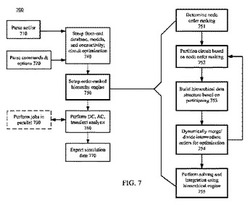

電子回路の階層的次数ランキングされたシミュレーション

【課題】集積回路設計をシミュレートする方法を提供する。

【解決手段】本発明の方法では、ネットリストにおけるノードのノード次数ランキングを決定することができる。ネットリストの回路は、ノード次数ランキングに基づいて静的及び動的電流駆動方式でパーティショニングされることができる。ノード次数パーティショニングに基づいて階層データ構造が構築されることができる。一実施形態では、シミュレーション最適化のために中間ノード次数を動的に結合することができる。その後、回路を1若しくは複数の結合された中間ノード次数に基づいて再パーティショニングすることができる。階層データ構造を用いて求解及び積分を行い、次数ランキングされた階層エンジンを生成することができる。次数ランキングされた階層エンジンについての解析を行うことができる。この時点で、解析に基づいてIC設計のシミュレーションデータがエクスポートされることができる。

(もっと読む)

半導体装置の設計方法

【課題】配線層の溶出、および酸化を抑制する半導体装置、およびその設計方法を提供する。

【解決手段】接続コンタクトに接続される金属配線の配置を決定するステップと、接続コンタクトを設けるためのスルーホールの配置を決定するステップとを具備する半導体装置に設計方法を適用する。ここで、金属配線の配置を決定するステップは、(a)スルーホールによって露出する金属配線の領域を特定するステップと、(b)金属配線に付帯する容量を特定するステップと、(c)容量が蓄える電荷が、領域を介して金属配線から極性溶媒に移動したときの領域の損傷を抑制するように、金属配線の配置を決定するステップとを含むものとする。

(もっと読む)

集積回路装置及び電子機器

【課題】I/Oセルを効率良く配置できる集積回路装置及び電子機器等を提供すること。

【解決手段】集積回路装置は、各I/OセルがI/O回路及びパッドで構成される複数のI/Oセルと、コア回路102とを含み、チップ外縁部101からコア回路102へ向かう方向を第1の方向とした場合に、複数のI/Oセルのうちの第1のI/Oセル10の第1のI/O回路11及び複数のI/Oセルのうちの第2のI/Oセル20の第2のI/O回路21は、第1の方向に沿って並んで配置され、第1の方向に直交する方向を第2の方向とした場合に、第1のI/Oセル10の第1のパッド12は、第1のI/O回路11の第2の方向に配置される。

(もっと読む)

半導体製品ダイのテスト方法及び同テストのためのテストダイを含むアセンブリ

【課題】製品ダイ(2011,300)の製品回路(202,302,304)をテストするためのテストアセンブリ(2000)を提供すること。

【解決手段】一実施形態では、テストアセンブリは、テストダイ(2010,400)及び該テストダイをホストコントローラ(2002)へ電気的に結合する相互接続基板(2008)を含む。該テストダイは、テスト回路(202A,402,404)及び製品回路を統合化された設計(102)に同時に設計するステップを含むテストダイ及び製品ダイに関する設計方法論(100)に従って設計可能である。テスト回路は、該テスト回路により必要とされるシリコン領域の量にほぼ関係なく、対応する製品回路に関して高度の欠陥検出範囲を提供するよう設計可能である。次いで該設計方法論は、統合化された設計をテストダイ及び製品ダイへと分割する(104)。テストダイはテスト回路を含み、製品ダイは製品回路を含む。

(もっと読む)

半導体集積回路装置

【課題】 信号転送速度や波形品質の維持と静電保護とを両立すると共にチップ面積の肥大化を抑制した半導体集積回路装置を提供する。

【解決手段】 静電保護の効果を維持しつつ、信号転送速度や波形品質を維持すると共に、差動入力対を一つの静電保護素子で同時に保護し面積的優位性を得る為、任意に分離可能な静電保護素子を終端抵抗の中点に配置する。

(もっと読む)

ウェハ貫通ビア構造を有するESDネットワーク回路及び製造方法。

【課題】ウェハ貫通ビア構造を有するESDネットワーク回路及びその製造方法を提供する。

【解決手段】本発明は一般に回路構造及び回路の製造方法に関し、より具体的には、ウェハ貫通ビアを有する静電放電(ESD)回路及びその製造方法に関する。ESD構造体は、ESD能動デバイスと、ESD能動デバイスから基板への低直列抵抗経路をもたらす少なくとも1つのウェハ貫通ビアとを備える。装置は、入力部と、少なくとも1つの電力レールと、入力部と少なくとも1つの電力レールとの間に電気的に接続されたESD回路とを含み、ここでESD回路は少なくとも1つのウェハ貫通ビアを備えて基板への低直列抵抗経路をもたらす。方法は、ESDデバイスを基板上に形成することと、基板の裏面に接地面を形成することと、ESD能動デバイスの負電源及び接地面に電気的に接続されて基板への低直列抵抗経路をもたらす少なくとも1つのウェハ貫通ビアを形成することとを含む。

(もっと読む)

ESD保護検証装置及びESD保護検証方法

【課題】信頼性の高いESD保護検証を高速に実行する。

【解決手段】本発明の例に関わるESD保護検証装置は、第1のパッドに接続された素子を抽出する素子抽出部11と、抽出された素子の中から第1のパッドに第1の端子が接続された1つ以上の素子を判別し、その素子の寸法情報に基づく第1の演算値を算出する第1の素子情報調査/演算部12と、第1の基準値と第1の演算値とを比較し、素子が所定のESD耐圧を有するか否か判定する第1のエラー検出部13と、第1のパッドに第1の端子が接続された素子の中から第2の端子が第2のパッドに接続された1つ以上の素子を判別し、その素子の寸法情報に基づく第2の演算値を算出する第2の素子情報調査/演算部14と、第2の基準値と第2の演算値とを比較して、素子が所定のESD耐圧を有するか否か判定する第2のエラー検出部15と、を備える。

(もっと読む)

ESD保護素子検証方法

【課題】多電源が入力される半導体集積回路内で種々の耐圧を有したESD保護素子が適切なESD保護素子であるか否かを容易に検証するESD保護素子検証方法を得ること。

【解決手段】半導体回路の回路図内の素子と素子耐圧情報とを対応付けするステップS10と、使用者からの指示情報に基づいて、回路図内のピンに、電源ピン、GNDピンまたは信号ピンの何れかを設定するとともに電源ピンには印加電圧を設定するステップS22と、ネットリストに基づいて、信号ピンと電源ピンとの間に接続されてPN接合を有している素子を抽出するステップS30と、耐圧情報、電源ピンへの印加電圧およびネットリストに基づいて、抽出した素子が適切な耐圧を有しているか否かを判定するステップ50と、耐圧の判定結果に基づいて、回路図内から不適切な電源側のESD保護素子を抽出して登録するステップS70と、を含む。

(もっと読む)

半導体集積回路装置

【課題】エリアバンプ構造の半導体チップに最適化したI/Oセルのレイアウトを施すことにより、チップサイズを縮小化する。

【解決手段】I/Oセル3は、半導体チップの辺側から中心側にかけて、信号電圧変換回路6、論理部7、プリバッファ部8、ESD保護部の抵抗30、出力バッファ部におけるトランジスタ28、ESD保護部の抵抗31、ESD保護部のダイオード32、パッド接続口3aを挟んでダイオード33、出力バッファ部におけるトランジスタ29、およびコアバッファ部5が直線状にレイアウトされている。プリバッファ部8をパッド接続口3aよりも半導体チップ辺側に配置することによって、該パッド接続口3aをI/Oセル3の中央部よりも半導体チップの中心側にレイアウトでき、半導体チップの辺部に最も近いパッドをI/Oセル3の領域からはみ出すことなくレイアウトできる。

(もっと読む)

半導体構造、半導体構造の形成方法、半導体装置の動作方法(高周波の高調波を減少するためのSOIRFスイッチ)

【課題】SOI基板における容量結合を減少した集積回路を提供する。

【解決手段】底部半導体層と同じ導電型のドーパントを含む第1のドープされた半導体領域18及び反対導電型のドーパントを含む第2のドープされた半導体領域28がSOI基板の埋め込み絶縁層20の直下に形成される。第1のドープされた半導体領域18及び第2のドープされた半導体領域28は、共にグランド電位に接続されるか、又は底部半導体層への少数キャリアの順方向バイアス注入に基づく過剰な電流を生じるには不十分は電圧、即ち、0.6V乃至0.8Vを越えない電位差を保って底部半導体層に対して順方向バイアスされる。上部半導体の半導体装置内の電気信号により誘起される電荷層内の電荷は第1及び第2のドープされた半導体領域に接続されている電気的コンタクトを介して引き出され、これにより半導体装置内の高調波信号を減少させる。

(もっと読む)

半導体集積回路装置

【課題】PAD on I/Oセル構造において、パッド引き出し部のレイアウトをI/O部の略中心に配置し、半導体チップのレイアウト面積を削減する。

【解決手段】I/O部5において、トランジスタ8は、半導体チップの周辺部に最も近い位置にレイアウトされている。このトランジスタ8の上方には、抵抗12がレイアウトされており、抵抗12の上方には、ダイオード10,11がレイアウトされている。ダイオード10,11の上方には、トランジスタ9がレイアウトされており、トランジスタ9の上方には、たとえば、メタル配線層に形成されたパッド引き出し部5aを挟んでロジック部6がレイアウトされている。これにより、パッド2からトランジスタ9のドレインまでを同じノードとすることができるので、パッド引き出し部5aをI/O部5の略中央にレイアウトすることが可能となる。

(もっと読む)

MOS型可変容量素子

【課題】回路構成を複雑化することなく、簡易な等価回路で高周波領域まで実際の電気的特性に合致する任意形状のMOS型可変容量素子をモデリングする。

【解決手段】MOS型可変容量素子は、第1導電型の半導体基板と、前記半導体基板内に形成された第2導電型のウェル領域と、前記ウェル領域内に形成された第2導電型の第1の拡散領域と、前記ウェル領域内に形成された第2導電型の第2の拡散領域と、電圧供給端子と、基板引き出し端子と、ウェル引き出し端子と、単位MOS可変容量部と、を備える。

(もっと読む)

半導体装置、半導体装置の設計方法、半導体設計装置、及びプログラム

【課題】ランプアニール処理において半導体基板内に熱分布が生じることを抑制する。

【解決手段】この半導体装置の設計方法は、半導体基板に不純物拡散層領域及び素子分離膜を配置する工程(ステップS10)と、半導体基板を1mm2以上である所定面積単位で複数の領域に区画する工程(ステップS20)と、複数の領域それぞれで素子分離膜に対する不純物拡散層領域の面積比Tを算出する工程(ステップS30)と、算出した面積比が基準範囲から外れている領域を、補正対象領域として選択する工程(ステップS40)と、補正対象領域にダミー不純物拡散層領域を配置し、面積比Tを基準範囲内にする工程(ステップS50)を備える。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、ボンディングパッドの間隔を任意に調整して配置することができないという問題があった。

【解決手段】本発明にかかる半導体装置は、機能ブロックが配置された内部回路と、ボンディングパッドを複数有するI/Oバッファセル205が内部回路の外周部に沿って配置された周辺回路と、を備える。また周辺回路は、隣接する2つのI/Oバッファセルに所定の間隔を持たせるように内部回路の外周部に沿って配置されたブランクセル206を備える。このような回路構成により、ボンディングパッドの間隔を任意に調整して配置することが可能な半導体装置を提供することができる。

(もっと読む)

集積回路装置のための共通重心静電放電保護

集積回路(IC)内で実現される回路設計を、静電放電(ESD)から保護するための方法は、共通の重心(130)を共有するように、第1の装置アレイ(245)および第2の装置アレイ(250)を備える装置アレイ対(104および108)をIC上に配置することを含み、第1および第2の装置アレイは一致している。第1のESDダイオードアレイ(220)および第2のESDダイオードアレイ(225)を備えるESDダイオードアレイ対(110)は、IC上に、第1および第2の装置アレイを含む第1の周辺部(115)に隣接して配置され得、第1および第2のESDダイオードアレイは共通の重心を共有するとともに、一致している。第1のESDダイオードアレイの各ESDダイオード(220)のカソード端子は、第1の装置アレイ(245)の入力に結合され、第2のESDダイオードアレイの各ESDダイオード(225)のカソード端子は、第2の装置アレイ(250)の入力端子に結合され得る。  (もっと読む)

(もっと読む)

アナログ回路用セルアレイおよびアナログ集積回路

【課題】短いリードタイムで製造でき、高い集積度を有するアナログ回路の実現。

【解決手段】複数のトランジスタセルPMOSC2,NMOSC2が、アレイ状に配置されたアナログ回路用セルアレイARYP1,ARYN1であって、各トランジスタセルは、隣接して順に配置された第1ソース領域SOURCE1、第1チャネル領域、共通のドレイン領域DRAIN、第2チャネル領域および第2ソース領域SOURCE2と、第1チャネル領域および前記第2チャネル領域上にそれぞれ配置された第1ゲート電極POLYG1および第2ゲート電極POLYG2と、を備え、第1ゲート電極POLYG1と第2ゲート電極POLYG2は接続して使用され、第1ソース領域SOURCE1と第2ソース領域SOURCE2は接続して使用される。

(もっと読む)

半導体装置

【課題】PIDの影響を遮断することのできるレイアウト手法を用いてアンテナダイオードを配置することにより、PIDに起因する電界効果トランジスタの特性劣化を防止して、信頼度の高い半導体装置を実現する。

【解決手段】第1アンテナダイオードAD1とnMISのゲート電極16とを第1層目の配線M1を介して電気的に接続し、第2アンテナダイオードAD2と他の半導体素子とを第1層目の配線M1から第4層目の配線(アナログブロック内の最上層配線から1層下の配線)M4を介して電気的に接続する。さらに第1アンテナダイオードAD1と電気的に繋がる第4層目の配線M4と第2アンテナダイオードAD2と電気的に繋がる第4層目の配線M4とをアナログブロック内の最上層配線である第5層目の配線25によって結線する。

(もっと読む)

半導体集積回路装置とテスト端子配置方法

【課題】テスト端子がI/Oセルの1部を占有することをなくし、テスト端子に起因するチップサイズの増大を抑止し、コスト増大を抑止する半導体集積回路装置の提供。

【解決手段】チップの第1の辺に沿って配置される第1の論理回路セル(IOセル)(2)の列と、前記第1の辺と直交する第2の辺に沿って配置される第2の論理回路セル(IOセル)(2’)の列と、を有し、第1の辺と第2の辺とが交わるチップコーナー部において、第1のテスト論理回路セル(4A)は、前記第1の論理回路セル(2)の列の端部のセルの辺に長辺を対向させて配置され、第2のテスト論理回路セル(4B)は、第2の論理回路セル(2’)の列の端部のセルの辺に長辺を対向させて配置され、第1のテスト論理回路セル(4A)と第2のテスト論理回路セル(4B)は、それぞれの平面形状が、対向配置される前記斜辺の中間の仮想線(8)に関して互いに対称(鏡映対称)となるように配置される。

(もっと読む)

回路図設計装置、回路図設計プログラム及び回路図設計方法

【課題】 MOSトランジスタなどの回路素子を共有部分を介して連続接続してなるマルチ素子回路を含む半導体集積回路に係る回路図を設計するのに好適な回路図設計装置、回路図設計プログラム及び回路図設計方法を提供する。

【解決手段】 回路図設計装置100を、レイアウトされた回路図や選択画面から回路記号を選択する回路記号選択部12と、表示情報に基づき回路図の表示制御を行う回路図表示制御部16と、パラメータ設定可能な回路記号に対してマルチ素子回路を生成するためのパラメータを設定するパラメータ設定部18と、予め設定されたルールと回路記号に対して設定されたパラメータとに基づきマルチ素子回路の接続関係情報を生成する接続関係情報生成部20と、予め設定された表示方法のルールに基づきマルチ素子回路の回路記号の表示情報を生成する回路表示情報生成部22とを含んだ構成とした。

(もっと読む)

回路図設計装置、回路図設計プログラム及び回路図設計方法

【課題】 MOSトランジスタなどの回路素子を共有部分を介して連続接続してなるマルチ素子回路を含む半導体集積回路に係る回路図を設計するのに好適な回路図設計装置、回路図設計プログラム及び回路図設計方法を提供する。

【解決手段】 回路図設計装置100を、シンボル回路図や選択画面から回路シンボルを選択する回路記号選択部12と、回路図の表示制御を行う回路図表示制御部18と、パラメータ設定可能な回路シンボルに対してマルチ素子回路を生成するためのパラメータを設定するパラメータ設定部20と、設定されたパラメータが正しいか誤りかを判定するパラメータ判定部22と、パラメータの設定内容に誤りがあるときに正しい設定内容に修正するパラメータ修正部24と、予め設定されたルールと回路シンボルに対して設定されたパラメータとに基づきマルチ素子回路の接続関係情報を生成する接続関係情報生成部26と、を含んだ構成とした。

(もっと読む)

41 - 60 / 156

[ Back to top ]