Fターム[5F064CC21]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | ダイオード (156)

Fターム[5F064CC21]に分類される特許

21 - 40 / 156

半導体装置

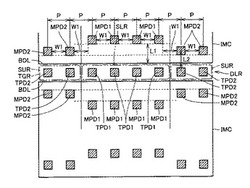

【課題】ダイシング処理に起因する、チップ用パッド同士のショートを抑制することが可能な半導体装置を提供する。

【解決手段】半導体基板と複数の第1のパッドと、複数の第2のパッドとを備える半導体装置であり、第1のパッドは素子形成領域IMC内に、第2のパッドは素子形成領域IMCを取り囲むダイシングライン領域DLR内に形成される。ダイシングライン領域DLRには、第2のパッド同士が電気的短絡を生じさせやすい第1の領域SLRと、第2のパッド同士が電気的短絡を生じさせにくい第2の領域SURとを有している。第1の領域SLRに対向する位置に配置された一部の第1のパッドは、第2の領域SURに対向する位置に配置された残りの第1のパッドよりも、素子形成領域IMCの外縁の1辺BDLから離れて配置されている。

(もっと読む)

レイアウト検証装置及びレイアウト検証方法

【課題】素子と配線、配線と配線の交差部分の耐圧を検証することができるレイアウト検証装置及びレイアウト検証方法を提供する。

【解決手段】レイアウト検証装置は、半導体集積回路の回路図データと、該回路図データに基づいて生成されたレイアウトデータとの整合性を検証する整合性検証手段と、整合性検証手段により整合性が検証された場合に、レイアウトデータに基づいて、互いに交差する位置関係にある素子と配線、又は、配線と配線がなす交差対を抽出する抽出手段と、判定基準となる基準電位差を記憶する記憶手段と、回路図データに基づいて、交差対の電位差を求める電位差検出手段と、交差対の電位差と基準電位差とを比較する電位差比較手段と、を備える。

(もっと読む)

半導体装置

【課題】ダイオードセルを有する半導体装置において、ダイオードセルに隣り合う標準セルについて、光近接効果によるゲート長のばらつきを確実に抑制できるレイアウトを提供する。

【解決手段】標準セルC1は、Y方向に延び、X方向に同一ピッチで配置されたゲートパターンG1,G2,G3を有する。ダイオードセルC2は標準セルC1にY方向において隣り合っている。ゲートパターンG1,G2,G3は、各終端部e1,e2,e3がY方向において同じ位置にあり、X方向における幅が同一である。ダイオードセルC2は、ダイオードとして機能する拡散層D1〜D10に加えて、標準セルC1のゲートパターンG1,G2,G3の終端部e1,e2,e3に対向するように配置された、ゲートパターンG4,G5,G6からなる複数の対向終端部eo1,eo2,eo3を備えている。

(もっと読む)

半導体装置及びその作製方法

【課題】書き込み電圧が小さいアンチヒューズを提供する。

【解決手段】アンチヒューズは読み出し専用の記憶装置のメモリ素子に用いられる。アンチヒューズは、第1導電層、絶縁層、半導体層、及び第2導電層を有する。アンチヒューズに含まれる絶縁層は、原料ガス中にアンモニアを添加して形成した酸化窒化シリコンであり、層中に1.2×1021以上3.4×1021atoms/cm3以下の水素、または3.2×1020以上2.2×1021atoms/cm3以下の窒素を含むことで、低電圧での書き込みが可能となる。

(もっと読む)

半導体装置

【課題】チップ面積を増加させずに、半導体チップの主面上に占める配線領域を拡大する。

【解決手段】半導体チップの主面上に形成された例えばMISトランジスタなどを含んで構成される内部回路7から、例えばダイオードからなる保護素子11および保護素子12に電気的に接続する信号配線8を保護素子11と保護素子12との間の配線13上の取り出し口29から引き出して、信号配線8が占める信号配線領域10を、保護素子12上および電極パッド9下に設ける。

(もっと読む)

半導体装置

【課題】電源電圧の電圧降下を抑制しつつ、信号配線リソースを大きく確保可能な電源配線構造を実現する。

【解決手段】第1配線層に、電源電位配線101a〜101dおよび基板電位配線102a〜102dが形成されており、配線層全体の真ん中より下層側の配線層に、電源ストラップ配線103a,103b,104a,104bが形成されている。上方ビア部114は、下方ビア部112よりも、電源ストラップ配線103a,103b,104a,104bが延びる方向における配置密度が低くなっている。

(もっと読む)

品質優先回路抽出装置、品質優先回路抽出方法、品質優先回路抽出プログラム、マスク作成システム、及びレイアウト制約作成システム

【課題】レイアウト上での素子配置の規則性情報と組み合わせて、差動対回路やカレントミラー回路のようなマスク検査品質を優先する部分回路の抽出を図ること。

【解決手段】品質優先回路ネットリスト抽出装置3で抽出した品質優先回路のネットリスト情報(差動対回路、カレントミラー回路)と品質優先回路レイアウト抽出装置5で抽出した品質優先回路のレイアウト情報(行/列/アレイ構造)から、レイアウトデータに含まれる素子図形に対してマスク検査精度の優先順位を決定する。

(もっと読む)

昇圧回路及び半導体装置

【課題】半導体チップのチップ面積を小さくできる昇圧回路を提供する。

【解決手段】昇圧回路100は、N個(Nは2以上の自然数)の容量素子(容量素子C0〜C3)を備える。N個の容量素子のうち第K番目(1<K<N、Kは自然数)の容量素子(容量素子C2)は第(K−1)番目の容量素子(容量素子C1)によって昇圧された第(K−1)番目の昇圧電圧を受けて、第(K−1)番目の昇圧電圧を更に昇圧した第K番目の昇圧電圧を発生して第(K+1)番目の容量素子(容量素子C3)に供給し、第N番目の容量素子の一端(出力端子OUT)から第N番目の昇圧電圧を発生する。N個の容量素子の内、少なくとも1つの容量素子(容量素子C0及びC1)は他の容量素子(容量素子C2及びC3)が形成された第1のチップ(半導体チップCHIP2)とは異なる第2のチップ(半導体チップCHIP1)に形成され、第1及び第2のチップは互いに積層されている。

(もっと読む)

ヒューズ制御回路、ヒューズ制御システム、照度センサ、近接センサ、携帯電話、デジタルスチルカメラ、および電源回路

【課題】従来のヒューズ制御回路よりも回路規模が低減されたヒューズ制御回路、照度センサ、近接センサ、携帯電話、デジタルスチルカメラ、および電源回路を提供する。

【解決手段】ヒューズ制御回路1は、ヒューズ溶断回路2がヒューズ素子F1に電流を流すとき、ノードBとヒューズ溶断検知回路3とを切断するとともに、ヒューズ溶断回路2がヒューズ素子F1に電流を流さないとき、ノードBとヒューズ溶断検知回路3とを接続する分離用素子4を備える。

(もっと読む)

半導体集積回路および電子回路

【課題】簡易な工程で保護ダイオードが有する寄生容量を内部回路から分離し、半導体集積回路の高速化を実現することが可能な半導体集積回路および電子回路を提供することを目的とする。

【解決手段】信号端子120と内部回路132とを接続する信号ライン134と、信号ライン134から分岐して接続されるヒューズ素子F1と、ヒューズ素子F1を介して信号ライン134と接続し、正電源VDDまたは負電源VSSが直接接続される通電端子136と、ヒューズ素子F1の通電端子136側に接続され、信号ライン134と正電源VDDまたは負電源VSSとの間をそれぞれ逆方向に接続する保護ダイオードD1、D2と、を備えることを特徴とする。

(もっと読む)

半導体構成素子を備えた回路装置

本発明は、電力端子(2.1,2.2)と、該電力端子から電気的に絶縁されている、制御電圧(U2)を印加するための制御端子(2.0)とを有する半導体構成素子(2)、並びに、半導体構成素子の電気的な特性を測定するために制御端子に接触接続するための制御端子コンタクト面(3)を有する電気的な回路装置(1,1a,1b,31,51,61,71)に関する。接続装置(6,32)、特にアンチヒューズ又は回路ユニットが設けられている。接続装置を介して制御端子を直列ユニット(4;34;78,74)と電気的に接続可能であり、接続装置を、制御端子が直列ユニットと電気的に接続されていない非導通状態から、制御端子が直列ユニットと電気的に接続されている導通状態に移行可能である。アンチヒューズを半導体構成素子に集積することができる。  (もっと読む)

(もっと読む)

集積回路装置及び電子機器

【課題】アナログ処理の特性の向上を図れる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、信号が入力されるパッドPANTと、パッドPANTを介して入力される信号についてのアナログ処理を行うアナログ回路と、アナログ回路の信号入力ノードとパッドPANTとの間に設けられるキャパシターCAを含む。パッドPANTとキャパシターCAの一端とが、最上層金属層ALEで形成されるパッド配線LNPにより接続される。

(もっと読む)

T−コイル回路網設計を生成する方法およびT−コイル回路網

T−コイル回路網を備える回路設計を生成する方法の1つの実施形態は、インダクタのインダクタンスおよびT−コイル回路網の寄生ブリッジ容量を決定するステップ(305−340)を含み得る。寄生ブリッジ容量は、T−コイル回路網の出力に結合された負荷の寄生容量に依存する負荷容量基準と比較され得る(345,355)。T−コイル回路網の出力に結合された回路設計の静電放電(ESD)保護の量、または、T−コイル回路網のインダクタのパラメータが、寄生ブリッジ容量と負荷容量基準との比較に従って、選択的に調整され得る(350,360)。インダクタのインダクタンスと、静電放電保護の量と、インダクタの巻線の幅とを特定可能な回路設計が出力され得る(365)。  (もっと読む)

(もっと読む)

シリコン貫通ビアのためのESD/アンテナダイオード

概略を述べると、アンテナダイオードが、少なくとも一部がTSVの周囲の排他的区域内に形成され、金属1層の導電体を介してTSV(シリコン貫通ビア)に接続されている。それと同時に、TSVは、排他的区域の外側に位置する1又は複数のトランジスタのゲートポリ又は拡散領域に接続している。 (もっと読む)

半導体集積回路装置

【課題】電源遮断時にそれ以前の情報を保持する低消費電力モードにおいてその復帰を高速にする。その一つに従来のデータ保持型フリップフロップを用いることが考えられるが、そのためにセルを大きくする等の面積オーバーヘッドが生じるのは望ましくない。

【解決手段】電源遮断時のデータ保持のための電源線は一般の電源幹線よりも細い配線にて形成する。望ましくは、データ保持回路の電源を信号線扱いとして、自動配置配線時に配線することである。そのために、セルにはあらかじめ上記データ保持回路用電源のための端子を通常の信号線と同様に設けて設計しておく。[効果]セルに余分な電源線のレイアウトが不要となり省面積化が図られるとともに、既存の自動配置配線ツールにより設計が可能となる。

(もっと読む)

不揮発スイッチ素子、その動作方法及びそれを用いた回路

【課題】高耐圧かつ不揮発のスイッチ素子を提供する。

【解決手段】上記課題を解決するため本発明のスイッチ素子は、半導体基板中に作られたソース・ドレインと、前記半導体基板上に作られたゲート絶縁膜と、前記ゲート絶縁膜の上に形成された電荷蓄積層と、前記電荷蓄積層の上に形成され前記電荷蓄積層が凹みに接触するイオン伝導層と、前記イオン伝導層の上に形成され前記イオン伝導層の凹みに接触する電荷注入層と、前記イオン伝導層の両脇に形成されたパス制御端子を有する。

(もっと読む)

半導体集積回路

【課題】入力回路または出力回路を介して電源配線にサージ電圧が印加された場合においても、素子面積の増大を抑制しつつ、内部回路を静電破壊から安定的に保護する。

【解決手段】入出力セル3c〜3fの間の隙間に電源保護素子6a〜6dをそれぞれ配置し、電源保護素子6a〜6dとして、電源配線7、8間に接続されたダイオードストリングS2〜S5をそれぞれ用いる。

(もっと読む)

半導体装置

【課題】ESD放電経路におけるメタル配線の電流密度の許容値を高くとることが可能であり、また、配線抵抗を小さくすることが可能である半導体装置を提供する。

【解決手段】信号パッド(101)と、電源線(103)と、接地線(104)と、一端が信号パッド(101)と接続されたインダクタ(111)と、インダクタ(111)の他端と電源線(103)または接地線(104)との間に設けられた終端抵抗(112)と、インダクタ(111)の中間の第1位置(Aa)に接続された第1ESD保護素子(ESD_G)と、インダクタ(111)の中間の第1位置(Aa)とは異なる第2位置(Ab)に接続された第2ESD保護素子(ESD_V)とを備える。

(もっと読む)

半導体装置

【課題】半導体チップのチップサイズを縮小化することができる技術を提供する。特に、LCDドライバを構成する長方形形状の半導体チップにおいて、短辺方向のレイアウト配置を工夫することにより、半導体チップのチップサイズを縮小化することができる技術を提供する。

【解決手段】LCDドライバを構成する半導体チップCHP2は、複数の入力用バンプ電極IBMPのうち一部の入力用バンプ電極IBMPの下層には入力保護回路3a〜3cが配置されている一方、複数の入力用バンプ電極IBMPのうち他の一部の入力用バンプ電極IBMPの下層には入力保護回路3a〜3cが配置されずにSRAM2a〜2c(内部回路)が配置されている。

(もっと読む)

電子回路の階層的次数ランキングされたシミュレーション

【課題】集積回路設計をシミュレートする方法を提供する。

【解決手段】本発明の方法では、ネットリストにおけるノードのノード次数ランキングを決定することができる。ネットリストの回路は、ノード次数ランキングに基づいて静的及び動的電流駆動方式でパーティショニングされることができる。ノード次数パーティショニングに基づいて階層データ構造が構築されることができる。一実施形態では、シミュレーション最適化のために中間ノード次数を動的に結合することができる。その後、回路を1若しくは複数の結合された中間ノード次数に基づいて再パーティショニングすることができる。階層データ構造を用いて求解及び積分を行い、次数ランキングされた階層エンジンを生成することができる。次数ランキングされた階層エンジンについての解析を行うことができる。この時点で、解析に基づいてIC設計のシミュレーションデータがエクスポートされることができる。

(もっと読む)

21 - 40 / 156

[ Back to top ]