Fターム[5F064DD03]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 素子、セル、ブロック等の配置、レイアウト (5,076) | 最適化 (397)

Fターム[5F064DD03]に分類される特許

1 - 20 / 397

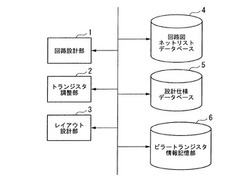

レイアウトデータ作成装置及び半導体装置

【課題】従来のようにピラーの分割単位が小数点数とならず、単位ピラートランジスタのピラーの径の変更を行う必要が無くなり、半導体装置を製造するプロセスを複雑化することなく、ピラー型のトランジスタによりセルを、セルロウ内に効率的に配置するレイアウトデータ作成装置を提供する。

【解決手段】本発明のレイアウトデータ作成装置は、集積回路における複数の単位ピラー型トランジスタで構成されるピラー型トランジスタを、配置領域内に配置可能な単位ピラー型トランジスタの整数単位に分割し、配置領域内に配置するサブピラー型トランジスタを生成するトランジスタ調整部2を備えている。

(もっと読む)

半導体設計装置、半導体設計方法及びプログラム

【課題】信号の重要度を考慮に入れたセルの自動配置を行うアルゴリズムは存在しない。従って、重要配線が不必要に長くなる場合がある。重要配線が長くなると、重要配線を伝達する信号を劣化させる原因となり得る。そのため、信号の重要度を考慮に入れたセルの自動配置を行うことで、重要度の高い信号の品質を維持する半導体装置を設計できる半導体設計装置、が望まれる。

【解決手段】半導体設計装置は、半導体装置に含まれる複数のセルを接続する複数の信号配線から、伝達する信号が重要であることを示す重要配線情報が付された重要配線と、複数の信号配線のそれぞれに接続されているセルの数を示すセル接続数と、を抽出する配線情報抽出部と、配線情報抽出部が抽出した重要配線及びセル接続数に応じて、複数のセルの配置を決定するセル自動配置部と、を備えている。

(もっと読む)

回路設計装置、デカップリング容量効果最適化方法、及びプログラム

【課題】 本発明の課題は、デカップリング容量効果を最適化した回路設計を行うことを目的とする。

【解決手段】 上記課題は、回路を構成する複数のセル間のネット毎の高電位電源側及び低電位電源側の配線容量と、各入力ピンの該高電位電源側及び該低電位電源側の容量とを記憶する記憶部と、前記記憶部に記憶された前記各ネットの配線容量と、前記各入力ピンの容量とを参照して、前記構成における非動作パスに対して、セルの置換前の該セルの組み合せと、セルを置換する際の制約に従った置換後のセルの組み合せのうち、該非動作パスの信号値の遷移状態に応じた、各ネット及び各入力ピンの前記高電位電源側又は前記低電位電源側の容量を加算した総容量に基づいて、該総容量が最大となるセルに置換することによって、デカップリング容量効果を最適化する最適化処理部と、を有する回路設計装置により達成される。

(もっと読む)

半導体集積回路のレイアウト設計装置、方法、及びプログラム

【課題】アナログ回路において最適な配線効率を実現するためのレイアウト設計を可能にする。

【解決手段】機能ブロックを構成する素子をその種類毎にグループ化する。機能ブロック内の素子の配置を各素子の接続関係に基づいて決定する。この時、グループを構成する素子の分割数を考慮してもよい。機能ブロックの配置順序を面積又は幅が大きい順に配置されるように決定する。また、配置順序はユーザの指定により調整できることが好ましい。配置順序と回路全体の接続情報とに基づいて各機能ブロックの配置位置を決定する。

(もっと読む)

配置配線装置

【課題】効率的にIR−Dropを防止することが可能な配置配線装置を提供すること。

【解決手段】複数のセルを配置した後、セル間の隙間が所定の大きさよりも小さい場合にはセル間の隙間が所定の大きさ以上となるようにセルの配置を変更する(S17)。そして、配置された複数のセルの間に容量セルを挿入し(S15)、配置された複数のセルの配線を行なう(S14,S16)。したがって、効率的にIR−Dropを防止することが可能となる。

(もっと読む)

半導体集積回路装置

【課題】チップ面積を増加させることなく、効率良くリーク電流を抑制することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は論理が同一のセルA−1,B−1,C−1を備えている。セルB−1はセルA−1よりセル幅W2が大きいが、MOSトランジスタのゲート長L1はセルA−1と等しい。セルC−1は、セルB−1とセル幅W2が等しいが、ゲート長L2が大きいMOSトランジスタを有しており、セルA−1,B−1と比べて回路遅延は遅くなるがリーク電流は小さくなる。このため例えば、空き領域に隣接したセルA−1をセルB−1に置き換え、タイミングに余裕があるパスにおけるセルB−1をセルC−1に置き換えることによって、チップ面積を増加させることなく、リーク電流を抑えることができる。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

半導体集積回路装置の解析方法

【課題】半導体集積回路装置に含まれる回路素子および寄生素子の中から電位変動の発生源から観測点への電位変動の伝播経路の要因となる素子を容易に特定する。

【解決手段】半導体集積回路装置に含まれる回路素子および寄生素子の各々の電位変動量が登録された素子電位変動情報(11)と回路素子および寄生素子の各々の配置位置が登録された素子配置情報(12)とを入力する。素子電位変動情報(11)および素子配置情報(12)を参照して、回路素子および寄生素子の中から予め設定された電位変動閾値よりも大きい電位変動量に対応する素子を選別し、選別された素子の電位変動量および配置位置を示す情報を素子選別情報(10)に登録する。

(もっと読む)

半導体集積回路装置のレイアウト設計方法

【課題】チップサイズの増大を抑制できる半導体集積回路装置のレイアウト設計方法を提供する。

【解決手段】外部電源電圧が供給される第一電源線と第一電源線にスイッチとなる第二電源ドライバを介して接続される第二電源線とを備えた、SCRC方式を採用した半導体集積回路装置において、第二電源ドライバのレイアウト面積の増大を抑制するために、半導体集積回路装置の全回路を機能別回路に分割し、機能別回路領域毎に、SCRC方式による制御対象の回路であるSCRC使用動作回路のトランジスサイズに応じて第二電源ドライバとして用いるMOSトランジスタのサイズを決定する。

(もっと読む)

半導体装置および半導体装置設計方法

【課題】半導体基板においてダミーパターンの配置密度を高める。

【解決手段】半導体基板104には、配線パターン102とダミーパターン106がレイアウトされる。配線パターン102の周囲にはマージン領域がレイアウトされ、マージン領域の周囲にダミー領域がレイアウトされる。このダミー領域に、複数のダミーパターン106がレイアウトされる。ダミーパターン106は、ダミー領域の延伸方向に配列される。マージン領域とダミー領域は、配線パターン102を基準として交互にレイアウトされる。

(もっと読む)

クロックツリー生成方法、クロックツリー生成プログラム、記録媒体、およびクロックツリー生成装置

【課題】外部電源電圧が変動した場合でも、安定に動作する半導体装置を実現することが可能なクロックツリー生成方法を提供する。

【解決手段】プログラム5のCTS部8は、電源領域Aから電源領域Bにクロック信号CLK1,CLK2を伝達する経路L1,L2を設け、電源領域A内の経路L1,L2にそれぞれアンカーバッファB1,B2を配置し、遅延回路D1,D2を電源領域B内の経路L1,L2にそれぞれ配置し、遅延回路D3,D4をアンカーバッファB1,B2の入力ノード側の経路L1,L2にそれぞれ配置する。したがって、外部電源電圧VDD1,VDD2が変動した場合でも、クロック信号CLK1,CLK2の遅延時間は同じになる。

(もっと読む)

レイアウト設計装置

【課題】アナログレイアウト設計の自動化による設計工期の短縮を図ることが可能なレイアウト設計装置を提供すること。

【解決手段】レイアウト設計装置21は、回路データ24の中から特性を一致させる必要があるトランジスタ、抵抗、容量素子群を抽出し、トランジスタ、抵抗、容量素子群の接続関係に基づいてトランジスタ、抵抗、容量素子群に含まれる複数のトランジスタ、抵抗、容量素子によって構成される所定の機能を有する回路、たとえば差動回路、差動負荷回路およびミラー回路を特定する。そして、特定された回路の種別に応じてレイアウト制約30を生成し、レイアウト制約30に基づいて配置配線を行なう。したがって、アナログ回路のレイアウト制約30を自動的に付加することができ、アナログレイアウト設計の自動化による設計工期の短縮を図ることが可能となる。

(もっと読む)

レイアウト設計方法、レイアウト設計システムおよびプログラム

【課題】チップ上のマクロ間の間隔を適正化する。

【解決手段】チップ上の隣接する2つのマクロに挟まれた領域のうち、配線リソース占有率が、所定の目標占有率未満の領域を挟むマクロの少なくとも一方を移動し、配線リソース占有率を上げる第1のステップと、前記第1のステップの実行後、前記チップ上の隣接する2つのマクロに挟まれた領域のうち、配線リソース占有率が所定の目標占有率を超えている領域を挟むマクロの少なくとも一方を移動し、配線リソース占有率を下げる第2のステップと、を有する。

(もっと読む)

集積回路内における、インターフェースデバイスの面積効率の良い配列

【課題】過度にシステムの中にスキューを増加させずに、増加した数の入力/出力デバイスを有するシステムを提供する。

【解決手段】論理回路を備えるコアと、処理コアからおよび処理コアへ信号を伝送するための、複数のインターフェースデバイスであって、2つのタイプのインターフェースデバイスを備える、複数のインターフェースデバイスと、コアに電力を送達するための、電力インターフェースデバイスである、1つのタイプと、コアと集積回路の外部のデバイスとの間で、データ信号を伝送するための信号インターフェースデバイスである、第2のタイプと、を備え、複数のインターフェースデバイスは、コアの外縁に向かう外側列、およびコアの中心により近い外側列の内側にある内側列の、2列に配設され、内側列は、2つのタイプのインターフェースデバイスのうちの一方を備え、外側列は、2つのタイプのインターフェースデバイスのうちの他方を備える、集積回路が開示される。

(もっと読む)

集積回路のレイアウト設計方法、レイアウト設計装置、及び設計プログラム

【課題】高駆動素子が含まれている論理素子経路に遅延素子を挿入してホールドタイム違反を解消する際に、セットアップタイム違反が新たに発生することを防止する。

【解決手段】レイアウト設計方法が、第1フリップフロップ101と、第2フリップフロップ102と、第1フリップフロップ101の出力と第2フリップフロップ102の入力の間の論理回路とを含む集積回路について配置及び配線を行うステップと、ホールドタイム違反を検出するステップと、遅延素子302をホールドタイム違反を解消するように挿入するステップとを備えている。遅延素子302を挿入するステップでは、第1フリップフロップ101と第2フリップフロップ102間の論理素子経路に高駆動素子105が配置されているかが確認され、高駆動素子105が配置されている場合、高駆動素子105の出力に直接に接続されないように遅延素子302が配置される。

(もっと読む)

半導体装置

【課題】2つの入力端子の配置形態を工夫することにより配線層の増設スペースを確保しスタンダードセルの原価低減を図る。

【解決手段】入力端子34bはゲート配線2bに接続され、入力端子34cはゲート配線2cに接続される。また、入力端子34b、34cは、Y方向に互いに近接して配置され、入力端子34bの第2コンタクト配線4bは、第1コンタクト配線3bと隣接し、且つ該第1コンタクト配線3bに対しX方向に延在する。入力端子34cの第2コンタクト配線4cは、第1コンタクト配線3cと隣接し、且つ該第1コンタクト配線3c対して第2コンタクト配線4bとは逆のX方向に延在する。即ち、入力端子34bの第1コンタクト配線3bと入力端子34cの第2コンタクト配線4cとはY方向に互いに対向して配置され、入力端子34bの第2コンタクト配線4bと入力端子34cの第1コンタクト配線3cはY方向に互いに対向して配置される。

(もっと読む)

クロックツリー生成装置及びクロックツリー生成方法

【課題】クロック遅延などを調整し易くすることで、タイミングエラーを適切に収束させる。

【解決手段】クロックツリー生成装置は、クロックツリーに関する情報と、クロックツリーに含まれる複数のフリップフロップが用いている複数のクロックに関する情報とを取得する取得手段と、取得手段によって取得された複数のクロックごとに、それぞれのクロックで駆動されるフリップフロップの数を特定するフリップフロップ数特定手段と、フリップフロップ数特定手段によって特定された複数のクロックごとのフリップフロップの数に基づいて、複数のクロックの中でフリップフロップの数が少ない上位のクロックを所定数だけ特定するクロック特定手段と、クロック特定手段によって特定されたクロックで駆動されるフリップフロップを基準にして、クロックツリーを分割する分割手段と、を備える。

(もっと読む)

半導体集積回路レイアウト設計装置、半導体集積回路レイアウト設計方法及びプログラム

【課題】半導体集積回路のレイアウト設計工程において、一定のセル配置品質を保証し、短時間でのセル配置を可能とする。

【解決手段】半導体集積回路を機能単位の各エリアに分解し、各エリアに含まれるセルを個別に配置することで半導体集積回路全体の配置を決定する。具体的には、回路情報から半導体集積回路内のセル間を接続する複数の信号線について、接続方向、入出力及び接続本数に関する信号線接続情報を抽出し、所定の規則に基づき、信号線接続情報からターゲットエリア内の全てのセルの配置を決定する。

(もっと読む)

電力最適化のための粒状チャネル幅

【課題】集積回路の設計において電力を最適化する為に、コンピュータによって読取可能であり、コンピュータによって用いられる1つ以上のセルを有するセルライブラリを記録する記憶媒体の提供。

【解決手段】1つ以上のセルは、フィジカルディメンションパラメータとチャネル幅パラメータとを有する。フィジカルディメンションパラメータは、1つ以上のセルのフットプリントである。チャネル幅パラメータは、最小ドライバサイズと最大ドライバサイズとを有する。チャネル幅パラメータは、1つ以上の電力基準に基づいて集積回路の設計フロー中に、フットプリントを変更せずに、ツールが最大ドライバサイズと最小ドライバサイズとの間でチャネル幅を変更する範囲を定義する。

(もっと読む)

半導体装置の設計方法、設計支援装置

【課題】ランプアニール工程での基板の温度ばらつきを抑制する。

【解決手段】半導体チップ(22)に導入、配置される複数の回路ブロック(A1〜E6)の初期レイアウト(31)を決定する。複数の回路ブロック(A1〜E6)の各々に対し、製造時にアニール用光源から照射される光の影響を受ける受光面を特定する。複数の回路ブロック(A1〜E6)の各々の面積に対する受光面の面積の比率を、受光面積率として算出する。初期レイアウトを、面積が均等な複数の領域の集合(A1〜E6、A2’、B2’、C5’、C6’、D5’、D6’、E3’、E4’)として特定する。基準ブロックの周辺の領域を周辺ブロックとして特定し、基準ブロックの受光面積率と周辺ブロックの受光面積率との和を周辺和とする。複数の領域の各々の周辺和のばらつきが最小となるように、複数の回路ブロックのレイアウトを変更する。

(もっと読む)

1 - 20 / 397

[ Back to top ]