Fターム[5F064EE44]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線(又は配線間)の物理的性質 (2,766) | インダクタンス (65)

Fターム[5F064EE44]に分類される特許

1 - 20 / 65

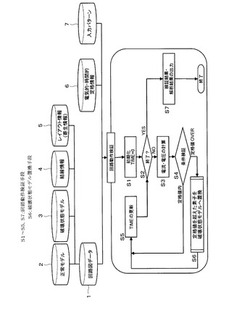

回路動作の検証装置及び回路動作の検証方法

【課題】電圧規格や電流規格を満たさない箇所があった場合に、その影響を反映させて検証を行うことができる回路動作の検証装置を提供する。

【解決手段】回路動作の検証装置は、結線情報4と、定格情報6とを用い、回路に入力する信号パターン7が与えられると、その入力パターン7に基づいて回路動作を検証する(S1〜S5)。そして、検証の結果、回路素子に印加される電圧や通電される電流等が定格値を超えることで破壊に至る回路素子が存在すると、当該回路素子を破壊の態様に応じた破壊状態モデルに置換し(S6)、破壊状態モデルに置換した回路について検証を継続する。

(もっと読む)

半導体装置設計方法および半導体装置設計支援プログラム

【課題】EBDに近いモデリング精度を維持しつつ、モデリングの効率を高める。

【解決手段】複数のチップ(CHIP1〜4)が積層され、それぞれのチップが共通の外部端子104に接続される積層型の半導体装置100の設計に関する。まず、電磁界解析ツールにより、外部端子104とチップを接続するプリント基板配線(共通配線106、個別配線108)の電気的なパラメータを算出し、それらをEBDのパラメータとして設定する。設定されたパラメータに基づいて半導体装置100の電気的な特性をシミュレーション計算する。パラメータの計算・設定に際しては、所定の配線、たとえば、共通配線106や個別配線108などのプリント基板配線の長さを示すパラメータをゼロに設定する。

(もっと読む)

撚り合わされた導線を有する集積回路インダクター

【課題】集積回路インダクターを提供すること。

【解決手段】第1の端子と、第2の端子と、第1の端子と第2の端子との間に連結された伝導性経路とを備え、伝導性経路は、集積回路上に複数の撚り合わされた伝導性線を含む、インダクター。撚り合わされた伝導性線は、集積回路上に少なくとも1つの金属層から形成された少なくとも第1の伝導性線と、集積回路上に少なくとも1つの金属層から形成された少なくとも第2の伝導性線とを含む、インダクター。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

電源ノイズ解析方法

【課題】簡易モデルを使用しても、電源ノイズを高精度かつ高速で解析することのできる電源ノイズ解析方法を提供する。

【解決手段】実施形態の電源ノイズ解析方法は、スイッチング部モデル11と非スイッチング部モデル12とを備える簡易モデル1を用い、半導体集積回路のトグル率の時間軸上の変化を表すトグル率時系列データを生成するステップと、トグル率時系列データにもとづいて簡易モデル1の容量CL、Cnswの容量値の時間軸上の変化を表す容量値時系列データを生成するステップと、簡易モデル1および容量値時系列データを用いて電源ノイズの解析を行うステップとを有する。電源ノイズの解析を行うステップは、スイッチング部モデル11のスイッチSWのスイッチング区間ごとに容量値時系列データから該当区間の容量値を取得し、前区間の過渡解析の結果を引き継ぎながら次区間の過渡解析を実行する。

(もっと読む)

半導体装置の設計支援装置、設計支援プログラム及びレイアウト情報生成方法

【課題】従来の設計支援装置により生成したインダクタは、周囲の回路の影響により特性ずれが生じる問題があった。

【解決手段】本発明の設計支援装置は、生成対象のインダクタに接続される接続対象回路領域の第1、第2の接続端子の位置情報を回路設計情報から生成されるフロアプラン結果から得て、インダクタを他の回路と接続する第3、第4の接続端子を、第1の接続端子と第3の接続端子との間及び第2の接続端子と第4の接続端子との間が最短の配線によって接続可能な位置に設定する端子位置設定部10と、第3、第4の接続端子の位置を基準としてインダクタの配線パターンを生成し、当該配線パターンに基づきインダクタのレイアウト情報を生成するパターン生成部13と、を有する。

(もっと読む)

基板ノイズ解析装置

【課題】 本発明の課題は、被ノイズ回路において影響を受けるノイズの大きさに基づいて効率的に基板ノイズ解析を行うことを目的とする。

【解決手段】 上記課題は、導体集積回路の回路ブロック毎に該回路ブロックの回路データを用いてノイズ源解析を行い、各周波数と該周波数に対するノイズ量とを対応させたノイズ源情報を出力するノイズ源解析手段と、回路ブロック毎に該回路ブロックの回路データを用いて各周波数に対して出力ノードから出力される該周波数の振幅をノイズの影響の大きさを示す感度として解析するノイズ感度解析を行い、各周波数と該周波数に対する感度とを対応させたノイズ感度情報を出力するノイズ感度解析手段と、前記ノイズ源情報と前記ノイズ感度情報とに基づいてノイズを受ける被ノイズ回路の動作に影響を与える周波数成分を特定し、該ノイズ源情報から該周波数成分を抽出するノイズ源情報抽出手段とを有する基板ノイズ解析装置により達成される。

(もっと読む)

半導体装置およびその製造方法

【課題】配線層の平坦性を維持しつつ、配線とインダクタとの間に生じる寄生容量を低減させた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に形成された第1の層間絶縁膜506と、第1の層間絶縁膜506のうち配線形成領域内に位置する部分に埋め込まれた配線106と、第1の層間絶縁膜506のうち配線形成領域内に位置する部分に埋め込まれた第1のダミーパターン107と、第1の層間絶縁膜506のうちインダクタ領域内に位置する部分に埋め込まれた第2のダミーパターン108と、第1の層間絶縁膜506の上方に形成された第2の層間絶縁膜と、第2のダミーパターン108の上方であって、第2の層間絶縁膜のうちインダクタ領域内に位置する部分に埋め込まれたインダクタ111とを備える。第2のダミーパターン108として金属が形成されていない。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置の性能を下げることなく、コスト低減及び小型化を図ることができる半導体集積回路装置を提供する。

【解決手段】内部回路と、外部から入力された入力信号を内部回路に供給及び内部回路から供給された出力信号を外部に出力する入出力回路と、を有する半導体集積回路装置であって、内部回路に駆動電圧を供給するための内部回路用電源端子と、入出力回路に駆動電圧を供給するための入出力回路用電源端子と、内部回路及び入出力回路に共通のグランド電圧を供給するための共通グランド端子と、を有し、内部回路用電源端子、入出力回路用電源端子、及び共通グランド端子が隣り合って配置されることによって当該3つの端子から単位端子群が形成されていること。

(もっと読む)

半導体装置

【課題】ノイズが高周波である場合においても、多層配線層を介してデジタル回路とアナログ回路の間でノイズが伝播することを抑制する。

【解決手段】回路分離領域40は第1回路領域20と第2回路領域30の間に位置している。回路分離領域40には複数の第1導体及び複数の第1ビアが設けられている。複数の第1導体は、電源ライン110より下層に設けられ、電源ライン110に対向しており、かつ繰り返し配置されている。複数の第1ビアは多層配線層の中に、複数の第1導体それぞれごとに設けられており、各第1導体を電源ライン110に接続している。

(もっと読む)

配線構造

【課題】電源・信号間の干渉および結合の抑制と、電源ノイズの抑制と、信号間の干渉・クロストークの抑制と、インピーダンス不連続による信号反射の抑制とを、全てバランスよく満たす低コストな高速デバイスを提供する。

【解決手段】信号用ボンディングワイヤ31d、31eと、グランド用ボンディングワイヤ31b、31gと、電源用ボンディングワイヤ32a、32c、32f]とを、次のように配置する。すなわち、グランド用ボンディングワイヤまたは電源用ボンディングワイヤの一方が、信号用ボンディングワイヤと同じ第1の包絡面に含まれ、他方は別の第2の包絡面に含まれる。ここで、第2の包絡面に含まれるボンディングワイヤおよび信号用ボンディングワイヤの間の電磁結合が、第1の包絡面に含まれる2本のボンディングワイヤの間の電磁結合よりも小さくなるようにする配線構造。

(もっと読む)

回路のジッタを計算する方法、論理装置及びシステム並びに回路のクロックツリーを合成する方法、論理装置及びシステム

【課題】チップレベルの設計に関する問題に対処し、クロストークカップリングが存在する場合でも正確な経路遅延を計算すること。

【解決手段】一実施例でのクロックツリーにてジッタを計算する方法は、クロックツリーを複数のステージに分割し、クロックツリーに関連する回路の少なくとも一部分のモデルに従って、1以上のステージのジッタを算出する。モデルは回路のジッタのソース各々の表現を含む。本方法は、クロックツリー中の経路又は経路対に関するジッタを計算するため、クロックツリー中の経路又は経路対の各ステージのジッタを互いに統計的に合成するステップを含む。一実施例では、ジッタを効率的に計算し且つクロックスキューゼロを達成するため、モデルは回路の対称的なクロックツリーを合成し、そのツリーでは区六浮くツリーのルートからクロックツリーのシンクに至る全てのパス中の関連するステージは、近似的に電気的に互いに等価な性質を示す。

(もっと読む)

電源ノイズ解析方法及び電源ノイズ解析プログラム

【課題】SSOノイズの解析精度を落とさずにパッケージモデルの回路規模を削減できるSSOノイズ解析方法及び装置を提供する。

【解決手段】複数の信号駆動回路と、複数の信号駆動回路に第1の電源電圧を供給する第1の配線と、複数の信号駆動回路に第2の電源電圧を供給する第2の配線と、複数の信号駆動回路により駆動される信号を伝搬する複数の第3の配線とを含んだモデルを用いる電源ノイズ解析方法は、レイアウト情報から第1乃至第3の配線の自己インダクタンス及び相互インダクタンスを抽出し、信号の駆動時に流れる電流経路を特定し、特定された電流経路の情報に基づいて自己インダクタンスと相互インダクタンスとを合成することにより第1乃至第3の配線の各々の実効インダクタンスを求め、実効インダクタンスを含めたモデルを用いて回路シミュレータを実行する各段階を含む。

(もっと読む)

半導体装置

【課題】デカップリング容量セルを用いて電源配線の電圧変動を抑制し、かつ、電源配線の電源共振を防ぐ半導体装置を提供する。

【解決手段】半導体チップ100に複数配置されたデカップリング容量セルを、トランジスタ素子及び容量素子の直列回路で構成する。制御回路CTRCにおいては、半導体チップ100を動作させる基準クロック又はそこから生成される高周波数のクロックが入力され、そのクロックに同期した制御信号CTRLを生成し、デカップリング容量セルの電源配線VDDへの容量素子の接続/非接続を行う。

(もっと読む)

整調可能な特性インピーダンスを有する垂直型共平面導波路、その設計構造、およびその作製方法

【課題】整調可能な特性インピーダンスを有するオンチップ垂直型共平面導波路、その設計構造、およびその作製方法を提供する。

【解決手段】オンチップ伝送線路(60)は、信号ライン(65)、信号ラインの上側にあって該信号ラインから離間された上方接地ライン(70)、および信号ラインの下側にあって該信号ラインから離間された下方接地ライン(75)を包含する。信号ライン、上方接地ライン、および下方接地ラインは、誘電材料(80)中にほぼ垂直並びに配列されている。

(もっと読む)

クロストークノイズエラー判定方法

【課題】回路中の全インスタンスに対してクロストークノイズエラーを判定する場合、どのネットのノイズエラーが集積回路の動作に影響を与えるかを特定できない。また、フリップフロップの入力におけるクロストークノイズエラーを判定した場合、フリップフロップのデータ信号に影響を及ぼすノイズエラーが、どのネットなのかを特定できない。

【解決手段】フリップフロップの動作に影響を及ぼすネットを、フリップフロップのデータ端子から逆方向に検索することで、どのネットの影響でエラーが発生しているのかを容易に特定できる。

(もっと読む)

集積回路設計プログラム、集積回路設計装置および集積回路設計方法

【課題】集積回路の製造後に実施されるテストでRAMが動作しなくなるのを防ぎ、設計への戻りをなくすこと。製造後のテストの回数を減らし、テスト費用の削減を図ること。

【解決手段】集積回路の設計時に、RAMの消費電流値、RAMの配置位置に基づいて消費電流値に重み付けをした重み付け消費電流値、または重み付け消費電流値に素子間の距離を考慮した値に基づいて複数のRAMを複数のグループに振り分ける。各グループについてコアノイズを解析し、得られた電源ドロップ量が所定の条件を満たすか否かを判定する。電源ドロップ量が所定の条件を満たすグループについては、そのグループに含まれるRAMを同時に動作させるRAMとする。一方、電源ドロップ量が所定の条件を満たさないグループについては、RAMの振り分け条件を変更してRAMの振り分けからやり直す。

(もっと読む)

電源ノイズの解析方法

【課題】従来、電源ラインにある一のノードに電源ノイズが発生せず固定の電源電圧が印加されている場合に係るノードに接続された素子に向かって流れる電流を求め、この電流が係るノードから係る素子に向かって流れる場合に係るノードに発生する電圧を求め、これをもって電源ノイズの解析結果とした。しかし、係るノードに発生する電圧が変化すれば、係るノードから係る素子に向かって流れる電流も変化し、係る電流の変化に応じて係るノードに発生する電圧も変化する。従来ではこの現象が考慮されず解析の精度がよくなかった。

【解決手段】係るノードに発生する電圧の電源電圧に対する変動に対応して、係るノードから係る素子に向かって流れる電流の変動の量である電流変動分を求め、係る電流変動分が係る電流に発生した場合に係るノードに発生する電圧の変動の量である電圧変動分を求め、この電圧変動分を使用して電源ノイズを求める。

(もっと読む)

半導体装置およびインダクタンスの調整方法

【課題】製造安定性に優れたインダクタを提供する。

【解決手段】半導体装置100は、シリコン基板101上に設けられた絶縁層105、絶縁層105中に埋設されたスパイラルインダクタ111、および絶縁層105上に設けられた金属層115を含み、金属層115の一部が除去されて切欠部となっている。

(もっと読む)

電流波形解析方法及びその装置

【課題】回路の動作率を基に、統計的に作成した電流モデルを使用して回路シミュレーションを行い、短時間で電流波形に含まれるスペクトルを解析する。

【解決手段】部分回路動作電流解析部10において部分回路の電流波形をデータベース(DB)化し、回路動作率解析部20における高速なシミュレータから得られた部分回路の動作率と、DB化された部分回路の動作とから、電流波形整形部50によって電流波形を作成し、回路シミュレーション部60によって複数回シミュレーションしている。そのため、電流波形の変動を高速に得ることができ、スペクトル解析部70において効率良く信号のスペクトル解析を行うことができる。

(もっと読む)

1 - 20 / 65

[ Back to top ]