Fターム[5F064FF29]の内容

ICの設計・製造(配線設計等) (42,086) | 切り換え、選択 (3,709) | 切り換え、選択部分の素子 (1,619) | フューズ (1,286) | 材料が特定されているもの (479)

Fターム[5F064FF29]の下位に属するFターム

Fターム[5F064FF29]に分類される特許

1 - 20 / 71

カップリングチャネルを使用したアンチヒューズメモリ及びその操作方法

【課題】カップリングチャネルを使用したアンチヒューズメモリ及びその操作方法を提供する。

【解決手段】カップリングチャネルを使用したアンチヒューズメモリは、第1導電型の基板と、第2導電型のドープ領域と、カップリングゲートと、ゲート誘電層と、アンチヒューズゲートと、アンチヒューズ層と、を含む。基板中に隔離構造を有する。ドープ領域が基板中に設置され、且つドープ領域及び隔離構造の間にチャネル領域を定義する。カップリングゲートがドープ領域及び隔離構造の間の基板上に設置され、且つカップリングゲートとドープ領域と隣り合う。ゲート誘電層がカップリングゲート及び基板の間に設置される。アンチヒューズゲートがカップリングゲート及び隔離構造の間の基板上に設置され、アンチヒューズゲート及びカップリングゲートの間に間隔を有する。アンチヒューズ層がアンチヒューズゲート及び基板の間に設置される。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bとを有する。駆動対象の記憶素子21に対して、電極215Aと電極215Bとの間に所定の閾値以上の電圧V1を印加して、半導体層212Nと半導体層213Nとの間の領域にそれらの半導体層同士を電気的に繋ぐ導電パスであるフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

一方向性アンチヒューズ素子及びこれを用いた発光ダイオードユニット

【課題】1列に直列接続された各発光ダイオード(LED)素子の各々にそれぞれ1つのアンチヒューズ素子が並列接続されているLEDユニットにおいて、電源を誤って逆方向に接続した場合にも、LEDユニットを保護する一方向性アンチヒューズ素子を提供する。

【解決手段】1はカソード電極端子Kに接続されたカソード電極層、2はp型不純物層21及びn型不純物層22よりなる半導体層、3は絶縁層、4はボンディングワイヤ5によってアノード電極端子Aに接続されたアノード電極層、6は封止樹脂層である。カソード電極端子Kとアノード電極端子Aとの間に順方向電圧が印加された場合のみ、一方向性アンチヒューズ素子はアンチヒューズとして作用する。カソード電極端子Kとアノード電極端子Aとの間に逆方向電圧が印加された場合には、一方向性アンチヒューズ素子はアンチヒューズとして作用しない。

(もっと読む)

半導体装置

【課題】銅ヒューズに起因する故障または特性悪化を抑制または防止できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、銅ヒューズ4と、半導体基板1と銅ヒューズ4との間に配置された銅膜からなるシール膜7,8と、銅ヒューズ4よりも上の層に形成された銅以外の金属材料膜からなり、銅ヒューズ4の両端にそれぞれに接続された最上層配線501,502と、シール膜7,8に結合され、銅ヒューズ4の周囲を取り囲む筒状に形成された銅シールリング6とを含む。

(もっと読む)

半導体装置

【課題】安定した特性のヒューズ素子を有する半導体装置を提供する。

【解決手段】半導体装置100は、基板10と、基板10の上方に形成され、空洞部20を画成する被覆構造体30と、空洞部20に収容されたヒューズ素子40a,40b,40cと、を含み、被覆構造体30は、導電層を有し、ヒューズ素子40a,40b,40cの材質は、導電層の材質と同じである。

(もっと読む)

半導体装置及びその製造方法

【課題】金属シリサイド層を利用した電気ヒューズの信頼性を向上する。

【解決手段】半導体装置50は、電気ヒューズ16を有する。電気ヒューズ16は、第1の端子領域16aと、第2の端子領域16bと、第1の端子領域16a及び第2の端子領域16bを接続するヒューズリンク領域16cとを備える。ヒューズリンク領域16cは、第1のシリコン膜12cと、第1のシリコン膜上に形成された第1の金属シリサイド層15cとを有する。平面視において、第1の端子領域16aと第2の端子領域16bとが並ぶ方向に垂直な方向の寸法を幅とするとき、第1のシリコン膜12cの少なくとも一部の幅は、第1の金属シリサイド層15cの幅よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】ヒューズ配線を溶断する際に素子分離構造や半導体基板に与えるダメージを抑制することができる半導体装置を提供する。

【解決手段】半導体装置1は、半導体基板10と、半導体基板の主面の面内方向に互いに離間するように形成された一対の電極12A,12Bと、これら電極12A,12Bを被覆し、上面に凹部13cを有する下層絶縁膜13と、凹部13cに形成されたヒューズ配線20Cと、下層絶縁膜13及びヒューズ配線20Cを被覆する層間絶縁膜21と、層間絶縁膜21上に形成され、ヒューズ配線20Cの直上にレーザトリミング用の開口部1hを有する上層絶縁膜31とを備える。

(もっと読む)

半導体装置

【課題】信頼性の高いヒューズを有する半導体装置を提供する。

【解決手段】半導体層22と、この半導体層22の表面に形成され、半導体層22と金属とが反応して形成された化合物層28,29と、半導体層22及び化合物層28,29から成るヒューズと、このヒューズの接地電位側に電気的に接続された、選択トランジスタ11とを含む、半導体装置を構成する。

(もっと読む)

半導体装置

【課題】面積の増加を抑えつつ、ヒューズ構造体のデータの保持量を増加する。

【解決手段】半導体装置100は、基板(不図示)上に形成されたヒューズ構造体120を含む。ヒューズ構造体120は、第1の配線(122)および第2の配線(124)と、これらを接続するビア123とから構成された電気ヒューズ121と、一端がビア123の側方にビア123に接続して形成された抵抗配線128と、を含む。電気ヒューズ121のビア123は、基板の積層方向において、第1の配線(122)との接続箇所から抵抗配線128との接続箇所までの間に、面内方向の断面積が第2の配線(124)との接続箇所から抵抗配線128との接続箇所までの面内方向の断面積よりも小さい箇所を有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ヒューズ層を覆う絶縁膜の膜厚を精度良く調整する。

【解決手段】半導体基板10上にザッピング素子1のヒューズ層12を形成し、ヒューズ層12を覆う第1の絶縁膜13を形成する。第1の絶縁膜13上にはヒューズ層12を覆うエッチングストッパー膜14を形成し、エッチングストッパー膜14を覆う第2の絶縁膜16を形成する。他の工程を経た後、第1のエッチング工程として、ヒューズ層12上で、第2の絶縁膜16をエッチングストッパー膜14に対して選択的にエッチングすることにより、エッチングストッパー膜14の表面を露出させる。次に、第2のエッチング工程として、ヒューズ層12上で、エッチングストッパー膜14を第1の絶縁膜13に対して選択的にエッチングすることにより、第1の絶縁膜13の表面を露出させる。

(もっと読む)

ヒューズ制御回路、ヒューズ制御システム、照度センサ、近接センサ、携帯電話、デジタルスチルカメラ、および電源回路

【課題】従来のヒューズ制御回路よりも回路規模が低減されたヒューズ制御回路、照度センサ、近接センサ、携帯電話、デジタルスチルカメラ、および電源回路を提供する。

【解決手段】ヒューズ制御回路1は、ヒューズ溶断回路2がヒューズ素子F1に電流を流すとき、ノードBとヒューズ溶断検知回路3とを切断するとともに、ヒューズ溶断回路2がヒューズ素子F1に電流を流さないとき、ノードBとヒューズ溶断検知回路3とを接続する分離用素子4を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの性能を良好にするとともに、トランジスタにより構成されたアンチヒューズのゲート絶縁膜の破壊後の特性を良好にする。

【解決手段】アンチヒューズ素子190として機能するNMOSトランジスタにおいて、N型チャネル領域112aが設けられている。また、通常のNMOSトランジスタ194には、N型エクステンション領域120およびP型ポケット領域122が設けられているが、アンチヒューズ素子190には、エクステンション領域およびポケット領域が設けられない。

(もっと読む)

アンチヒューズ素子のプログラム方法および半導体装置

【課題】書込前後の電流値の比を大きくして、アンチヒューズ素子の書込状態を精度よく判定する。

【解決手段】トランジスタにより構成されているアンチヒューズ素子101のプログラム方法は、ゲート電極112に所定のゲート電圧を印加して、ゲート絶縁膜110を破壊するとともに、不純物拡散領域104aおよび不純物拡散領域104bの少なくとも一方の表面に形成されたシリサイド層106aまたはシリサイド層106bを構成するシリサイド材料をゲート絶縁膜110中に移動させて、ゲート電極112と不純物拡散領域104aおよび不純物拡散領域104bの少なくとも一方とをシリサイド材料122を介して電気的に接続する工程を含む。

(もっと読む)

電気ヒューズ構造とその形成方法

【課題】 電気ヒューズ構造とその形成方法を提供する。

【解決手段】 具体例はヒューズ構造である。具体例によると、ヒューズ構造は、陽極、陰極、陽極と陰極間に挿入されるヒューズリンク、及び、陰極に結合される陰極コネクタ、からなる。陰極コネクタは、それぞれ、アクティブ装置に結合されるコンタクトの最小フィーチャーサイズの約二倍以上である。

(もっと読む)

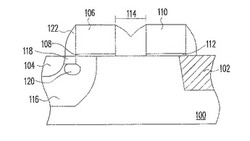

半導体装置およびその製造方法

【課題】ヒューズのカットばらつきを防ぐとともに腐食(酸化等も含む)を良好に防ぐ。

【解決手段】半導体装置100は、基板102と、基板102上に形成されたヒューズ配線116と、少なくともヒューズ配線116の側壁を保護するように形成された耐湿性絶縁膜120と、を含む。耐湿性絶縁膜120は、ヒューズ配線116の上面には形成されていないか、またはヒューズ配線116の上面における積層方向の膜厚d1がヒューズ配線116の側壁における積層方向に垂直な方向の膜厚d2よりも薄くなるように形成されている。

(もっと読む)

アンチヒューズ構造体および形成方法

【課題】 アンチヒューズ構造体および形成方法を提供する。

【解決手段】 アンチヒューズ構造体は基板上に配置された複数の並行導電フィンを含み、フィンのそれぞれは第1の端部と第2の端部とを有する。第2の電気導体はフィンの第2の端部に電気的に接続される。絶縁体はフィンの第1の端部を覆い、第1の電気導体は絶縁体上に配置される。第1の電気導体は絶縁体によってフィンの第1の端部から電気的に絶縁される。絶縁体は、第2の電気導体と第1の電気導体との間に所定の電圧を印加したときに絶縁破壊し、それによりフィンを介して第2の電気導体と第1の電気導体との間に途切れない電気接続を形成するのに十分な厚さまで形成される。

(もっと読む)

半導体装置の製造方法、製造プログラム、及び半導体装置

【課題】回路規模の増大を抑制しつつ、素子破壊によってノード間の電気的接続を制御する電流制御素子を有する半導体装置の信頼性を高める。

【解決手段】本発明による半導体装置の製造方法は、半導体ウエハ1上に形成された素子特性抽出用パタン30の素子特性を測定するステップと、測定された素子特性を、素子特性抽出用パタン30に対応付けられた電流制御素子20の素子特性として抽出するステップと、抽出された素子特性に基づいて、半導体ウエハ1上におけるノード間に形成された電流制御素子20に供給するエネルギーを設定するステップと、設定されたエネルギーを電流制御素子に供給し、電流制御素子の素子破壊によってノード間の電気的接続を不可逆的に制御するステップとを具備する。

(もっと読む)

不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置

【課題】高速動作が可能で、しかも可逆的に安定した書き換え特性を有し、半導体製造プロセスと親和性の高い不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置の提供を目的とする。

【解決手段】第1電極103と、第2電極105と、第1電極103と第2電極104との間に介在させ、両電極103,105間に与えられる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層104とを備えている。この抵抗変化層104は少なくともハフニウム酸化物を含み、当該ハフニウム酸化物をHfOxと表した場合に、0.9<x<1.6を満足するように抵抗変化層104が構成されている。

(もっと読む)

アンチヒューズ素子及びその製造方法

【課題】ショートする箇所を特定することができ、ショート化電圧を高精度に制御することができ、製造コストを低減することができる、アンチヒューズ素子及びその製造方法を提供する。

【解決手段】(a)対向する少なくとも一対の電極膜15,17と、(b)一対の電極膜15,17の間に配置された絶縁体膜16と、(c)一対の電極膜15,17及び絶縁体膜16を支持する基板12とを備える。膜厚方向から透視したときに、少なくとも一方の電極膜17には先端が尖った角部17aが形成され、角部17aは他方の電極膜15に重なっている。電極膜15,17間に電圧が印加されたときに一方の電極膜17の角部17aの先端付近で電界が集中し、ショートに至る箇所を角部17aの先端付近に限定することができる。

(もっと読む)

電気ヒューズおよび半導体装置

【課題】銅を構成材料として用いた電気ヒューズの切断を確実に行うとともに、切断された電気ヒューズの切断状態を良好に保つ。

【解決手段】電気ヒューズ100は、被切断配線102と、被切断配線102の両端にそれぞれ設けられた第1の端子120および第2の端子122とを含む。被切断配線102は、銅を主成分とするとともに(111)面に配向した第1の配向膜104と、第1の配向膜104中に、第1の配向膜104を分断するように、第1の端子120から第2の端子122に向かう方向に対して直角な方向の幅全体にわたって設けられた、銅を主成分とするとともに(511)面に配向した第2の配向膜106と、を含む。

(もっと読む)

1 - 20 / 71

[ Back to top ]