Fターム[5F064FF30]の内容

ICの設計・製造(配線設計等) (42,086) | 切り換え、選択 (3,709) | 切り換え、選択部分の素子 (1,619) | フューズ (1,286) | 材料が特定されているもの (479) | ポリシリコン (151)

Fターム[5F064FF30]に分類される特許

1 - 20 / 151

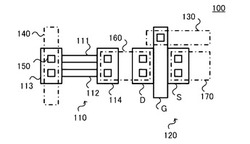

半導体記憶素子及び半導体記憶装置

【課題】LSI素子の性能劣化及びヒューズ素子の欠陥の増加を抑制できる半導体記憶素子及び半導体記憶装置を提供する。

【解決手段】半導体記憶素子100は、第1ヒューズ線111と、第1ヒューズ線111と並列接続された第2ヒューズ線112とを有し、切断されているか否かによって2値のデータを保持するヒューズ素子110と、一端がワード線130に接続されており、ヒューズ素子110に電流を流すか否かを選択する選択素子120と、を備える。

(もっと読む)

半導体装置

【課題】多層配線プロセスでSOGエッチバックにて平坦化を行なうプロセスにて、ヒューズ開口部に起因する水分の浸入における長期信頼性の劣化を防止する半導体装置の製造方法を提供する。

【解決手段】ヒューズ開口部からの水分侵入を防ぐためのメタル1層目のガードリングの下部まで多結晶シリコンが伸びているヒューズ形状にする。これによりヒューズの電極をとるためのメタル配線とガードリングのメタル配線の高さがそろい、SOG層がIC内部に到達することを防ぐことが可能となる。

(もっと読む)

半導体集積回路装置

【課題】過電流に対して内部回路を保護する半導体集積回路装置を提供することを目的としている。

【解決手段】多層配線構造を有する半導体集積回路装置であって、半導体集積回路装置の内部にある内部回路と半導体集積回路装置の外部にある外部回路とを接続するために半導体集積回路装置の内部に設けられたパッドパターンにおいて、第1の配線層と、第1の配線層が形成されている層とは別の層に形成されている第2の配線層と、第1の配線層と第2の配線層を接続するビアと、を備え、第2の配線層にヒューズパターンが形成されており、ヒューズパターンを経由して内部回路と外部回路とを電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】トリミングや冗長に用いられるヒューズを有する半導体装置に関し、安定且つ確実に溶断しうるヒューズを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に、第1の絶縁膜を形成し、第1の絶縁膜上に、ヒューズを形成し、ヒューズが形成された半導体基板上に、第1の絶縁膜に接して第2の絶縁膜を形成し、ヒューズ上の第2の絶縁膜に、開口部を形成し、第2の絶縁膜上及び開口部内に第3の絶縁膜を形成する。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体装置およびその製造方法

【課題】トリミングヒューズの上の絶縁膜が、トリミングヒューズの機能を高めるために適正な状態を維持することが可能な半導体装置を提供する。

【解決手段】表面を有する絶縁膜III上のヒューズ配線F1と、ヒューズ配線F1上の層間絶縁層II1,II2,PIと、層間絶縁層II1,II2,PIの内部に位置する、ヒューズ配線F1と平面視において重ならない領域に形成された電極部PDとを備える。上記ヒューズ配線F1の真上のうち少なくとも一部の第1の領域において、層間絶縁層II1,II2,PIの厚みが、第1の領域以外の第2の領域における層間絶縁層II1,II2,PIの厚みより薄くなるようにトリミング開口部LTCが形成される。トリミング開口部LTCの内側において側壁および底面の少なくとも一部を覆うアルミニウム薄膜部SALを備える。アルミニウム薄膜部SALは、側壁の少なくとも一部から、底面より上側において上記表面に沿う方向に連なる。

(もっと読む)

半導体ダイ上にフィーチャをめっきするためのヒューズバス

【課題】半導体ダイ上に相互接続部又はボンドパッドなどのフィーチャ構造を電気めっきする方法を提供する。

【解決手段】方法は半導体基板の上方に複数のヒューズ(208)を形成する工程と、半導体基板の上方の複数の相互接続層(400〜408)と、該複数の相互接続層の上面の複数の相互接続パッド(502)とを形成する工程と、を含む。シールリング(202)が、半導体基板(302)と、前記複数の相互接続パッド(502)と、前記複数のヒューズ(208,320)とに形成された能動回路を包囲する。各ヒューズ(208,320)は、対応する相互接続パッド(502)とシールリング(202)とに電気的に接続される。各ヒューズ(208)が導通状態にあるとき、該ヒューズは対応する相互接続パッド(502)をシールリング(202)に電気的に接続する。

(もっと読む)

半導体デバイスの電気的にプログラミング可能なヒューズモジュール

【課題】より小型なeヒューズモジュールを提供する。

【解決手段】半導体デバイスが、eヒューズモジュールおよびプログラミング電流生成器を有する。eヒューズモジュールが電気的にプログラミングするeヒューズ素子(226)のアレイを含む。プログラミング電流発生器が、複数の基準トランジスタ素子(M0〜M6)のセットと、基準トランジスタ素子(M0〜M6)を活性化させて、選択された基準電流を生成するセレクタ(254)と、アレイの選択されたeヒューズ素子(226)に、選択された基準電流に応じたプログラミング電流を印加して、eヒューズ素子(226)の抵抗をプログラミングするカレントミラー(M7、M8、M9)とを有する。

(もっと読む)

電気ヒューズ及びその製造方法

【課題】発熱体である抵抗から熱容量の大きいアノード領域への放熱を阻止し、ジュール熱を効率的に抵抗で消費するようにして、電気ヒューズの切断電力の低減化を図る。

【解決手段】絶縁膜5上にポリシリコン層6を形成し、該ポリシリコン層6上の一部に絶縁膜マスクを形成する。次に、該絶縁膜マスク層で被覆された以外のポリシリコン層6上にシリサイド層7を形成する。次にフォトエッチング工程を経てシリサイド層7、ポリシリコン層6をエッチングし、アノード領域1、カソード領域2及びアノード領域1とカソード領域2を接続するリンク領域3からなる電気ヒューズを形成する。電気ヒューズは、アノード領域1とリンク領域3の境界を挟んでリンク領域3方向からアノード領域1の一部に延在する非シリサイド領域を具備する。リンク領域3の非シリサイド領域は高抵抗領域11を構成し、アノード領域1の非シリサイド領域は熱伝導阻止層1bを構成する。

(もっと読む)

電気ヒューズ、半導体装置、及び、電気ヒューズの情報書き込み方法

【課題】 例えば半導体集積回路等のチップに搭載する電気ヒューズの容量を省スペースで効率よく増加させることのできる電気ヒューズ、及び、それを備える半導体装置を提供する。

【解決手段】 電気ヒューズは、第1導電層4と、第1導電層4上に形成された第2導電層5とを有しフィラメント1を備える。そして、フィラメント1は、第1導電層4の状態及び第2導電層5の状態の組み合わせを変えることにより、少なくとも3つの識別可能な抵抗状態が生成されるように構成される。

(もっと読む)

半導体装置

【課題】レーザートリミングの際に半導体基板のダメージを極力抑えながら導電体を溶断することが可能な半導体装置を提供する。

【解決手段】半導体基板10上にLOCOS絶縁膜11を覆う第1の絶縁膜12が形成され、第1の絶縁膜12上には、LOCOS絶縁膜11の平坦部11F上を通って、レーザートリミングにより溶断される導電体20が形成されている。第1の絶縁膜12及び導電体20を覆って、LOCOS絶縁膜11の平坦部11Fと重畳する領域内に凸レンズ状の凸部13Cを有した第2の絶縁膜13が形成されている。レーザートリミングの際、LOCOS絶縁膜11の平坦部11Fの両側の傾斜部11Sでは、レーザー光が半導体基板10の表面に斜めに入射するように反射されるため、半導体基板10のダメージを回避できる。また、第2の絶縁膜13の凸部13Cは、レーザー光を屈折させて導電体20に集光させる。

(もっと読む)

半導体ウェハ、半導体装置、及び半導体装置の製造方法

【課題】ヒューズメモリを利用したトリミングを行う半導体ウェハにおける各半導体チップの回路面積を小さくする。

【解決手段】半導体ウェハ10におけるシリコン基板上は、複数個のチップ領域TARとこの領域TARを囲むスクライブ領域SARとに区画されている。チップ領域TARには、トリミング対象回路11と、ヒューズ素子Fm(m=1〜2M)と、ヒューズ素子Fm(m=1〜2M)が断線状態であるか否かを検出する検出回路としての役割を果たす定電流源IPm(m=1〜2M)及びインバータINm(m=1〜2M)とが形成されている。スクライブ領域SARには、制御信号に応じてON/OFFが切り換わり、ONとなることによりヒューズ素子Fm(m=1〜2M)を断線させる電流を発生するNチャネル電界効果トランジスタTSm(m=1〜2M)がある。

(もっと読む)

半導体記憶装置

【課題】 省スペースによって従来よりも多くの論理回路及びヒューズブロックを設けることができる半導体記憶装置を提供する。

【解決手段】 ヒューズ露出窓を介して外部に露出して互いに並置された複数のヒューズ片を各々が含む複数のヒューズブロックがゲートアレイの近傍において縦列に配置され、電源配線と接地配線とが当該ヒューズ片の並置方向に沿って延在しており、ヒューズブロックの配置のために当該ゲートアレイの近傍のスペースを活用した半導体記憶装置。

(もっと読む)

ヒューズ回路

【課題】ヒューズ回路の2つの出力側にそれぞれ所期の論理値に設定された論理信号出力する。

【解決手段】ヒューズ回路10は、電圧源VDDと、第1主電極、第2主電極、及び制御電極を有する第1及び第2のトランジスタQ11,Q12と、電圧源と第1のトランジスタのソースSとの間に直列に配置される第1の電気ヒューズRf1と、電圧源と第2のトランジスタのソースとの間に直列に配置される第2の電気ヒューズRf2を備える。さらに、第1,第2の電力供給回路Q13,Q14と、第1及び第2のトランジスタのドレインD側から論理値出力を取り出す第1及び第2の出力X,Yを備える。

(もっと読む)

半導体装置及びその駆動方法

【課題】現行プロセスを用いて追加工程なしに製造でき、高い信頼性を有する多値化された電気ヒューズを有する半導体装置を提供する。

【解決手段】第1フィラメントFS1と、第1フィラメントFS1に接続された第2フィラメントFS2とを有する電気ヒューズ素子を有し、第1フィラメントFS1の第2フィラメントFS2との接続端と反対の端部に接続された第1フィラメントFS1と第2フィラメントFS2の直列抵抗を読み出す直列読み出し部RDSとを有する構成とする。

(もっと読む)

半導体装置のトリミング方法、及びトリミング制御回路

【課題】スイッチ素子の製造バラツキを排除し、より均一で確実な溶断が行える半導体装置のトリミング方法、及びトリミング制御回路を提供すること。

【解決手段】電位が異なる第1電源(電源端子c)と第2電源(接地端子d)との間にて直列接続された第1スイッチ素子S1〜S3およびフューズF1〜F3を内蔵した半導体装置101における第1スイッチ素子S1〜S3をオン制御することでフューズF1〜F3に電圧を印加してフューズF1〜F3を溶断する半導体装置101のトリミング方法であって、第1スイッチ素子S1〜S3をターンオン制御することにより、第1電源(電源端子c)からフューズF1〜F3を溶断させない第1電圧値を所定時間印加するステップと、第1電圧値の印加が完了した後、第1電源(電源端子c)からフューズF1〜F3を溶断させる第2電圧値を印加するように切り替えるステップと、を含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】工程を追加せずに、アライメントマークの形成領域におけるゲート電極膜の残渣を低減する。

【解決手段】半導体装置の製造方法は、アライメントマーク10を有する第1領域R1と、抵抗体40が形成される第2領域R2と、ゲート電極15が形成される第3領域R3と、を主面1aに有する基板の主面1a上に、金属材料を含有するゲート電極膜11を形成する工程を有する。更に、第1及び第2領域R1、R2のゲート電極膜11を等方性エッチングにより除去する工程を有する。更に、ゲート電極膜11を除去した第2領域R2と、第3領域R3と、に導電膜(ポリシリコン膜13)を成膜する工程を有する。更に、導電膜を成膜する工程の後に、基板の主面1a上にフォトレジスト膜を形成し、アライメントマーク10をアライメントに用いて所定のパターンをフォトレジスト膜に転写する工程を有する。

(もっと読む)

半導体装置

【課題】面積の増加を抑えつつ、ヒューズ構造体のデータの保持量を増加する。

【解決手段】半導体装置100は、基板(不図示)上に形成されたヒューズ構造体120を含む。ヒューズ構造体120は、第1の配線(122)および第2の配線(124)と、これらを接続するビア123とから構成された電気ヒューズ121と、一端がビア123の側方にビア123に接続して形成された抵抗配線128と、を含む。電気ヒューズ121のビア123は、基板の積層方向において、第1の配線(122)との接続箇所から抵抗配線128との接続箇所までの間に、面内方向の断面積が第2の配線(124)との接続箇所から抵抗配線128との接続箇所までの面内方向の断面積よりも小さい箇所を有する。

(もっと読む)

半導体集積回路

【課題】 ヒューズを用いてデータを記憶する半導体集積回路において、データの誤読み出しを抑制すること。

【解決手段】 半導体集積回路100は、直列に接続された複数のヒューズを含むヒューズ回路10と、複数のヒューズに対し切断用の電流を供給する切断電流供給部30と、複数のヒューズの切断情報を読み出す読み出し部20と、を備える。ヒューズ回路10は、第1端子N1及び第2端子N2を含み、複数のヒューズは、第1端子N1に接続された第1ヒューズF1と、第1ヒューズF1及び第2端子N2に接続された第2ヒューズF2とを含む。読み出し部20は、第1端子N1に接続された第1電源端子Vddと、第2端子N2に接続された第2電源端子Vssと、第1端子N1と第1電源端子Vddとの間(N3)に接続され、切断情報を出力する出力回路40とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】フューズ開口部に起因する水分の浸入における長期信頼性の劣化を防止する半導体装置を提供する。

【解決手段】半導体基板上にフィールド酸化膜を介して抵抗体を設け、抵抗体上に第一の金属配線を設け、第一の金属配線上に吸湿性膜を含む平坦性の良い金属間層間膜を形成する。抵抗体のトリミング用フューズは吸湿性膜を含む金属間層間膜の上に形成することで吸湿性膜の露出を防止する。

(もっと読む)

1 - 20 / 151

[ Back to top ]