Fターム[5F064FF46]の内容

ICの設計・製造(配線設計等) (42,086) | 切り換え、選択 (3,709) | 切り換え、選択実行方法 (1,017) | 電圧、電流の供給、変更 (416) | 端子への入力電圧の変更 (95)

Fターム[5F064FF46]に分類される特許

1 - 20 / 95

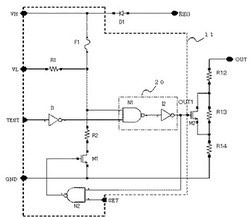

トリミング回路及び調整回路

【課題】ヒューズ素子の仮想切断を可能にすると共に、高電圧又は大電流によるヒューズ溶断の際に、周辺回路を破損する確率も低減できる信頼性の高いトリミング回路を提供する。

【解決手段】ヒューズトリミングを行うための回路であって、トリミングヒューズと、

前記トリミングヒューズに接続されるトリミング用のパッド端子と、仮想切断時に制御信号を入力するテスト端子と、入力端子の一方が前記テスト端子に接続され他方が前記トリミングヒューズに接続され、入力された制御信号に応じた制御信号を出力する制御回路と、を有し、前記トリミングヒューズの切断により、前記制御回路の他方の入力端子がGNDレベルへプルダウンする手段を備えたことを特徴とする。

(もっと読む)

ヒューズ素子読み出し回路

【課題】十分な読み出しマージンを確保し、ヒューズ素子のデータ読み出しの際に誤判定を防止することができるヒューズ素子読み出し回路を提供することを課題とする。

【解決手段】切断済みと未切断とで抵抗値が異なる第1のヒューズ素子(115)と、通常モードと試験モードとで異なる抵抗値を有する第1の抵抗回路(701,702)と、前記第1のヒューズ素子の抵抗値及び前記第1の抵抗回路の抵抗値に応じた読み出し電圧を出力する読み出し電圧出力回路(101)とを有することを特徴とするヒューズ素子読み出し回路が提供される。

(もっと読む)

抵抗変化素子及びそのプログラミング方法

【課題】誤書き込み、及び誤動作を防止し、高信頼化、及び高密度化が可能な抵抗変化素子の提供。

【解決手段】第一の電極(201)と、抵抗変化膜(202)と、第二の電極(203)と、中間絶縁膜(204)と、制御電極(205)と、をこの順に積層した積層構造を備え、前記抵抗変化層(202)と前記中間絶縁膜(204)が直接接していない。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体集積回路装置

【課題】過電圧がLSIの電源端子に印加されたことを確認できるようにする。

【解決手段】半導体集積回路装置(10)は、内部回路(11)と、上記内部回路に電源電圧を供給するための電源端子(15,16)とを含む。このとき、上記内部回路の電源電圧として想定されるレベルを越える電圧(過電圧)が上記電源端子に印加された事実を記録するための過電圧印加情報記録回路(12)を設ける。過電圧印加情報記録回路には、過電圧が上記電源端子に印加された事実が記録されているため、それに基づいて、過電圧がLSIの電源端子に印加されたことを確認することができる。

(もっと読む)

半導体装置

【課題】回路規模が増大化する。

【解決手段】抵抗値が順に小さい値となって直列接続される複数のヒューズを備えるヒューズ部と、前記ヒューズ部の複数のヒューズのそれぞれ一端と、第1の電源電圧との間に接続される複数の選択スイッチと、前記第1の電源電圧から所定の電位差を有するヒューズ溶断用電圧を、前記ヒューズ部の最も小さい抵抗値のヒューズ側に出力するヒューズ溶融電圧出力回路と、ヒューズ溶断時に、前記ヒューズ溶融電圧出力回路が前記ヒューズ溶断用電圧を出力し、前記ヒューズ部の最も大きい抵抗値のヒューズに接続される選択スイッチから最も小さい抵抗値のヒューズに接続される選択スイッチまでを順に導通させる制御回路と、を備える半導体装置。

(もっと読む)

半導体装置および判定方法

【課題】ヒューズの切断または非切断をより正しく判定することが可能な半導体装置および判定方法を提供する。

【解決手段】半導体装置は、ヒューズの切断または非切断の判定を行う半導体装置であって、多数のヒューズと、多数のヒューズのうち切断状態である切断ヒューズの数が所定の切断閾値を超える場合には、ヒューズの切断を示す切断信号を出力し、切断ヒューズの数が切断閾値よりも小さい場合には、ヒューズの非切断を示す非切断信号を出力する判定回路と、を含む。

(もっと読む)

半導体装置

【課題】占有面積の小さな直線状の電気ヒューズを有する半導体装置を提供する。

【解決手段】複数の突出部10fは、電気ヒューズ部10aの中央位置からずれた位置、より具体的には、ビア10dに近くかつビア10eから遠い位置に設けられている。また、複数の突出部20fは、電気ヒューズ部20aの中央位置からずれた位置、より具体的には、ビア20dから遠くかつビア20eに近い位置に設けられている。つまり、突出部10fおよび突出部20fは、ジグザグ状に配置されている。

(もっと読む)

抵抗変化素子の制御方法、および、半導体装置

【課題】抵抗変化素子の閾値電圧のばらつきを生じさせることなく、閾値電圧を低電圧化すること。

【解決手段】印加されたパルス電圧の極性に応じて抵抗値の異なる第1の状態と第2の状態との間で遷移する抵抗変化層と、抵抗変化層の一端に接続された第1の電極と、他端に接続された第2の電極とを備えた抵抗変化素子の制御方法であって、抵抗変化層を第1の状態から前記第2の状態へ遷移させる第1の極性とは逆の第2の極性を有する第1のパルス電圧を、抵抗変化層を第1の状態に保ちつつ、両電極間に印加した後、第1の極性を有する第2のパルス電圧を両電極間に印加して、抵抗変化層を第1の状態から第2の状態へ遷移させる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

半導体デバイスの電気的にプログラミング可能なヒューズモジュール

【課題】より小型なeヒューズモジュールを提供する。

【解決手段】半導体デバイスが、eヒューズモジュールおよびプログラミング電流生成器を有する。eヒューズモジュールが電気的にプログラミングするeヒューズ素子(226)のアレイを含む。プログラミング電流発生器が、複数の基準トランジスタ素子(M0〜M6)のセットと、基準トランジスタ素子(M0〜M6)を活性化させて、選択された基準電流を生成するセレクタ(254)と、アレイの選択されたeヒューズ素子(226)に、選択された基準電流に応じたプログラミング電流を印加して、eヒューズ素子(226)の抵抗をプログラミングするカレントミラー(M7、M8、M9)とを有する。

(もっと読む)

電気ヒューズ及びその製造方法

【課題】発熱体である抵抗から熱容量の大きいアノード領域への放熱を阻止し、ジュール熱を効率的に抵抗で消費するようにして、電気ヒューズの切断電力の低減化を図る。

【解決手段】絶縁膜5上にポリシリコン層6を形成し、該ポリシリコン層6上の一部に絶縁膜マスクを形成する。次に、該絶縁膜マスク層で被覆された以外のポリシリコン層6上にシリサイド層7を形成する。次にフォトエッチング工程を経てシリサイド層7、ポリシリコン層6をエッチングし、アノード領域1、カソード領域2及びアノード領域1とカソード領域2を接続するリンク領域3からなる電気ヒューズを形成する。電気ヒューズは、アノード領域1とリンク領域3の境界を挟んでリンク領域3方向からアノード領域1の一部に延在する非シリサイド領域を具備する。リンク領域3の非シリサイド領域は高抵抗領域11を構成し、アノード領域1の非シリサイド領域は熱伝導阻止層1bを構成する。

(もっと読む)

半導体ウェハ、半導体装置、及び半導体装置の製造方法

【課題】ヒューズメモリを利用したトリミングを行う半導体ウェハにおける各半導体チップの回路面積を小さくする。

【解決手段】半導体ウェハ10におけるシリコン基板上は、複数個のチップ領域TARとこの領域TARを囲むスクライブ領域SARとに区画されている。チップ領域TARには、トリミング対象回路11と、ヒューズ素子Fm(m=1〜2M)と、ヒューズ素子Fm(m=1〜2M)が断線状態であるか否かを検出する検出回路としての役割を果たす定電流源IPm(m=1〜2M)及びインバータINm(m=1〜2M)とが形成されている。スクライブ領域SARには、制御信号に応じてON/OFFが切り換わり、ONとなることによりヒューズ素子Fm(m=1〜2M)を断線させる電流を発生するNチャネル電界効果トランジスタTSm(m=1〜2M)がある。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チップ面積を増大させることなく、針ずれに起因する誤測定や誤検査を防止することができる、半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、内部回路と、内部回路と電気的に接続されるとともに、検査装置に接続された複数の探針がそれぞれ接触する複数のパッドを備える。少なくとも2つのパッド2a、2bの間に、当該2つのパッド2a、2bを電気的に接続するとともに、所定の電流を印加することにより、恒久的に、電気的に切断されるヒューズ素子4が設けられる。パッド2a、2bの間の抵抗値を測定することで、針ずれの有無を検知することができる。その後、ヒューズ素子を切断し、内部回路の検査が実施される。

(もっと読む)

不揮発プログラマブルロジックスイッチ

【課題】 誤動作を防ぐとともに、サイズが小さい不揮発プログラマブルロジックスイッチを提供すること。

【解決手段】 本発明の実施形態による不揮発プログラマブルロジックスイッチは、制御ゲートが第1の配線に接続され、第1のソースドレイン端が第2の配線に接続され、電荷を蓄積する膜を有する第1のメモリセルトランジスタと、制御ゲートが前記第1の配線に接続され、第3のソースドレイン端が前記第1のメモリセルトランジスタの第2のソースドレイン端に接続され、第4のソースドレイン端が第3の配線に接続され、電荷を蓄積する膜を有する第2のメモリセルトランジスタと、前記第1のメモリセルトランジスタの前記第2のソースドレイン端と前記第2のメモリセルトランジスタの前記第3のソースドレイン端にゲート電極が接続されたパストランジスタと、前記パストランジスタのウェルに基板電圧を印加する第1の基板電極を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】レイアウト面積の増大を抑制しつつ、容量を拡張することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルに複数のアンチヒューズ素子F1、F2を設け、各アンチヒューズ素子F1、F2の電界効果トランジスタのゲートを互いに接続することで、アンチヒューズ素子F1、F2の一端をノードAに共通に接続し、メモリセルを多値化する。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bとを有する。駆動対象の記憶素子21に対して、電極215Aと電極215Bとの間に所定の閾値以上の電圧V1を印加して、半導体層212Nと半導体層213Nとの間の領域にそれらの半導体層同士を電気的に繋ぐ導電パスであるフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

半導体装置

【課題】ゲート電極へのチャージアップの有無を解析する手法を用いても、書き込まれた情報を解析することができないようにするアンチヒューズをメモリ素子として有する半導体装置を提供する。

【解決手段】基板10は第1導電型、例えばp型の半導体基板(例えばシリコン基板)である。アンチヒューズは、ゲート電極120及び第2導電型拡散層130を有している。第2導電型拡散層130は基板10に形成されており、例えばn型である。第1コンタクト122はゲート電極120に接続している。第2コンタクト142は第1コンタクト122と同一層に形成されており、基板10のうち第2導電型拡散層130が形成されていない領域に接続している。第2コンタクト142は第1コンタクト122に隣接している。

(もっと読む)

半導体装置

【課題】アンチヒューズにおいて、電極へのチャージアップの有無を解析する手法を用いても、書き込まれた情報を解析することができないようにする。

【解決手段】アンチヒューズ12は、ゲート絶縁膜、ゲート電極114、及び第1拡散層116を有している。第2拡散層126は、素子分離膜102を介して第1拡散層116と離間しており、第1拡散層116と同一導電型を有している。ゲート配線124はゲート電極114と一体として形成されており、素子分離膜102上を延伸している。共通コンタクト220は、ゲート配線124と第2拡散層126を接続している。そしてゲート電極114は、第1拡散層116と同一導電型の不純物が導入された半導体、例えばポリシリコンにより形成されている。また第2拡散層126は、共通コンタクト220のみに接続している。

(もっと読む)

1 - 20 / 95

[ Back to top ]