Fターム[5F064GG05]の内容

ICの設計・製造(配線設計等) (42,086) | 製造プロセス技術 (798) | 結晶成長、エピタキシャル成長 (57)

Fターム[5F064GG05]に分類される特許

1 - 20 / 57

半導体装置

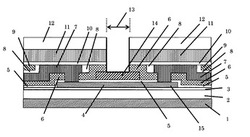

【課題】ヒューズ開口部からの水分侵入による電特異常及び配線腐食を防止する半導体装置を提供する。

【解決手段】シリコン基板1上に絶縁膜2とゲート酸化膜3を設け、ゲート酸化膜2上の一部にヒューズ配線4の両端にヒューズ端子15を有するヒューズを設ける。ヒューズを構成するヒューズ配線4の上方には酸化膜5を介して窒化膜14が形成された凸領域があり、ヒューズ端子15は第1金属配線7と電気的に接続している。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体装置およびその製造方法

【課題】トリミングヒューズの上の絶縁膜が、トリミングヒューズの機能を高めるために適正な状態を維持することが可能な半導体装置を提供する。

【解決手段】表面を有する絶縁膜III上のヒューズ配線F1と、ヒューズ配線F1上の層間絶縁層II1,II2,PIと、層間絶縁層II1,II2,PIの内部に位置する、ヒューズ配線F1と平面視において重ならない領域に形成された電極部PDとを備える。上記ヒューズ配線F1の真上のうち少なくとも一部の第1の領域において、層間絶縁層II1,II2,PIの厚みが、第1の領域以外の第2の領域における層間絶縁層II1,II2,PIの厚みより薄くなるようにトリミング開口部LTCが形成される。トリミング開口部LTCの内側において側壁および底面の少なくとも一部を覆うアルミニウム薄膜部SALを備える。アルミニウム薄膜部SALは、側壁の少なくとも一部から、底面より上側において上記表面に沿う方向に連なる。

(もっと読む)

半導体装置および試験方法

【課題】より小さな単位に切り離しも可能なマルチコア半導装置において、前記より小さな単位に切り離した場合に相互接続配線を伝って生じる可能性のある水の侵入を阻止する。

【解決手段】半導体装置は、素子領域を有する半導体基板と、前記素子領域に形成され、第1の開口部を有する内側シールリングと、前記素子領域に形成され、第2の開口部を有する外側シールリングと、前記半導体基板上に形成された、各々配線層を含む複数の層間絶縁膜を積層した積層体よりなる多層配線構造と、前記多層配線構造に含まれる第1の層間絶縁膜とその上の第2の層間絶縁膜の間に形成された耐湿膜と、前記耐湿膜の下側および上側のいずれか一方である第1の側を延在し、前記第1の開口部を通過する第1の部分と、前記耐湿膜の下側および上側の他方である第2の側を延在し、前記第2の開口部を通過する第2の部分と、前記第1の部分と前記第2の部分とを、前記耐湿膜を貫通して接続するビアプラグとを含む配線パターンと、を有する。

(もっと読む)

不揮発プログラマブルロジックスイッチ

【課題】 誤動作を防ぐとともに、サイズが小さい不揮発プログラマブルロジックスイッチを提供すること。

【解決手段】 本発明の実施形態による不揮発プログラマブルロジックスイッチは、制御ゲートが第1の配線に接続され、第1のソースドレイン端が第2の配線に接続され、電荷を蓄積する膜を有する第1のメモリセルトランジスタと、制御ゲートが前記第1の配線に接続され、第3のソースドレイン端が前記第1のメモリセルトランジスタの第2のソースドレイン端に接続され、第4のソースドレイン端が第3の配線に接続され、電荷を蓄積する膜を有する第2のメモリセルトランジスタと、前記第1のメモリセルトランジスタの前記第2のソースドレイン端と前記第2のメモリセルトランジスタの前記第3のソースドレイン端にゲート電極が接続されたパストランジスタと、前記パストランジスタのウェルに基板電圧を印加する第1の基板電極を有する。

(もっと読む)

プログラマブルLSI

【課題】低消費電力で、且つ、動的コンフィギュレーションにも対応できる高速なコンフィギュレーションを可能とし、起動するための時間が短いプログラマブルLSIを提供する。

【解決手段】複数のロジックエレメントと、複数のロジックエレメントに入力するためのコンフィギュレーションデータを記憶するメモリエレメントと、を有し、複数のロジックエレメントそれぞれは、コンフィギュレーションメモリを有し、コンフィギュレーションメモリに記憶されたコンフィギュレーションデータに応じて、異なる演算処理を行い、且つ、ロジックエレメント間の電気的接続を変更し、メモリエレメントは、チャネルが酸化物半導体層に形成されるトランジスタと、当該トランジスタがオフ状態となることによってフローティングとなるノードと、を有する記憶素子を用いて構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】フューズ開口部に起因する水分の浸入における長期信頼性の劣化を防止する半導体装置を提供する。

【解決手段】半導体基板上にフィールド酸化膜を介して抵抗体を設け、抵抗体上に第一の金属配線を設け、第一の金属配線上に吸湿性膜を含む平坦性の良い金属間層間膜を形成する。抵抗体のトリミング用フューズは吸湿性膜を含む金属間層間膜の上に形成することで吸湿性膜の露出を防止する。

(もっと読む)

半導体集積回路及びその製造方法

【課題】金属層からなるガードリングで囲まれたトリミング素子形成領域のヒューズ上の保護膜の開口からヒューズ上の層間絶縁膜に浸入した水分等がガードリングに形成されたヒューズ引き出し電極用の開口を通ってデバイス形成領域に浸入することを防止する。

【解決手段】ヒューズ5aを取り囲む第1ガードリング30とその外側の第2ガードリング40に囲まれたヒューズ電極引き出し領域41を形成する。ヒューズ5aと連続し層間絶縁膜6とフィールド酸化膜4の間をヒューズ電極引き出し領域41まで延在するヒューズ電極5と、該ヒューズ電極5と接続する第1ヒューズ引き出し電極7cと、該第1ヒューズ引き出し電極7cと接続する第2ヒューズ引き出し電極9cとを形成し、該第2ヒューズ引き出し電極9cを層間絶縁膜8上に形成された第2ガードリング40を構成する第2電極の開口24を通してデバイス素子形成領域80に引き出す。

(もっと読む)

半導体装置

【課題】トリミングにより分圧比を変更可能で所望の分圧比を得る精度の良いブリーダ抵抗回路を備える半導体装置を提供する。

【解決手段】ブリーダ抵抗回路を2段以上の直列接続した抵抗回路部で構成し、それらの抵抗回路部の抵抗素子として同一材料、同一長さ、同一幅、かつ、同一厚みの基本抵抗配線を少なくとも2本以上接続した形態で形成し、ブリーダ抵抗回路を構成する前基本抵抗配線は半導体装置内の1領域に全て集合して整列配置され、それぞれの抵抗回路部の基本抵抗配線を少なくとも2分割以上されて他の抵抗回路部の基本配線抵抗を挟んで配置されている構成とすることにより、離れて配置された基本抵抗配線の製造ばらつきなどによる抵抗値差を各抵抗回路部に分散させる。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

半導体装置

【課題】レーザートリミングによって除去される金属配線を有した半導体装置において、金属配線の下層の素子分離領域においてクラックの発生を抑止する。

【解決手段】例えばP型の半導体基板10には、N−型の半導体層11と隣接するP+型の素子分離領域12と、それを覆うLOCOS絶縁膜13が形成されている。これらは第1の層間絶縁膜21に覆われている。第1の層間絶縁膜21上には、ヒューズ配線として、並行して延びる金属配線23A,23B,23Cが形成されている。第1の層間絶縁膜21の貫通孔21TH内には、タングステン等からなる高融点金属層22が形成されている。この高融点金属層22は、レーザートリミングの際に生じる余分な熱を吸収するため、第1の層間絶縁膜21にクラックが生じにくくなる。

(もっと読む)

半導体装置

【課題】レーザートリミングによって除去されるポリシリコン層を有した半導体装置において、ポリシリコン層を覆う層間絶縁膜の開口部の広がりを抑止する。

【解決手段】例えばP型の半導体基板10には、N−型の半導体層11と隣接するP+型の素子分離領域12が形成されている。素子分離領域12を覆うLOCOS絶縁膜13上には、ヒューズ配線として複数のポリシリコン層15A,15B,15Cが形成されている。これらのヒューズ配線は層間絶縁膜16に覆われており、層間絶縁膜16に設けられた貫通孔16THには、タングステン等からなる高融点金属層17が形成されている。この高融点金属層17は、レーザートリミングの際に生じる余分な熱を吸収するため、層間絶縁膜16の開口部16Aの広がりを抑えることができる。

(もっと読む)

炭化珪素絶縁ゲート電界効果トランジスタを用いたインバータ回路および論理ゲート回路

【課題】動作速度を高速化できる SiC MISFETで構成された論理ゲート回路デバイスを得る。

【解決手段】nチャネルエンハンスメント型SiC MISFET(22)と、nチャネルデプリーション型SiC MISFET(22、22b)とでインバータ、NAND/NOR論理ゲート回路を構成する。

(もっと読む)

半導体装置の設計方法及び半導体装置の製造方法

【課題】溝内に配線を埋め込む際に層間絶縁膜の表面に深い凹部が生じるのを防止し得る半導体装置の設計方法等を提供する。

【解決手段】単位面積当たりの配線パターンの周囲長の総和を各々の単位領域毎に算出するステップS6と、単位領域内における配線パターンの周囲長の総和が第1の値以上である第1の領域と第2の値以下である第2の領域とを抽出するステップS7,S8と、第1の領域に隣接する第3の領域内に単位面積当たりの周囲長の総和が第3の値である第1のダミーパターンを配置し、第2の領域に隣接する第4の領域内に単位面積当たりの周囲長の総和が第4の値である第2のダミーパターンを配置するステップS9,S10と、第3の領域と第4の領域との間の第5の領域内に単位面積当たりの周囲長の総和が第3の値より小さく、第4の値より大きい第5の値である第3のダミーパターンを配置するステップS11とを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】ヒューズのカットばらつきを防ぐとともに腐食(酸化等も含む)を良好に防ぐ。

【解決手段】半導体装置100は、基板102と、基板102上に形成されたヒューズ配線116と、少なくともヒューズ配線116の側壁を保護するように形成された耐湿性絶縁膜120と、を含む。耐湿性絶縁膜120は、ヒューズ配線116の上面には形成されていないか、またはヒューズ配線116の上面における積層方向の膜厚d1がヒューズ配線116の側壁における積層方向に垂直な方向の膜厚d2よりも薄くなるように形成されている。

(もっと読む)

アンチヒューズ構造体および形成方法

【課題】 アンチヒューズ構造体および形成方法を提供する。

【解決手段】 アンチヒューズ構造体は基板上に配置された複数の並行導電フィンを含み、フィンのそれぞれは第1の端部と第2の端部とを有する。第2の電気導体はフィンの第2の端部に電気的に接続される。絶縁体はフィンの第1の端部を覆い、第1の電気導体は絶縁体上に配置される。第1の電気導体は絶縁体によってフィンの第1の端部から電気的に絶縁される。絶縁体は、第2の電気導体と第1の電気導体との間に所定の電圧を印加したときに絶縁破壊し、それによりフィンを介して第2の電気導体と第1の電気導体との間に途切れない電気接続を形成するのに十分な厚さまで形成される。

(もっと読む)

半導体装置

【課題】ヒューズ用開口部からガードリング外への水分等の伝達をより強固に防止する。

【解決手段】下地絶縁膜3上に第1シリコン膜パターンからなるシリコンヒューズとシリコン配線パターン7が形成されている。第1シリコン膜パターンとは別途形成された第2シリコン膜パターンからなり、上方から見てヒューズ5の周囲を取り囲み、一部分がシリコン配線パターン7上を跨いで下地絶縁膜上に環状に形成されたシリコンガードリング11が形成されている。シリコンガードリング11と交差している部分のシリコン配線パターン7表面にシリコン表面絶縁膜9が形成されている。シリコン配線パターン7とシリコンガードリング11はシリコン表面絶縁膜9により互いに絶縁されている。シリコンガードリング11上に金属材料からなる環状のガードリング17,19,25,27が上方から見てヒューズ5の周囲を取り囲んで形成されている。

(もっと読む)

低電力多重状態電子ヒューズ(eヒューズ)をプログラミング及び再プログラミングするための回路構造体及び方法

【課題】 低電力多重状態の電子ヒューズをプログラミング及び再プログラミングするための回路構造体及び方法を提供する。

【解決手段】 eヒューズのプログラミング/再プログラミング回路の実施形態を開示する。一実施形態において、eヒューズ(150)は、長い低原子拡散抵抗導体層(120)の同じ端部に両側(121、122)上に配置された2つの短い高原子拡散抵抗導体層(110、130)を有する。電圧源(170)を用いて端子(第1の端子=170/161/110、第2の端子=170/162/130、第3の端子=170/163/導体層120の近位端123、及び第4の端子=170/164/導電層120の遠位端124)に印加する電圧の極性及び随意的に大きさを変化させて、長い導体層内の電子の2方向の流れを制御し、これにより長い導体層と短い導体層との界面(125、126)における開路及び/又は短絡の形成を制御する。このような開路及び/又は短絡の形成を用いて異なるプログラミング状態(11、01、10、00)を実現することができる。他の回路構造体の実施形態は、さらに多くのプログラミング状態を可能にするように、付加的な導体層及び付加的な端子を有するeヒューズ(650)を組み込む。さらに、関連したeヒューズのプログラミング及び再プログラミング方法の実施形態を開示する。

(もっと読む)

半導体装置及びその製造方法

【課題】従来よりも少数のLEを用いてより小面積のDFFを構成できる、ビアパターンによって論理を変更可能な半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置の製造方法は、

複数のトランジスタと、これらに接続された第1メタル層とが形成された基板において、第1メタル層の上に、第1ビアパターンを含む第1ビア層を形成する工程と、

第1ビア層の上に第2メタル層、第2ビア層および第3メタル層を形成する工程と、

第3メタル層の上に、第3ビアパターンを含む第3ビア層を形成する工程とを含み、

複数の前記トランジスタによって基本論理素子が構成され、

基本論理素子が、2つのN型トランジスタ及び2つのP型トランジスタ(CS2)と、1つのAOIゲート(AOI)と、2つのインバータ(INV)とを備え、

第1ビアパターンによって基本論理素子の論理を決定し、

第3ビアパターンによって基本論理素子間の配線を決定する。

(もっと読む)

半導体装置

【課題】高価な露光装置や高価なマスクを用いることなく、配線等のピッチを狭くすることができる半導体装置を提供する。

【解決手段】第1の導電パターン42と、第1の導電パターンに隣接して形成された第2の導電パターン42と、第1の導電パターンの所定領域下に形成された第1の導体プラグと、第1の導電パターンの所定領域上に形成された第2の導体プラグ62nと、第2の導電パターンのうちの、第1の導電パターンの所定領域に隣接する所定領域下に形成された第3の導体プラグと、第2の導電パターンの所定領域上に形成された第4の導体プラグ62n+1と、第1の導電パターン42の上方に形成され、第2の導体プラグに接続された第3の導電パターン62と、第2の導電パターンの上方に形成され、第4の導体プラグに接続された第4の導電パターン64とを有し、第4の導体プラグは、第2の導体プラグに対して、ずれた位置に配されている。

(もっと読む)

1 - 20 / 57

[ Back to top ]