Fターム[5F083AD02]の内容

Fターム[5F083AD02]に分類される特許

401 - 416 / 416

半導体記憶装置

【課題】 本発明は、メモリセルから読み出されるデータの判定を正確に行うと共に、消費電力を低減することができる半導体記憶装置を提供することを目的とする。

【解決手段】 半導体基板20上に形成された埋め込み電極30と、埋め込み電極30上に埋め込み絶縁膜40を介して形成された半導体層45と、半導体層45上に絶縁膜60を介して形成された表面電極70と、半導体層45の両端部に所定間隔を空けて形成されたソース領域80及びドレイン領域90と、ソース領域80及びドレイン領域90の間に形成されたフローティングボディ50とを有し、フローティングボディ50にホールが蓄積されているか否かによってデータを記憶することを特徴とする。

(もっと読む)

半導体装置

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

(もっと読む)

半導体記憶装置とその製造方法

【課題】 セルアレイと周辺回路の特性が最適化された半導体記憶装置を提供する。

【解決手段】 半導体記憶装置は、絶縁性基板とこの上に形成された半導体層とを有する半導体素子基体と、前記半導体素子基体に形成されて電気的にフローティングのチャネルボディのキャリア蓄積状態によりデータ記憶を行うセルトランジスタが配列され、各ソース及びドレイン層が一方向に隣接する2セルトランジスタにより共有されるセルアレイと、前記半導体素子基体に形成された、前記セルアレイの周辺回路を構成するロジックトランジスタとを有し、前記セルトランジスタのソース及びドレイン層の少なくとも一部が前記ロジックトランジスタのソース及びドレイン層と異なる厚みをもって形成されている。

(もっと読む)

表示装置及びそれを用いた電子機器

【課題】不揮発性であって、データの追記が可能で、作製工程が増加することがない記憶回路を有する表示装置、表示装置を用いた電子機器の提供を課題とする。

【解決手段】一対の導電層間に有機化合物層が挟まれた簡単な構造の記憶素子からなる記憶回路を有する表示装置を提供する。上記構成を有することにより、不揮発性であって、データの追記が可能で、作製工程が増加することがない記憶回路を有する表示装置を提供することができる。

(もっと読む)

半導体記憶装置

【課題】 情報の読み出し時に、チャネル領域からの多数キャリアの放出による情報の変化と情報の保持時間の短縮を防止し、高速動作の可能な半導体記憶装置を提供する。

【解決手段】 半導体基板3上にチャネル領域4を直立に設け、このチャネル領域4の少なくとも一端にソース/ドレイン層5(6)を設け、チャネル領域4の両側面にゲート絶縁膜7、8を介して第1及び第2のゲート電極9、10を設ける。そして、チャネル領域4に情報の書き込みを行い、その情報の読み出しは、チャネル領域4とソース/ドレイン層5、6間のpn接合を逆方向バイアス状態にしておき、第1及び第2のゲート電極9、10に所定電位を印加することにより両ゲート電極9、10間に流れるトンネル電流量を検知することによって行う。

(もっと読む)

半導体装置の製造方法

【課題】ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】ソース/ドレイン領域の一方になり、かつビット線にもなる第1の不純物拡散層24の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜13が設けられる。キャパシタ絶縁膜13を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

強誘電膜の形成方法、これを利用したキャパシタ及び半導体メモリ素子の製造方法

【課題】 強誘電膜の形成方法、これを利用したキャパシタ及び半導体メモリ素子の製造方法を提供する。

【解決手段】 基板を準備する段階、基板上に非晶質強誘電膜を蒸着する段階、及び非晶質強誘電膜にレーザビームを照射し、非晶質強誘電膜を結晶化する段階を含むことを特徴とする強誘電膜の形成方法であり、該強誘電膜の製造方法を利用して強誘電膜を形成したキャパシタの製造方法を提供し、該キャパシタの製造方法を利用した半導体メモリ素子の製造方法である。よって、強誘電膜を500℃より低い温度で形成でき、強誘電膜の形成時に他部材の熱的損傷を減らすことができる。

(もっと読む)

液晶表示装置

【課題】 消費電力の小さなものを得る。

【解決手段】 前記画素領域の集合である表示領域をx方向に沿った仮想の線を境にして一方の表示領域と他方の表示領域とに区分けられ、一方の表示領域側の各ゲート信号線に走査信号を供給する走査信号駆動回路と他方の表示領域側の各ゲート信号線に走査信号を供給する走査信号駆動回路とが別個に形成され、かつ、一方の表示領域側の各ドレイン信号線と他方の表示領域側の各ドレイン信号線とが分離されているとともに、一方の表示領域側の各ドレイン信号線に映像信号を供給する映像信号駆動回路と他方の表示領域側の各ドレイン信号線に映像信号を供給する映像信号駆動回路とが別個に形成されている。

(もっと読む)

キャパシタと好ましくはプレーナ型のトランジスタとを有する集積回路構造およびその製造方法

プレーナ型であることが好ましいトランジスタ(142)とキャパシタ(144)とを有する集積回路構造(140)が開示されている。キャパシタ(44)の下部電極は、トランジスタ(142)のチャネル領域と共に、1つのSOI基板に配置されている。回路構造(140)は、簡単に製造でき、優れた電子特性を有している。  (もっと読む)

(もっと読む)

キャパシタを含んだ集積回路構造およびその製造方法

特に、トランジスタ(122)(好ましくはFinFET)、および、キャパシタ(124)を備えた集積回路構造(120)を開示する。キャパシタ(124)の下部電極は、SOI基板ないに、トランジスタ(122)のチャネル部に沿って配置されている。これにより、本発明の回路構造(120)は、簡単に製造され、優れた電子特性を有している。  (もっと読む)

(もっと読む)

トランジスタ構造及びその製作方法

トランジスタ構造の少なくとも一部分が実質的に透明であるエンハンスメント・モード電界効果トランジスタである。該トランジスタの一変形形態は、ZnO、SnO2及びIn2O3から選択された実質的に絶縁性で実質的に透明な材料から構成されるチャネル層を含む。実質的に透明な材料から構成されるゲート絶縁体層は、チャネル層/ゲート絶縁体層境界面を形成するようにチャネル層に隣接して配置される。該トランジスタの第2の変形形態は、アニーリングにより生成される実質的に絶縁性のZnO、SnO2及びIn2O3から選択される実質的に透明な材料から構成されるチャネル層を含む。該トランジスタを含む装置、及び該トランジスタを作る方法も開示されている。  (もっと読む)

(もっと読む)

半導体装置、その製造方法及び電子機器

【課題】 スイッチングトランジスタ領域のSi−H結合が安定し、誘電体キャパシタ領域の強誘電体酸化膜に酸素欠損が発生しない半導体装置、その製造方法及びそれを使用した電子機器を提供する。

【解決手段】 ガラス等の基板1上に形成されたポリシリコン薄膜にソースドレイン拡散層4とチャネル領域3が形成され、更に、ゲート絶縁膜5を介してゲート電極6が形成されている。そして、層間絶縁膜8上に水素化窒化シリコン膜11が形成されており、これにより、スイッチング用薄膜トランジスタ7を含む能動素子領域の水素濃度を高く保つことができ、シリコン薄膜におけるSi−H結合が安定する。また、水素化窒化シリコン膜11の上に導電性酸化膜により形成された下部電極12を介して強誘電体膜13を設けることにより、強誘電体容量素子層の酸素濃度を高く保つことができ、強誘電体膜13における酸素欠損の発生を防止できる。

(もっと読む)

集積回路メモリーセル及びその製法

【課題】セルデザインや工程を不必要に複雑化せずにセルサイズを減少させる。

【解決手段】

チャンネル30は、組み合わされた第1電極と第1ソース/ドレーンの半導電性上方延長部を含むことができる。メモリーセルは複数のメモリーセルのアレイを含んでおり、第2電極は複数の電極の中の共通電極である。メモリーセルは、第1電極とデジット線との間に直線導電通路を提供することができ、その通路は垂直トランジスターを通過して延びている。

(もっと読む)

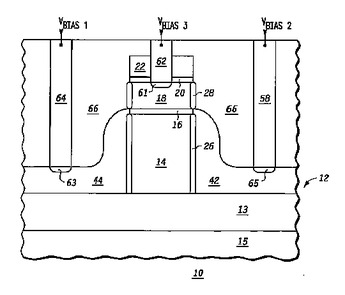

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

完全空乏型シリコン・オン・インシュレータのCMOSロジック

【課題】SOI技術を用いた部分空乏型CMOSデバイスにおける浮遊ボディの不必要な影響を制御可能とする。

【解決手段】シリコン・オン・インシュレータのCMOSメモリデバイスにおいて、引き出し線を含む領域が用いられる。引き出し線を逆方向にバイアスすることで、部分空乏型メモリセルのボディ領域から少数キャリアを取り除く。これにより、ボディ領域を完全空乏化し、浮遊ボディの不必要な影響を抑制する。

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

401 - 416 / 416

[ Back to top ]