Fターム[5F083BS21]の内容

Fターム[5F083BS21]に分類される特許

1 - 18 / 18

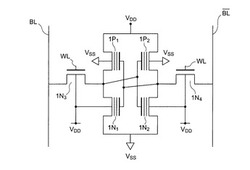

二重フローティングゲート構造を有するトランジスタを備えた不揮発性メモリ

【課題】CMOS製造プロセスに用いることのできる材料を用いかつノイズマージンの広い不揮発性メモリを提供する。

【解決手段】本実施形態の不揮発性メモリによれば、第1および第2のPチャネルトランジスタはそれぞれ第1の半導体領域上に設けられ、第1の半導体領域上に、第1の絶縁膜と、第1のフローティングゲート、第2の絶縁膜、第2のフローティングゲート、第3の絶縁膜、および第1の制御ゲートが、この順序で積層された構造を有し、前記第1および第2のNチャネルトランジスタはそれぞれ第2の半導体領域上に設けられ、前記第2の半導体領域上に、第4の絶縁膜、第3のフローティングゲート、第5の絶縁膜、第4のフローティングゲート、第6の絶縁膜、および第2の制御ゲートがこの順序で積層された積層構造を有している。

(もっと読む)

半導体装置

【課題】高集積なCMOS SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に歪みを導入して半導体装置の特性を向上するとともに、応力印加膜に覆われたゲート配線の断線を防止する。

【解決手段】半導体装置は、第1の素子形成領域101に形成された第1の活性領域104と、第2の素子形成領域102に形成された第2の活性領域105と、第1の活性領域104上から第2の活性領域105上に亘って延伸するゲート配線103と、第1の活性領域104のうちゲート配線103の直下領域に形成された第1のチャネル領域80と、第2の活性領域のうちゲート配線の直下領域に形成された第2のチャネル領域90とを備える。ゲート配線103は、第1の活性領域104上に形成され、引張り応力又は圧縮応力である第1の応力を有する第1の領域164と、第1の領域164よりも緩和された第1の応力を有する第2の領域162とを有している。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】電気的特性の安定した酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供すること。また、結晶性の高い酸化物半導体膜を用いることにより、移動度の向上した半導体装置を提供すること。

【解決手段】表面粗さの低減された絶縁膜上に接して、結晶性を有する酸化物半導体膜を形成することにより、電気的特性の安定した酸化物半導体膜を形成することができる。これにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することができる。さらに、移動度の向上した半導体装置を提供することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、水素または希ガスのいずれかの元素が添加されている。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】高速動作可能な半導体装置を提供する。また、短チャネル効果による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】トランジスタの半導体層に結晶性を有する酸化物半導体を用い、該半導体層にチャネル形成領域とソース領域とドレイン領域を形成する。ソース領域及びドレイン領域は、ゲート電極をマスクとして、半導体層に第15族元素のうち一種類または複数種類の元素を添加する自己整合プロセスにより形成する。ソース領域及びドレイン領域に、ウルツ鉱型の結晶構造を付与することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート幅が互いに異なる第1,第2のMISトランジスタを備えた半導体装置において、第1,第2のMISトランジスタの閾値電圧を、所望の閾値電圧に制御する。

【解決手段】半導体装置は、第1,第2のMISトランジスタを備えた半導体装置である。第1のMISトランジスタは、第1の高誘電率絶縁膜15aを有する第1のゲート絶縁膜15Aと、第1のゲート電極20Aとを備えている。第2のMISトランジスタは、第2の高誘電率絶縁膜15bを有する第2のゲート絶縁膜15Bと、第2のゲート電極20Bとを備えている。第1,第2のゲート絶縁膜は、調整用金属を含む。第1のMISトランジスタの第1のゲート幅W1は、第2のMISトランジスタの第2のゲート幅W2よりも小さい。第1のゲート絶縁膜中における調整用金属の平均調整用金属濃度は、第2のゲート絶縁膜中における調整用金属の平均調整用金属濃度に比べて低い。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体以外の半導体材料が用いられた第1のチャネル形成領域を有する第1のトランジスタ160と、第1のトランジスタ160の上方の、酸化物半導体材料が用いられた第2のチャネル形成領域を有する第2のトランジスタ162と、容量素子164と、を有し、第2のトランジスタ162の第2のソース電極または第2のドレイン電極の一方と、容量素子164の電極の一方とは、電気的に接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】STIの圧縮応力を減少し、チャネル方向とチャネル幅方向の応力を印加することにより、駆動能力を増大したCMOS半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、NMOSFET用活性領域AR1、PMOSFET用活性領域AR2を画定する素子分離溝STと、素子分離溝の下部のみを埋め、その上に凹部を画定する酸化シリコン膜OXと、NMOSFET領域AR1に形成されたNMOSFETと、PMOSFET領域AR2に形成されたPMOSFETと、NMOSFET構造を覆い、NMOSFET用活性領域AR1の周囲における凹部上及びPMOSFET用活性領域AR2のゲート幅方向外側における凹部上に延在して形成された引張応力膜TSFと、PMOSFET構造を覆い、PMOSFET用活性領域AR2のチャネル長方向外側における凹部上に延在して形成された圧縮応力膜CSFとを有する。

(もっと読む)

半導体装置

【課題】メモリセル領域とその周辺回路領域とを含んで構成される半導体装置において、メモリを構成するMOSFETのしきい値のばらつきを小さくできる半導体装置を提供する。

【解決手段】それぞれMOSFETを有してなる複数のメモリセルが形成されたメモリセル領域とMOSFETを回路が形成された周辺回路領域を備えた半導体装置において、メモリセル領域のMOSFETは、周辺回路領域の少なくとも一部のMOSFETとは異なるゲート構造を有し、ゲート絶縁膜及びゲート電極のうちの少なくとも一方の組成が一部のMOSFETとは異なる。

(もっと読む)

半導体装置の製造方法

【課題】MOSFETにおいて、ショートチャネル効果の抑制と移動度向上を両立させることを可能とする。

【解決手段】半導体基板13上にダミーゲート絶縁膜31を介してダミーゲート34を形成する工程と、ダミーゲート34の両側の半導体基板13にソース・ドレイン不純物領域23,24を形成する工程と、ダミーゲート34の両側の半導体基板13上にエクステンション領域25,26を形成する工程と、ダミーゲート34直下のソース側にソース不純物領域23のオーバーラップ領域27を形成する工程と、ダミーゲート34を除去し、該除去領域に露出したダミーゲート絶縁膜31を除去する工程と、除去領域に露出した半導体基板13にリセス形状15を形成する工程と、リセス形状15を形成した半導体基板13上にゲート絶縁膜21とゲート電極22とを順次形成する工程とを備えている。

(もっと読む)

半導体デバイス、半導体デバイスを形成する方法、および集積回路

【課題】 相互に異なるしきい値電圧要件を有する複数のトランジスタを結合するための技法を提供する。

【解決手段】 一態様では、半導体デバイスは、第1および第2のnFET領域と第1および第2のpFET領域とを有する基板と、第1のnFET領域の上の基板上のロジックnFETと、第1のpFET領域の上の基板上のロジックpFETと、第2のnFET領域の上の基板上のSRAM nFETと、第2のpFET領域の上の基板上のSRAM pFETとを含み、そのそれぞれが、高K層の上の金属層を有するゲート・スタックを含む。ロジックnFETゲート・スタックは、高K層から金属層を分離するキャッピング層をさらに含み、キャッピング層は、ロジックpFET、SRAM nFET、およびSRAM pFETのうちの1つまたは複数のしきい値電圧に対してロジックnFETのしきい値電圧をシフトするようにさらに構成される。

(もっと読む)

半導体記憶装置及び当該半導体記憶装置を具備する電子機器

【課題】電源が切れても記憶状態を保持することができ、且つ揮発性メモリと同程度のコストで製造でき、且つ読み出しまたは書き込みの速度が揮発性メモリと同程度の半導体記憶装置を提供することを課題とする。

【解決手段】メモリセルを選択するためのトランジスタと、メモリセルの記憶状態を保持するためのラッチ回路を有し、ラッチ回路を構成するインバーター回路の高電位電源側にはダイオードが接続され、ラッチ回路に容量素子が接続される構成とする。ラッチ回路を具備する半導体記憶装置において、電源が切られた状態でもラッチ回路に接続された容量素子が電位を保持し、そしてラッチ回路を構成するインバーター回路の高電位電源側に接続されたダイオードが容量素子に保持された電荷のリークを防ぐことが出来る。その結果、不揮発性を有する半導体記憶装置を安価に提供することができる。

(もっと読む)

半導体装置

【課題】CPU搭載無線タグのメモリ内のデータの書き換えを可能にした上で、CPUシステムを高速化し、無線タグの通信性能の向上を行う。

【解決手段】CPUが搭載されている無線タグにRFバッテリー付きのSRAMを搭載することで、CPUシステムの高速化による通信性能を向上させる。また、CPU搭載無線タグのメモリ内のデータの書き換えを可能にした。RFバッテリーは、アンテナ回路と、電源部と、蓄電装置と、を有する。SRAMとRFバッテリーとを組み合わせることで、SRAMに不揮発性メモリとしての機能を持たせる。

(もっと読む)

半導体装置、メモリ回路及び機械語プログラム生成装置、並びに半導体装置及びメモリ回路の動作方法

【課題】消費電力の低下が可能な半導体装置及びメモリ回路、並びにこれらの動作方法を提案することを課題とする。

【解決手段】演算回路102と制御回路103とを具備する演算処理回路101と、ROM105とRAM106とを具備するメモリ回路104とを有し、演算処理回路101とメモリ回路104は、アドレスバス107及びデータバス108を介して接続され、ROM105は、演算処理回路101を用いて実行される機械語プログラムのデータが格納されており、RAM106は、複数のバンクを有し、機械語プログラムが実行した際の処理データが、複数のスタックに分割されて複数のバンクに格納され、複数のバンクに格納される複数のスタックにおいて、機械語プログラム終了まで使用されないスタックが省かれ、連続したスタックが同一のバンクに書き込まれるように、機械語プログラムに基づいて演算処理回路が動作する。

(もっと読む)

半導体集積回路

【課題】集積回路内では、それぞれの回路の事情により最適なゲート長とゲート酸化膜厚としきい値電圧があることになる。これらの回路を同一基板上に集積する半導体集積回路では、それぞれの回路の最適な値にするために製造工程が複雑化し、結果として歩留まりの低下、製造日数の増加に伴い製造コストの上昇をもたらす。

【解決手段】論理回路には高低2種類のしきい値のトランジスタを用い、メモリセルには高しきい値電圧と同じしきい値電圧のトランジスタにより構成し、入出力回路は上記の高しきい値電圧と同じチャネルの不純物濃度でゲート酸化膜厚を厚くしたトランジスタを用いて構成する。

(もっと読む)

半導体集積回路装置

【課題】 本発明によれば、リーク電流の発生が抑制された半導体集積回路装置及びその製造方法を提供することができる。

【解決手段】 半導体基板上に第1のゲート絶縁膜を介して形成された第1のゲート電極と、前記半導体基板内に前記第1のゲート電極に対して自己整合的に形成された第1の不純物拡散領域と、前記第1の不純物領域に接続されたコンタクトと、前記半導体基板上に第2のゲート絶縁膜を介して形成された第2のゲート電極と、前記半導体基板内に前記ゲート電極に対して自己整合的に形成された第2の不純物拡散領域と、前記第2のゲート電極と前記第2の不純物拡散領域とに共通に接続されたシェアドコンタクトと、を有する半導体集積回路装置において、前記第2のゲート絶縁膜の誘電率は、前記第1のゲート絶縁膜の誘電率に比べて大きいことを特徴とする半導体集積回路装置。

(もっと読む)

1 - 18 / 18

[ Back to top ]