Fターム[5F083BS27]の内容

Fターム[5F083BS27]の下位に属するFターム

拡散層ゲート (1)

Fターム[5F083BS27]に分類される特許

621 - 629 / 629

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

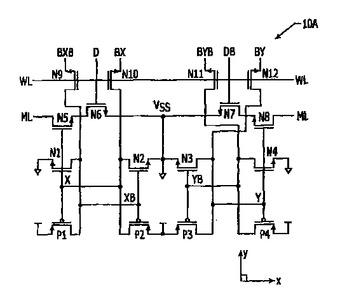

改良されたレイアウトのSRAMメモリセル

本発明は、二つのインバータと複数のスイッチを備えたSRAMメモリセルであって、SRAMセルがN/Pシャント能力を提供する技術において製造され、インバータの入力が少なくとも一対のビットライン(BLa、BLa/;BLb、BLb/)に前記スイッチの二つを介して接続されており、前記スイッチが信号ワードライン(WLa、WLb)によって制御され、各インバータが第1導電性タイプの第1トランジスタ(MN0、MN1)と第2導電性タイプの第2トランジスタ(MP0、MP1)を備え、そして、各スイッチが第1導電性タイプの少なくとも第3トランジスタ(MN2、MN3)を備えるSRAMメモリセルであって、インバータにおける第2導電性タイプの二つのトランジスタ(MP0、MP1)がメモリセルの二つの対向端部領域にそれぞれ配置されていることを特徴とするSRAMメモリセルを提案する。  (もっと読む)

(もっと読む)

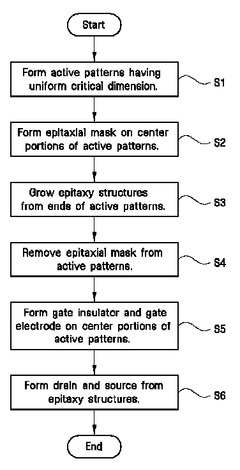

均一な臨界寸法のアクティブパターンで形成されたマルチゲートトランジスタ及びその製造方法

本発明は、均一な臨界寸法のアクティブパターンで構成されたマルチゲートトランジスタの製造方法を提供する。本発明はまた、均一な臨界寸法のアクティブパターンを具備するマルチゲートトランジスタを提供する。マルチゲートトランジスタの製造方法は先に少なくとも一つのアクティブパターンを形成する。以後、前記アクティブパターンの露出した領域から少なくとも一つのエピタキシ構造を成長させる。続いて、前記アクティブパターンの少なくとも2個の面にチャネル領域を形成する。  (もっと読む)

(もっと読む)

放射線耐性のあるSRAMビット

1つの入力と1つの出力を有する第1インバータと、1つの入力と1つの出力を有する第2インバータとを備える集積回路における放射線耐性のあるSRAM装置。第1抵抗は、第1インバータの出力と第2インバータの入力との間に接続される。第2抵抗は、第2インバータの出力と第1インバータの入力との間に接続される。第1書き込みトランジスタは、第1インバータの出力と接続され、書き込み制御信号の第1セットのソースと接続されるゲートを有する。第2書き込みトランジスタは、第2インバータの出力と接続され、書き込み制御信号の第2セットのソースと接続されるゲートを有する。最後にパストランジスタは第1及び第2インバータのいずれか1つの出力と接続されるゲートを有する。  (もっと読む)

(もっと読む)

セルフタイミング回路を有する半導体メモリ

半導体メモリのセルフタイミング回路(61)において、第1の状態に設定されたセルフタイミング用ダミーメモリセル(SDMC11、12)及び第1の状態と反対の第2の状態に設定された負荷用ダミーメモリセル(LDMC11、12)を有するダミービット線(XDBL1)と、第3の状態に設定されたセルフタイミング用ダミーメモリセル(SDMC21、22)及び前記第3の状態と同一の第4の状態に設定された負荷用ダミーメモリセル(LDMC21、22)を有するダミービット線(XDBL2)と、ダミービット線(XDBL1、XDBL2)の電位の変化速度の差に対応する期間だけ遅延させて、セルフタイミング信号(SLF)を出力するタイミング制御回路(62)とを備える。 (もっと読む)

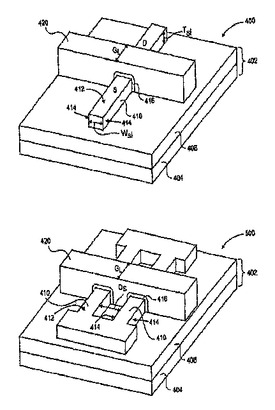

増大されたセル比を有する6トランジスタFINFET型CMOSスタティックRAMセル

本発明に係るCMOSスタティックRAMセルは、2つのアクセスデバイスであり、各々のアクセスデバイスが単一のフィンを有する3ゲートトランジスタから成るところの2つのアクセスデバイス;2つのプルアップデバイスであり、各々のプルアップデバイスが単一のフィンを有する3ゲートトランジスタから成るところの2つのプルアップデバイス;及び2つのプルダウンデバイスであり、各々のプルダウンデバイスが複数のフィンを有する3ゲートトランジスタから成るところの2つのプルダウンデバイスを有する。さらに、2つのフィンを有する3ゲートトランジスタを備えたCMOSスタティックRAMセルの製造方法が提供される。  (もっと読む)

(もっと読む)

小さいフットプリントおよび効率的なレイアウトアスペクト比を有するターナリ検索機能付きメモリ(TCAM)セル

スケーラビリティを高める効率的なレイアウトアスペクト比および極めて小さいレイアウトフットプリントサイズを有するターナリCAMセルが提供される。また、セルは、ビット線、データ線、マッチ線に対する高い歩留りの相互接続を容易にする高度の対称性も有している。16TターナリCAMセルは、セルの第1の側に隣接して延びる第1および第2の対のアクセストランジスタと、セルの第2の側に隣接して延びる第1および第2の対の交差結合インバータとを有している。また、4T比較回路の第1及び第2の半分部位も設けられている。4T比較回路の第1の半分部位は、第1の対のアクセストランジスタと第1の対の交差結合インバータとの間で延びるように位置されている。同様に、4T比較回路の第2の半分部位は、第2の対のアクセストランジスタと第2の対の交差結合インバータとの間で延びるように位置されている。

(もっと読む)

(もっと読む)

並列相補型FinFETの対を有する集積回路構造体及び該形成方法

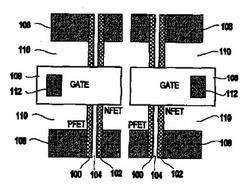

【課題】 従来の単一のFinFETのスペースに2またはそれ以上のFinFETを形成すること。

【解決手段】 相補的フィン型電界効果トランジスタ(FinFET)を用いる集積回路構造体のための方法および構造体を開示する。本発明は、第1フィン(100)を含む第1型FinFETと、第1フィン(100)に並列に延在する第2フィン(102)を含む第2型FinFETを含む。また、本発明は、第1型FinFETおよび第2型FinFETのソース/ドレイン領域(130)の間に配置される絶縁体フィンを含む。第1型FinFETと第2型FinFETとの間隔が1個のフィンの幅とほぼ等しくなるように、絶縁体フィンは、第1フィン(100)および第2フィン(102)とほぼ同じ寸法の幅にされる。また、本発明は、第1型FinFETおよび第2型FinFETのチャネル領域を覆うように形成された共通ゲート(106)を含む。ゲート(106)は、第1型FinFETに隣接する第1不純物ドーピング領域と、第2型FinFETに隣接する第2不純物ドーピング領域とを含む。第1不純物ドーピング領域と第2不純物ドーピング領域の差異が、ゲートに、第1型FinFETと第2型FinFETとの差異に関係した異なる仕事関数を与える。第1フィン(100)および第2フィン(102)はほぼ同じ幅である。

(もっと読む)

半導体装置及びその製造方法

【課題】 より優れたソフトエラー耐性を有するSOI基板を用いた高信頼性のCMOS・SRAMセルを備える半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 SOI基板の表面半導体層上にゲート絶縁膜を介して形成されたゲート電極と、該ゲート電極の両側の表面半導体層に形成された第1導電型ソース/ドレイン領域とから構成される半導体装置であって、前記第1導電型ソース/ドレイン領域の双方又は一方に接して第2導電型引出拡散層が形成され、少なくとも前記第1導電型ソース/ドレイン領域上から第2導電型引出拡散層上にわたってシリサイド層が形成されており、シリサイド層に接地電位が与えられてなる半導体装置。

(もっと読む)

621 - 629 / 629

[ Back to top ]