Fターム[5F083BS40]の内容

Fターム[5F083BS40]の下位に属するFターム

Fターム[5F083BS40]に分類される特許

21 - 39 / 39

半導体装置の製造方法

【課題】 所望のVthが異なる複数種類のMOSFETに対してVthを選択的に制御することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体基板40上の複数種類のMOSFET(Tr1−Trn)を形成する領域に、二酸化シリコンを含む第1ゲート絶縁膜45と、金属酸化物を含む第2ゲート絶縁膜46を形成する工程と、第1ゲート絶縁膜45及び第2ゲート絶縁膜46上にポリシリコンを含むゲート電極47を形成する工程とを有する。この方法は更に、ゲート電極47の形成後、複数種類のMOSFET(Tr1−Trn)のうち、1種類以上のMOSFET(Trn)の温度を、他の種類のMOSFET(Tr1−Tr3)の温度と異ならせるように熱処理する工程を有する。

(もっと読む)

半導体装置およびその製造方法、ならびにその半導体装置を用いた集積半導体装置および不揮発性半導体記憶装置

【課題】絶縁ゲート型電界効果トランジスタにおいて低電圧下で急峻なスイッチング特性を有する半導体素子を提供する。

【解決手段】大規模集積回路に用いられているプレーナ型のロジック回路用MOSFETにおいて、ドレイン拡散層電極のなかに、ダイオード素子と抵抗素子が並列配置されるように形成することで、低電圧であってもゲート電圧変化に対してドレイン電流が急峻な変化を示す高性能トランジスタが実現できる。

(もっと読む)

半導体装置

【課題】メモリセル領域とその周辺回路領域とを含んで構成される半導体装置において、メモリを構成するMOSFETのしきい値のばらつきを小さくできる半導体装置を提供する。

【解決手段】それぞれMOSFETを有してなる複数のメモリセルが形成されたメモリセル領域とMOSFETを回路が形成された周辺回路領域を備えた半導体装置において、メモリセル領域のMOSFETは、周辺回路領域の少なくとも一部のMOSFETとは異なるゲート構造を有し、ゲート絶縁膜及びゲート電極のうちの少なくとも一方の組成が一部のMOSFETとは異なる。

(もっと読む)

半導体装置の製造方法

【課題】MOSFETにおいて、ショートチャネル効果の抑制と移動度向上を両立させることを可能とする。

【解決手段】半導体基板13上にダミーゲート絶縁膜31を介してダミーゲート34を形成する工程と、ダミーゲート34の両側の半導体基板13にソース・ドレイン不純物領域23,24を形成する工程と、ダミーゲート34の両側の半導体基板13上にエクステンション領域25,26を形成する工程と、ダミーゲート34直下のソース側にソース不純物領域23のオーバーラップ領域27を形成する工程と、ダミーゲート34を除去し、該除去領域に露出したダミーゲート絶縁膜31を除去する工程と、除去領域に露出した半導体基板13にリセス形状15を形成する工程と、リセス形状15を形成した半導体基板13上にゲート絶縁膜21とゲート電極22とを順次形成する工程とを備えている。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】製造コスト増加を抑制することができるSRAM型半導体記憶装置の提供。

【解決手段】データを記憶する記憶回路と、第1アクセストランジスタと第2アクセストランジスタとを備え、データの読み出しと書き込みを制御するアクセス制御回路と、記憶回路とアクセス制御回路とに接地電圧を供給する接地電圧供給領域と、第1アクセストランジスタに備えられた第1ゲート電極と第1アクセストランジスタに備えられた第2ゲート電極とを接続する第2導電型のポリシリコン8とを具備するSRAM型半導体記憶装置を構成する。その接地電圧供給領域15は、接地電圧を供給する接地電圧供給コンタクトに接続され、一部分が第2導電型の半導体22であり一部分を除く他の部分が第1導電型の半導体15で構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】Si(110)基板に形成され、シリサイド化されたソース/ドレイン領域を有するNチャネルMISFETにおいて、オフリーク電流を抑制する。

【解決手段】半導体装置は、面方位が(110)面たる主表面を有する半導体基板上に形成され、ソース領域およびドレイン領域の少なくとも一方の上部にニッケルまたはニッケル合金のシリサイドを有するNチャネルMISFET(Metal Insulator Semiconductor Field Effect Transistor)を備える。そのうちチャネル幅が400nm未満であるNチャネルMISFETは、チャネル長方向を結晶方位<100>となるようにレイアウトする。

(もっと読む)

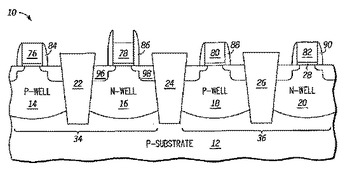

半導体デバイス構造

【課題】 スタティック・ランダム・アクセス・メモリ(SRAM)デバイスで使用するための半導体デバイス構造およびこのような半導体デバイス構造を形成するための方法を提供することにある。

【解決手段】 この半導体デバイス構造は、第1の半導体領域と第2の半導体領域との間に配置された誘電体領域と、第1の半導体領域と第2の半導体領域との間に伸びるゲート導体構造とを含む。ゲート導体構造は、第1の半導体領域の上に重なる第1の側壁を有する。このデバイス構造は、第1の半導体領域の全域に伸びる電気的接続ブリッジをさらに含む。電気的接続ブリッジは、第1の半導体領域内の不純物ドープ領域をゲート導体構造の第1の側壁に電気的に接続する一部分を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の素子形成面に大きな段差が生じる場合でも、段差部底面の所望の部位に不純物を導入し得る半導体装置およびその製造方法を提供する。

【解決手段】同一極性の2つのMOS トランジスタがそれぞれのソース・ドレイン領域の各一方の不純物拡散層を共有するとともに2つのMOS トランジスタの各ポリシリコンゲート同士が隣り合う部分を有する半導体装置において、2つのMOS トランジスタの各ポリシリコンゲート11の高さが150nm 以上、隣り合うポリシリコンゲート相互の間隔が87nm 以下であって、2つのMOS トランジスタで共有される不純物拡散層151は、拡散層表面部の不純物濃度が拡散層内部で最も高い。

(もっと読む)

半導体素子の製造方法

【課題】SRAMなどの半導体素子を製造するために適用可能なポリシリコン層の製造方法を提供する。

【解決手段】本発明の半導体素子の製造方法は、半導体基板上に半導体素子内に含まれるトランジスタを形成するステップ、前記トランジスタ上に絶縁層を形成するステップ、前記絶縁層を選択的に除去してコンタクトホールを形成し、前記コンタクトホールを介して前記トランジスタの所定領域を露出させるステップ、前記コンタクトホール内にシリコン層を形成するステップ、前記絶縁層及び前記シリコン層上に金属層を形成するステップ、前記シリコン層及び前記金属層を熱処理して金属シリサイド層を形成するステップ、前記金属層を除去するステップ、前記絶縁層及び前記金属シリサイド層上に非晶質シリコン層を形成するステップ、及び前記非晶質シリコン層を熱処理してポリシリコン層を形成するステップを含む。

(もっと読む)

垂直配向ナノロッドを持つ低リークDRAMメモリセルとその製造方法

半導体メモリストレージセルにおいてリーク電流を減らすための方法と構造が記載される。垂直配向ナノロッド(403)が、アクセストランジスタ(400)のチャネル領域で使用され得る。ナノロッドの直径は、アクセストランジスタのチャネル領域内の電子バンドギャップエネルギーの増加を引き起こすために十分小さくすることができ、これはオフ状態でのチャネルリーク電流を制限するように機能し得る。様々な実施形態では、アクセストランジスタは両面キャパシタ(425)に電気的に結合し得る。本発明の実施形態に従うメモリデバイス、およびそのようなデバイスを含むシステムもまた開示される。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MOSFETにおいて、ショートチャネル効果の抑制と移動度向上を両立させることを可能とする。

【解決手段】第1半導体面11とこの面につながる面であり、かつ該第1半導体面に対して傾斜を有する第2半導体面12を有する半導体領域10と、第1、第2半導体面11、12上にゲート絶縁膜21を介して第1、第2半導体面11、12境界上に設けられたゲート電極22と、ゲート絶縁膜21を挟んでゲート電極22と第1半導体面11内でオーバーラップするように半導体領域10に形成されたソース不純物領域23と、少なくとも第2半導体面12直下の半導体領域10に設けられたドレイン不純物領域24と、ドレイン不純物領域24と半導体領域10との接合界面Jdが、ソース不純物領域23と半導体領域10との接合界面Jsより、第1、第2半導体面11、12の境界Bに近い状態に形成されている。

(もっと読む)

半導体装置

【課題】nチャネルMISトランジスタとpチャネルMISトランジスタとが接続するドレイン領域において、トランジスタ特性を悪化させる不具合が生じないCMOSデバイスを含む半導体装置を提供する。

【解決手段】基板11上の半導体領域に形成されたソース領域18Aと、ドレイン領域17Aとを有するnチャネルMISトランジスタと、半導体領域に形成されたソース領域18Bと、ドレイン領域17Bと有するpチャネルMISトランジスタとを具備する。ドレイン領域17Aと17Bとが接続するように配置されると共に、同一の材料で形成され、ソース領域18A,18Bの少なくともいずれかがドレイン領域17A,17Bと異なる材料で形成されている。

(もっと読む)

半導体装置

【課題】SRAMのメモリセルにおいて、トランジスタのデバイス特性における非対称性不良を抑制する。

【解決手段】半導体装置は、入出力がクロスカップルするように接続され、ドライバトランジスタ及びロードトランジスタよりなるインバータの対と、インバータの対の各出力に接続されたアクセストランジスタの対とを含むSRAMセルを備える。インバータの対を構成するドライブトランジスタの対及びロードトランジスタの対、並びにアクセストランジスタの対のうちの少なくと1つのトランジスタの対は、ソースからドレインへの向きが互いに同じ向きになるように配置されている。

(もっと読む)

3次元半導体デバイスの製造方法

【課題】 半導体素子の回路が形成されているSi層上に絶縁膜を形成し、該絶縁膜上に多結晶もしくは非晶質Si層を積層し、これをレーザー照射及び走査により(再)結晶化して、ここに別の半導体素子の回路を形成し、これらの回路を接続する3次元半導体デバイスの製造方法に関する。レーザー(再)結晶化Si層の結晶性を改良することにより、現在のICに適した性能を与える。

【解決手段】絶縁膜17,26をCMPにより平坦化する;多結晶又は非晶質Si層22,32を積層し、エネルギーが照射面積当たり10J/cm2以上の固体連続波レーザーにより照射・走査行う;その直後にレーザーアニールを行う。

(もっと読む)

低減されたゲートドーピングを用いる半導体構造体及び同構造体を形成する方法

半導体構造体10は記憶領域34と論理領域36とを有する基板12を含む。第一のp型デバイスは記憶領域34に形成され、第二のp型デバイスは論理領域36に形成される。第一のp型デバイスの半導体ゲートの少なくとも一部は第二のp型デバイスの半導体ゲートの少なくとも一部よりもより低いp型ドーパント濃度を有する。第一及び第二のp型デバイスの半導体ゲートの各々は、ゼロではないp型ドーパント濃度を有する。  (もっと読む)

(もっと読む)

半導体集積回路装置の製造方法

【課題】DRAMとロジックLSIとを混載した半導体集積回路装置の製造において、DRAMのコンタクトホール形成プロセス(ゲート−SAC)とロジックLSIのコンタクトホール形成プロセス(L−SAC)とを両立させる。

【解決手段】DRAMのメモリセル選択用MISFETのゲート電極8A(ワード線WL)を形成する領域の上部のみに窒化シリコン膜9を残し、ロジックLSIを構成するMISFETのゲート電極8Bの上部およびSRAMのメモリセルを構成するゲート電極8C、8Dの上部には窒化シリコン膜9を残さないようにする。その後、上記窒化シリコン膜9とフォトレジスト膜10とをマスクに用いたエッチングで、ゲート電極8A(ワード線WL)およびゲート電極8B〜8Dを同時にパターン形成する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】DRAMとロジックLSIとを混載した半導体集積回路装置の製造プロセスを簡略化する。

【解決手段】ロジックLSIを構成するMISFETのゲート電極7B、ソース、ドレイン(n+型半導体領域16)のそれぞれの表面と、後の工程でDRAMのメモリセル選択用MISFETのゲート電極となる多結晶シリコン膜7の表面とにCoシリサイド層20を同時に形成することによって、製造プロセスの簡略化を実現する。

(もっと読む)

CMOSデバイスにおいて自己整合デュアル・フルシリサイド・ゲートを形成するための方法

【課題】 位置ずれの問題を克服する新規のデュアルFUSIゲート形成プロセスを提供する。

【解決手段】 1つのリソグラフィ段階しか必要としない、CMOSデバイスにおいて自己整合デュアル・フルシリサイド・ゲートを形成する方法であり、本方法は、半導体基板(252)の中の第1のウェル領域(253)、第1のウェル領域(253)の中の第1のソース/ドレイン・シリサイド・エリア(266)、及び第1のソース/ドレイン・シリサイド・エリア(266)から分離された第1のタイプのゲート(263)を有する第1のタイプの半導体デバイス(270)を形成するステップと、半導体基板(252)の中の第2のウェル領域(254)、第2のウェル領域(254)の中の第2のソース/ドレイン・シリサイド・エリア(256)、及び第2のソース/ドレイン・シリサイド・エリア(256)から分離された第2のタイプのゲート(258)を有する第2のタイプの半導体デバイス(280)を形成するステップと、第2のタイプの半導体デバイス(280)の上に第1の金属層(218)を選択的に形成するステップと、第2のタイプのゲート(258)のみの上で第1のフルシリサイド(FUSI)ゲート形成を行うステップと、第1及び第2のタイプの半導体デバイス(270、280)の上に第2の金属層(275)を堆積させるステップと、第1のタイプのゲート(263)のみの上で第2のFUSIゲート形成を行うステップとを含む。

(もっと読む)

スタティック・ランダム・アクセス・メモリ

【課題】スタティックノイズマージンの低下を抑制すること。

【解決手段】ビット線18はロードトランジスタ14のウェルに接続され、反転ビット線18はロードトランジスタ13のウェルに接続されている。ノードN1は“L”レベル、ノードN2は“H”レベルである。リード時にはビット線18,19は“H”レベルにプリチャージされる。ワード線17が“H”レベルに立ち上がるとドライバトランジスタ11にカラム電流が流れる。ビット線18の電位が“L”レベルに変化すると、同時にロードトランジスタ14のウェル電位が“L”レベルに変化するのでロードトランジスタ14の電流駆動能力が向上し、ノードN1の電位がノイズ等によって上昇しドライバトランジスタ12が僅かにオン動作してもノードN2の電位が“H”レベルから低下するのが抑制されビット線18,19の電位差読み取りが可能になりリード時の誤動作が低減される。

(もっと読む)

21 - 39 / 39

[ Back to top ]