Fターム[5F083BS41]の内容

Fターム[5F083BS41]に分類される特許

1 - 20 / 23

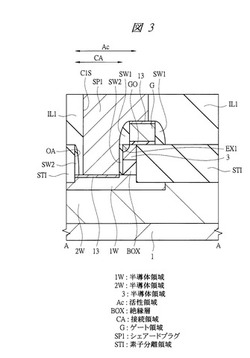

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

二重フローティングゲート構造を有するトランジスタを備えた不揮発性メモリ

【課題】CMOS製造プロセスに用いることのできる材料を用いかつノイズマージンの広い不揮発性メモリを提供する。

【解決手段】本実施形態の不揮発性メモリによれば、第1および第2のPチャネルトランジスタはそれぞれ第1の半導体領域上に設けられ、第1の半導体領域上に、第1の絶縁膜と、第1のフローティングゲート、第2の絶縁膜、第2のフローティングゲート、第3の絶縁膜、および第1の制御ゲートが、この順序で積層された構造を有し、前記第1および第2のNチャネルトランジスタはそれぞれ第2の半導体領域上に設けられ、前記第2の半導体領域上に、第4の絶縁膜、第3のフローティングゲート、第5の絶縁膜、第4のフローティングゲート、第6の絶縁膜、および第2の制御ゲートがこの順序で積層された積層構造を有している。

(もっと読む)

半導体装置

【課題】高集積なCMOS SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

表示装置

【課題】電気泳動表示装置で、書き込み回数のさらに少ないアクティブマトリクス型の電

気泳動表示装置を提供することを課題とする。

【解決手段】複数の画素電極上に、複数の帯電粒子を内蔵したマイクロカプセルを配置し

、前記画素電極の電位により前記帯電粒子を制御することによって明暗を表示することを

特徴とした表示装置において、前記画素電極への映像信号の再書き込み動作を、画素に表

示する映像が変化する場合に行うことにより、書き込み回数を低減する。

(もっと読む)

半導体装置およびその製造方法

【課題】活性領域における上記プラグと、活性領域の外部における上記プラグとの双方を有する、微細化された半導体装置において、枠付け絶縁膜を確実に形成し、かつ導電性などの機能を最適化することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に形成される活性領域と、平面視における活性領域の周辺に形成されるゲート接続領域と、活性領域上に形成される複数の第1のトランジスタTGに挟まれる領域に形成される、第1のトランジスタTGと第1のトランジスタTGよりも上側の層とを電気的に接続するための第1の接続層CTと、ゲート接続領域上に形成される第2のトランジスタTGと、第2のトランジスタTGよりも上側の層とを電気的に接続するための第2の接続層とを備えている。上記第1の接続層CTには第1の導電部PP1aと第2の導電部PP2aとを含み、第2の接続層SNCには第3の導電部PP2bを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】オフ電流を増加させることなく電源供給配線の電気抵抗を下降させることが可能な、TFTを有する半導体装置を提供することである。

【解決手段】表面を有する絶縁膜II4と、絶縁膜II4の表面上に形成され、かつチャネル領域TP2と、チャネル領域TP2を挟む1対のソース/ドレイン領域TP1,TP4とを含む半導体層と、ソース領域TP1に電源を供給するための電源供給配線TP1とを備えている。上記絶縁膜II4の表面には凹部TRが形成されている。上記電源供給配線TP1は、半導体層と同一の層から形成された層を含み、かつ絶縁膜II4の表面上に形成された第1の部分TP1Aと、凹部内に形成された第2の部分TP1Bとを有している。上記第2の部分TP1Bの底面全体が絶縁体II4で覆われている。

(もっと読む)

電界効果トランジスタを備える半導体素子及びその製造方法

【課題】電界効果トランジスタを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成され、第1活性領域の上面及び向き合う側面を経て伸張する第1ゲート電極を有する第1導電型の第1FET素子と、前記第1FET素子上に形成された層間絶縁膜と、前記層間絶縁膜上に形成され、第2活性領域の上面及び向き合う側面を経て伸張する第2ゲート電極を有する第2導電型の第2FET素子と、を備える。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、窒素、リン、又は砒素など15族元素のいずれか一以上の元素が添加されている。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】SRAMは高速で省電力なメモリであるが、携帯機器等で使用するにはさらなる省電力化が求められる。

【解決手段】オフ抵抗が極めて高いトランジスタを書き込みトランジスタとし、書き込みトランジスタのドレインを書き込みビット線に、ソースをCMOSインバータの入力に接続し、読み出しトランジスタのドレインを読み出しビット線に、ソースをCMOSインバータの出力に接続したメモリセルを用いる。書き込みトランジスタのソースにはキャパシタを意図的に設けてもよいが、CMOSインバータのゲート容量あるいはCMOSインバータの正極や負極との間の寄生容量等を用いることもできる。データの保持はこれらのキャパシタに蓄積された電荷によっておこなえるため、CMOSインバータの電源間の電位差を0とできる。このため、CMOSインバータの正負極間を流れるリーク電流がなくなり、消費電力を低減できる。

(もっと読む)

ノードコンタクト構造体

【課題】ノードコンタクト構造体を有する半導体素子と、その製造方法を提供する。

【解決手段】半導体基板の上に形成されソース/ドレイン領域を有するバルクモストランジスタを備える。該バルクモストランジスタ上に層間絶縁膜が形成され、該層間絶縁膜上にソース/ドレイン領域を有する薄膜トランジスタが形成される。該バルクモストランジスタのソース/ドレイン領域上に半導体プラグが形成され、該半導体プラグは該層間絶縁膜の少なくとも一部を介して延長される。該薄膜トランジスタのソース/ドレイン領域及び該半導体プラグは金属プラグと接触し、該金属プラグは該層間絶縁膜の少なくとも一部を介して延長される。該半導体プラグ及び該金属プラグは多層のプラグを構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート幅が互いに異なる第1,第2のMISトランジスタを備えた半導体装置において、第1,第2のMISトランジスタの閾値電圧を、所望の閾値電圧に制御する。

【解決手段】半導体装置は、第1,第2のMISトランジスタを備えた半導体装置である。第1のMISトランジスタは、第1の高誘電率絶縁膜15aを有する第1のゲート絶縁膜15Aと、第1のゲート電極20Aとを備えている。第2のMISトランジスタは、第2の高誘電率絶縁膜15bを有する第2のゲート絶縁膜15Bと、第2のゲート電極20Bとを備えている。第1,第2のゲート絶縁膜は、調整用金属を含む。第1のMISトランジスタの第1のゲート幅W1は、第2のMISトランジスタの第2のゲート幅W2よりも小さい。第1のゲート絶縁膜中における調整用金属の平均調整用金属濃度は、第2のゲート絶縁膜中における調整用金属の平均調整用金属濃度に比べて低い。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた高性能な半導体装置を提供する。

【解決手段】基板上に酸化物半導体層を形成し、酸化物半導体層上に第1の導電層を形成し、第1の導電層上に第2の導電層を形成し、第2の導電層をエッチングすることで、第1のパターンを形成し、第1のパターンを酸化することにより膨張させ、膨張後の第1のパターンをマスクとして第1の導電層をエッチングすることで、ソース電極及びドレイン電極となる第2のパターンを形成し、膨張後の第1のパターン及び第2のパターン及び酸化物半導体層を覆うゲート絶縁層を形成し、ゲート絶縁層上にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のソース電極および第1のドレイン電極と、第1のソース電極および第1のドレイン電極と電気的に接続され、酸化物半導体材料が用いられている第1のチャネル形成領域と、第1のチャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、を有する第1のトランジスタと、容量素子と、を有し、第1のトランジスタの第1のソース電極または第1のドレイン電極の一方と、容量素子の電極の一方とは、電気的に接続された半導体装置である。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体以外の半導体材料が用いられた第1のチャネル形成領域を有する第1のトランジスタ160と、第1のトランジスタ160の上方の、酸化物半導体材料が用いられた第2のチャネル形成領域を有する第2のトランジスタ162と、容量素子164と、を有し、第2のトランジスタ162の第2のソース電極または第2のドレイン電極の一方と、容量素子164の電極の一方とは、電気的に接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】高誘電率膜をゲート絶縁膜として用いたCISトランジスタの信頼性を向上する。

【解決手段】基板1の主面には、素子分離領域2によって互いに絶縁分離されたpMISトランジスタの活性領域およびnMISトランジスタの活性領域が設けられている。素子分離領域2に係るようにnMISトランジスタの活性領域上にnMISトランジスタのゲート絶縁膜を構成するハフニウム系酸化膜5が設けられており、そのハフニウム系酸化膜5と素子分離領域2上で接触し、pMISトランジスタの活性領域上にハフニウム系酸化膜5と異なる材料から構成されるpMISトランジスタのゲート絶縁膜を構成するハフニウム系酸化膜9が設けられている。

(もっと読む)

ゲート型横型サイリスタベースランダムアクセスメモリ(GLTRAM)セルを製造するための方法

【解決手段】

ゲート型横型サイリスタベースメモリデバイス(gltram)を製造するための方法が提供される。半導体層(406)内の第1の伝導性タイプの第1、第2、第3及び第4のウエル領域(463,471,486,493)を含む半導体層(406)が設けられる。第1のゲート構造(465/408)は第1のウエル領域(463)上にあり、第2のゲート構造(475/408)は第2のウエル領域(471)上にあり、第3のゲート構造(485/408)は第3のウエル領域(486)上にあり且つ第2のゲート構造(475/408)と一体であり、第4のゲート構造(495/408)は第4のウエル領域(493)上に配置される。第1のゲート構造(465/408)の第1の側壁(414)及び第2乃至第4のゲート構造(475/408,485/408,495/408)の側壁(412,413,416,417,418,419)に隣接して側壁スペーサ(469)が形成される。また、第1のウエル領域(463)の部分(468)及び第1のゲート構造(465/408)の部分を覆う絶縁スペーサブロック(467)が形成される。絶縁スペーサブロック(467)は第1のゲート構造(465/408)の第2の側壁(415)に隣接する。第1のゲート構造(465/408)に隣接して第1のソース領域(472)が形成され、第1及び第2のゲート構造(465/408,475/408)の間に共通ドレイン/カソード領域(474/464)が形成され、第3のゲート構造(485/408)に隣接して第2のソース領域(482)が形成され、第3及び第4のゲート構造(485/408,495/408)の間に共通ドレイン/ソース領域(484/492)が形成され、第4のゲート構造(495/408)に隣接してドレイン領域(494)が形成される。第1のゲート構造(465/408)に隣接する絶縁スペーサブロック(467)の下で第1のウエル領域(463)内に延在する第1のベース領域(468)が形成され、第1のベース領域(468)に隣接する第1のウエル領域(463)内に延在するアノード領域(466)が第1のウエル領域(463)内に形成される。

(もっと読む)

半導体デバイス、半導体デバイスを形成する方法、および集積回路

【課題】 相互に異なるしきい値電圧要件を有する複数のトランジスタを結合するための技法を提供する。

【解決手段】 一態様では、半導体デバイスは、第1および第2のnFET領域と第1および第2のpFET領域とを有する基板と、第1のnFET領域の上の基板上のロジックnFETと、第1のpFET領域の上の基板上のロジックpFETと、第2のnFET領域の上の基板上のSRAM nFETと、第2のpFET領域の上の基板上のSRAM pFETとを含み、そのそれぞれが、高K層の上の金属層を有するゲート・スタックを含む。ロジックnFETゲート・スタックは、高K層から金属層を分離するキャッピング層をさらに含み、キャッピング層は、ロジックpFET、SRAM nFET、およびSRAM pFETのうちの1つまたは複数のしきい値電圧に対してロジックnFETのしきい値電圧をシフトするようにさらに構成される。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】バリッドビットにおける無効化処理において、電源投入時に無効化処理を行うことができる半導体記憶装置を提供する。

【解決手段】第1のトランジスタと、第2のトランジスタと、を有する第1のインバータ回路と、入力部が前記第1のインバータ回路の出力部に接続され、出力部が前記第1のインバータの入力部に接続され、第3のトランジスタと、第4のトランジスタと、を有する第2のインバータ回路と、を含む初期化用メモリセルを有し、第3のトランジスタのしきい値電圧の絶対値は、第1のトランジスタのしきい値電圧の絶対値より低い構成とする。

(もっと読む)

自己整合したソース/ドレイン領域を有するフィン型電界効果トランジスタ・デバイスおよびその形成方法

【課題】改良されたフィン電界効果トランジスタ(FinFET)デバイスと、その製造方法とを提供する。

【解決手段】1つの側面において、電界効果トランジスタ・デバイスを製造する方法は次のステップを含む。その上にシリコン層を有する基板が準備される。そのシリコン層においてフィン・リソグラフィー・ハードマスクがパターニングされる。フィン・リソグラフィー・ハードマスクの中央部分の上にダミー・ゲート構造が置かれる。ダミー・ゲート構造の周りにフィラー層が堆積させられる。フィン・リソグラフィー・ハードマスクの中央部分の上を中心として、フィラー層にトレンチを形成するためにダミー・ゲート構造が除去され、それはデバイスのフィン領域をデバイスのソース領域およびドレイン領域から区別する。フィン領域内のフィン・リソグラフィー・ハードマスクは、シリコン層に複数のフィンをエッチングするために使用される。フィンの上にゲート・スタックを形成するためにトレンチはゲート材料で満たされる。デバイスのソース領域およびドレイン領域を形成するためにフィラー層が除去され、ソース領域およびドレイン領域は無傷であってゲート・スタックと自己整合させられている。

(もっと読む)

1 - 20 / 23

[ Back to top ]