Fターム[5F083BS48]の内容

Fターム[5F083BS48]に分類される特許

1 - 20 / 117

半導体装置及び半導体装置の製造方法

【課題】新規な構造のコンタクトプラグを有する半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板と、半導体基板に形成され、ソース/ドレイン領域及びゲート電極を有するトランジスタと、トランジスタのソース/ドレイン領域及びゲート電極を覆う絶縁膜と、絶縁膜中に形成され、トランジスタのソース/ドレイン領域またはゲート電極に接されるコンタクトプラグとを有し、コンタクトプラグは、絶縁膜の厚さ方向に延在しトランジスタのソース/ドレイン領域またはゲート電極に接触する柱部と、柱部の上部から絶縁膜の表面と平行な方向に張り出し上面が平坦化された鍔部とを有する。

(もっと読む)

半導体装置

【課題】高集積なCMOS SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に歪みを導入して半導体装置の特性を向上するとともに、応力印加膜に覆われたゲート配線の断線を防止する。

【解決手段】半導体装置は、第1の素子形成領域101に形成された第1の活性領域104と、第2の素子形成領域102に形成された第2の活性領域105と、第1の活性領域104上から第2の活性領域105上に亘って延伸するゲート配線103と、第1の活性領域104のうちゲート配線103の直下領域に形成された第1のチャネル領域80と、第2の活性領域のうちゲート配線の直下領域に形成された第2のチャネル領域90とを備える。ゲート配線103は、第1の活性領域104上に形成され、引張り応力又は圧縮応力である第1の応力を有する第1の領域164と、第1の領域164よりも緩和された第1の応力を有する第2の領域162とを有している。

(もっと読む)

半導体集積回路装置

【課題】本発明は、従来のSRAMメモリセルでは、Pウエル領域の基板へのコンタクトをとるために、拡散層の形を鍵状に曲げる必要があった。このため、対称性が悪く微細化が困難であるという問題があった。

【解決手段】SRAMセルを構成するインバータが形成されたPウエル領域PW1、PW2が2つに分割されてNウエル領域NW1の両側に配置され、トランジスタを形成する拡散層に曲がりがなく、配置方向が、ウエル境界線やビット線に平行に走るように形成される。アレイの途中には、基板への電源を供給するための領域が、メモリセル32ローあるいは、64ロー毎に、ワード線と平行に形成される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置

【課題】SRAMメモリセルに関し、ペアトランジスタのデバイス特性における非対称性不良を抑制可能なレイアウト構造を提供する。

【解決手段】第1のメモリセルは、単位配置領域1aのインバータ41と単位配置領域1bのインバータ81とを用いて構成されている。インバータ41,81はともに単位配置領域1a,1b内において下側に構成されている。よって、ロードトランジスタ対TP1,TP2およびドライブトランジスタ対TN1,TN2対では、ソースからドレインへの向きは同じである。また、ゲート電極31,71は直線状に延びており、屈曲部を有しない。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極同士の間の突合わせ部を挟むように形成されたコンタクトプラグ同士が、当該突合わせ部の絶縁膜内に形成されたボイドを介してショートすることを防ぐ。

【解決手段】ゲート電極G2およびG5間の突合わせ部において対向するサイドウォールSW上には、ライナー絶縁膜6と層間絶縁膜7が形成されている。サイドウォールSW同士の間において、サイドウォールSWの側壁にそれぞれ形成されたライナー絶縁膜6を接触させてサイドウォールSW間を閉塞させることにより、層間絶縁膜7とライナー絶縁膜6の内部にボイドが発生することを防ぐ。

(もっと読む)

半導体記憶装置

【課題】SRAMのゲート配線形成にあたって、ゲート形状を複雑に変形させることなく転写及び加工マージンを確保する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1組及び第2組のドライバトランジスタ11、ロードトランジスタ12及びアクセストランジスタ13とを備えたメモリセルが半導体基板上に2次元配列されたメモリセルアレーと、複数のワードラインと、複数のビットラインと、第1組のドライバトランジスタ11とロードトランジスタ12とを接続し、直線状の側辺を有する長方形状の第1ゲート配線3aと、アクセストランジスタ13と接続され、直線状の側辺を有する長方形状の第2ゲート配線3cと、第1ゲート配線3aと、第2組のドライバトランジスタ11とロードトランジスタ12とを接続する第1コネクタ5aと、第2ゲート配線3cとワードラインとを接続する第2コネクタ5cとを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】動作マージンの向上に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体基板上に、互いのゲート電極が接続されて配置される第1トランジスタ(P2)と、前記第1トランジスタと異なる導電型を有する第2トランジスタ(N4)とを具備し、前記第1トランジスタのゲート電極は、第1不純物と前記第1不純物の拡散を抑制する第2不純物とを含有し、前記第1不純物の濃度ピーク(PE1)は、前記第2不純物の濃度ピーク(PE2)よりも浅い位置に形成されている。

(もっと読む)

ノードコンタクト構造体

【課題】ノードコンタクト構造体を有する半導体素子と、その製造方法を提供する。

【解決手段】半導体基板の上に形成されソース/ドレイン領域を有するバルクモストランジスタを備える。該バルクモストランジスタ上に層間絶縁膜が形成され、該層間絶縁膜上にソース/ドレイン領域を有する薄膜トランジスタが形成される。該バルクモストランジスタのソース/ドレイン領域上に半導体プラグが形成され、該半導体プラグは該層間絶縁膜の少なくとも一部を介して延長される。該薄膜トランジスタのソース/ドレイン領域及び該半導体プラグは金属プラグと接触し、該金属プラグは該層間絶縁膜の少なくとも一部を介して延長される。該半導体プラグ及び該金属プラグは多層のプラグを構成する。

(もっと読む)

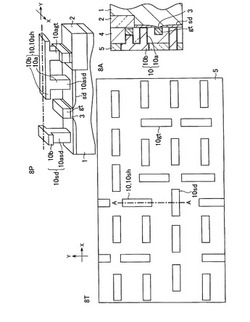

マスタスライス方式メモリセル

【課題】複数種類の回路構成をマスタスライス方式で対応可能なメモリセル専用のマスタスライス方式メモリセルを提供すること。

【解決手段】メモリユニットが2行2列に配置されてメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第3拡散層を備え、各拡散層で並列接続のトランジスタが構成される。第1および第2ワード線は第1〜第3拡散層の両端部外方に配置される。第1〜第3拡散層の第1コンタクト層とゲート層の第2コンタクト層との間、第1コンタクト層と第1/第2ワード線との間に、行方向に沿って第1のメタル配線領域が確保される。第1のメタル配線領域には、第2または第3メタル層の何れかが配線可能である。第1及び第2拡散層、第2及び第3拡散層の間には、列方向に沿って第2のメタル配線領域が確保される。第2のメタル配線領域には第3メタル層が配線可能である。

(もっと読む)

半導体装置の製造方法

【課題】検査コストや解析コスト、製品コストを低減可能な半導体装置の製造方法を提供する。

【解決手段】例えば、ウエハ検査工程(S1003)で、半導体ウエハ上のロジック回路を対象とした電気的検査(ロジック部テスト)(S1003a)と、メモリ回路を対象とした電気的検査(メモリ部テスト)(S1003b)を行い、それぞれの検査結果から得られた故障箇所を複合マップ24上に重ねて表示する。この複合マップ24を用いると、例えば、ロジック故障22とメモリ故障23が併存して分布する領域を判別でき、この領域に対してメモリ故障23に対する詳細解析を優先的に行うことで、特にロジック故障22とメモリ故障23の故障原因が共通であった場合に効率的な詳細解析を行うことが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】集積度が高くリソグラフィーコストが低いn型及びp型FETの積層構造を有した半導体装置を提供すること。

【解決手段】半導体装置100は、半導体基板1上にそれぞれ離隔しつつ列状に形成された第1グループの複数の柱状ゲート電極10と、前記半導体基板1上であって前記第1グループの隣接する柱状ゲート電極10間に形成された第1導電型の第1半導体層12と、前記第1半導体層の上であって前記第1グループの隣接する柱状ゲート電極間に形成された第1絶縁層20と、前記第1絶縁層20の上であって前記第1グループの隣接する柱状ゲート電極10間に形成された前記第1導電型と異なる第2導電型の第2半導体層13とを備え、前記第1半導体層12をチャネルとする前記第1導電型の第1MOSFETが形成され、前記第2半導体層13をチャネルとする前記第2導電型の第2MOSFETが形成されている。

(もっと読む)

半導体メモリ装置及びその製造方法

【課題】半導体メモリ装置及びその製造方法を提供する。

【解決手段】第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、第1ウェル領域は、第2ウェル領域と第3ウェル領域との間に配され、第1ウェル領域は、第1タイプ導電体を含み、第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板;第1ウェル領域に一列に形成され、電源端子を共有する第1プルアップ素子及び第2プルアップ素子;第2ウェル領域に第1プルアップ素子と隣接するように配される第1プルダウン素子;第3ウェル領域に第2プルアップ素子と隣接するように配される第2プルダウン素子;第2ウェル領域に第2プルアップ素子と隣接するように配される第1アクセス素子;第3ウェル領域に第1プルアップ素子と隣接するように形成される第2アクセス素子;を含む半導体メモリ装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性を損なうことなく更なる集積化を実現し得る半導体装置を提供する。

【解決手段】第1のトランジスタL1のゲート電極を含み、第1のコンタクト層48aを介して第2のトランジスタL2のソース/ドレイン拡散層20に電気的に接続される、直線状の第1のゲート配線16aと、第2のトランジスタL2のゲート電極を含み、第2のコンタクト層48bを介して第1のトランジスタのソース/ドレイン拡散層22に電気的に接続される、第1のゲート配線と平行な直線状の第2のゲート配線16bと、第1のゲート配線及び第2のゲート配線を覆うように形成された絶縁膜であって、第1のゲート配線と第2のトランジスタのソース/ドレイン拡散層とを露出し、長辺方向が第1のゲート配線の長手方向である第1の開口部46aが形成された絶縁膜と、第1の開口部内に埋め込まれた第1のコンタクト層とを有している。

(もっと読む)

半導体セル構造物、上記半導体セル構造物を含む半導体装置、及び上記半導体装置を含む半導体モジュール

【課題】所定の整列関係を有する単位セルを含む半導体セル構造物を提供すること。

【解決手段】単位セルは、活性領域14、18、24、28、ゲートパターン32、34、36、38、ダミーパターン42、44、46、48、及び導電パターン94を有する。ゲートパターン32、34、36、38は活性領域14、18、24、28と交差する。ダミーパターン42、44、46、48は単位セルを電気的に接続する。選択された単位セル内のダミーパターン42、44、46、48は、選択された単位セル内のゲートパターン32、34、36、38との間に対角的に配置される。導電パターン94はダミーパターン42、44、46、48と電気的に接続する。これにより、半導体セル構造物は、行及び列に沿って互い突出しない単位セルを有することができる。上述した半導体セル構造物は半導体装置及び半導体モジュールに配置される。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

1 - 20 / 117

[ Back to top ]