Fターム[5F083ER23]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電気的に消去するもの(EEPROM) (2,068) | ブロック消去 (331)

Fターム[5F083ER23]に分類される特許

1 - 20 / 331

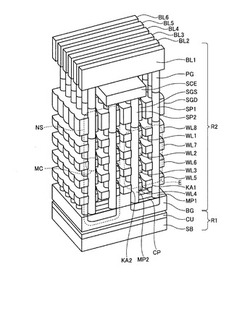

半導体装置および半導体装置の製造方法

【課題】ホールの微細化を図りつつ、ホールとスリットとを一括形成する。

【解決手段】4層分のワード線WL4〜WL1が順次積層されるとともに、ワード線WL4〜WL1にそれぞれ隣接するように4層分のワード線WL5〜WL8が順次積層され、ワード線WL5〜WL8が柱状体MP1にて貫かれるとともに、ワード線WL1〜WL4が柱状体MP2にて貫かれることで、NANDストリングNSが構成され、ワード線WL1〜WL8およびセレクトゲート電極SGD、SGSはロウ方向に沿って幅が周期的に変化されている。

(もっと読む)

半導体記憶装置

【課題】動作の安定性を向上できる半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、複数のメモリセルと、複数のワード線と、複数のビット線と、複数の選択トランジスタと、配線層と、を備える。複数のメモリセルは、第1方向及び第1方向と直交する第2方向にそれぞれ配置される。複数のワード線は、それぞれ第1方向に延在して設けられる。複数のビット線は、それぞれ第2方向に延在し、第1方向及び第2方向と直交する第3方向に複数のワード線と離間して設けられる。複数の選択トランジスタは、複数のストリングにそれぞれ設けられる。配線層は、選択トランジスタのソースと同電位に設けられる。配線層は、第3方向にみて複数のワード線とそれぞれ重なる複数の第1重複部分を有する。配線層のパターンが繰り返される単位領域において、複数の第1重複部分のそれぞれの面積は同じである。

(もっと読む)

不揮発性メモリ装置、不揮発性メモリ装置のプログラム方法、不揮発性メモリ装置を含むメモリシステム

【課題】向上された信頼性を有する不揮発性メモリ装置のプログラム方法が提供される。

【解決手段】本発明のプログラム方法は、第1メモリセルトランジスターの閾値電圧がプログラム状態から移動する傾向を判別する段階と、判別結果に応答して、複数の検証電圧の中で第1検証電圧を選択する段階と、第1メモリセルトランジスターの閾値電圧が変化するように第1メモリセルトランジスターをプログラムする段階と、で構成される。プログラムする段階は第1メモリセルトランジスターの閾値電圧が十分に変化されたかを第1検証電圧を利用して検証する段階を含む。判別する段階は第1メモリセルトランジスターの閾値電圧の第1範囲からの変化を判別する段階を含む。

(もっと読む)

半導体装置の製造方法

【課題】

実施形態は、ゲート配線の抵抗が増大することを防止可能な半導体装置の製造方法を提供する。

【解決手段】

本実施形態の半導体装置の製造方法は、第1領域及び第2領域の半導体素子を形成するために、半導体基板、前記半導体基板上の第1絶縁膜、前記第1絶縁膜上の電荷蓄積層を積層し、所望のトレンチを形成する工程と、前記トレンチに素子分離膜を形成する工程と、前記素子分離膜及び前記電荷蓄積層上にストッパー膜30を形成する工程と、前記第2領域を第2絶縁膜で被膜し、前記第1領域の前記ストッパー膜30と前記素子分離膜をエッチバックする工程と、前記エッチバックされた素子分離膜、前記電荷蓄積層、第2領域の前記ストッパー膜30上に第3絶縁膜を介して配線を形成する工程とを備えることを特徴とする。

(もっと読む)

半導体装置

【課題】

実施形態は、解析が簡便な半導体装置を提供する。

【解決手段】

本実施形態の半導体装置は、内部信号を伝送可能な第1配線101と、第1配線101

と電気的に接続された測定電極100と、測定電極100と隣接するように配置され、内

部信号を計測するときに接地電位VSSが印加され、内部信号を計測する以外のときに所

望の電圧が印加されたダミー電極102,103とを備える。

例えば、測定電極100は、環状に形成されており、ダミー電極は、第1電極102と

第2電極103とを有し、第1電極102は、測定電極100の内側に形成された空間に

隣接するように配置され、第2電極103は、測定電極100の外側に隣接するように配

置される。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】チャネル移動度を向上させた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20上に設けられたメモリトランジスタ40と選択トランジスタ50を有する。メモリトランジスタ40は、導電層41a〜41d、メモリゲート絶縁層43、柱状半導体層44、及び酸化層45を有する。導電層41は、メモリトランジスタ40のゲートとして機能する。メモリゲート絶縁層43は、導電層の側面に接する。半導体層44は、導電層と共にメモリゲート絶縁層43を一方の側面で挟み、半導体基板20に対して垂直方向に延び、メモリトランジスタ40のボディとして機能する。酸化層45は、半導体層44の他方の側面に接する。半導体層44は、シリコンゲルマニウムにて構成される。酸化層45は、酸化シリコンにて構成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルトランジスタに電荷を蓄積する際の電圧を従来よりも自由に設定し得る不揮発性半導体記憶装置を提案する。

【解決手段】不揮発性半導体記憶装置1では、選択メモリセルトランジスタ115に電荷を蓄積させる際、電圧の高い書き込み禁止電圧をP型MOSトランジスタ9bから印加し、電圧の低い書き込み電圧をN型MOSトランジスタ15aから印加して、選択メモリセルトランジスタ115又は非選択メモリセルトランジスタ116へ電圧を印加する役割分担を、P型MOSトランジスタ9b及びN型MOSトランジスタ15aに分けたことで、P型MOSトランジスタ9b及びN型MOSトランジスタ15aそれぞれのゲート電圧やソース電圧を個別に調整でき、最終的にゲート基板間電圧を例えば4[V]等に設定し得る。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

メモリ・デバイス

【課題】より高い性能を実現できるメモリ・デバイスを提供する。

【解決手段】メモリ・デバイスは、複数のセルを書き込み単位としてデータを書き込む不揮発性のメモリ(11)と、コントローラ(12)を含む。コントローラは、ホスト・デバイスからの論理アドレスを割り当てられた書き込みデータをメモリに書き込む要求に対して書き込みデータの分割された部分である書き込みデータ部分をそのサイズを指定して送信することをホスト・デバイスに要求する。コントローラは、書き込みデータに付加的データを付加してメモリに書き込む。書き込みデータ部分は当該書き込みデータ部分および対応する付加的データの和のサイズが書き込み単位のサイズ以下で最大となるように決定されたサイズの整数倍のサイズを有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】高い信頼性を有し且つ安価な不揮発性半導体記憶装置を提供する。

【解決手段】この不揮発性半導体記憶装置において、メモリストリングスは、基板に対して垂直方向に延びる一対の柱状部、及び前記一対の柱状部の下部を連結させるように形成された連結部を有する半導体層と、前記柱状部の側面を取り囲むように形成された電荷蓄積層と、前記柱状部の側面及び前記電荷蓄積層を含む第1の絶縁膜と、前記柱状部の側面及び前記第1の絶縁膜を覆うように形成された第1導電層と、前記連結部の周囲に形成される第2の絶縁膜と、前記連結部に前記ゲート絶縁膜を介して形成される第2導電層とを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】ビット線接続部の微細化を実現する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、p型の半導体基板101と、半導体基板101内に形成され、メモリセルのビット線とセンスアンプ部を接続するビット線接続トランジスタHTkが形成されるp型の第1のPウェル102と、第1のPウェル102を囲み、第1のPウェル102を半導体基板101から電気的に分離するn型の第1のNウェル103と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】データの劣化を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルは、半導体層、電荷蓄積層、及び導電層を備える。半導体層は、半導体基板に対して垂直方向に延び、メモリセルのボディとして機能する。電荷蓄積層は、半導体層の側面に設けられ、電荷を蓄積する。導電層は、半導体層と電荷蓄積層を挟むよう設けられ、メモリセルのゲートとして機能する。制御回路は、第1プログラム動作の後、第2プログラム動作を実行する。第1プログラム動作は、メモリセルのボディに第1電圧を印加し且つメモリセルのゲートに第1電圧よりも大きい第2電圧を印加することによりメモリセルの閾値電圧を正方向に移動させる動作である。第2プログラム動作は、メモリセルのボディをフローティングにし且つメモリセルのゲートに正の第3電圧を印加する動作である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第3のフィン型積層構造Fin1〜Fin3を有する。第1乃至第3のフィン型積層構造Fin1〜Fin3は、第1の方向に積み重ねられる第1及び第2の半導体層Sm1,Sm2を備える。第1及び第2のアシストゲート電極AG1,AG2は、第3の方向に並んで配置され、第3のフィン型積層構造Fin3の第1の方向にある表面上で互いに分断される。第1のアシストゲートトランジスタAGT1は、第1及び第3のフィン型積層構造Fin1,Fin3内に形成され、第2のアシストゲートトランジスタAGT2は、第2及び第3のフィン型積層構造Fin2,Fin3内に形成される。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去動作の実行単位を小さくすると共に正確な読出動作を実現可能な不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、複数のメモリストリング、複数のメモリブロック、複数のソース線、及び制御回路を有する。複数のメモリストリングは、積層された複数のメモリトランジスタを含む。複数のメモリブロックは、複数のメモリストリングを含む。複数のソース線は、複数のメモリストリングそれぞれに接続される。制御回路は、複数のソース線に供給する信号を制御する。複数のメモリストリングは、各々、半導体層、電荷蓄積層、及び導電層を有する。制御回路は、メモリトランジスタに対する動作の種類に基づいて、複数のソース線を電気的に共通接続するか否かを切り替える。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性半導体装置の高集積化を図ることのできる技術を提供する。

【解決手段】スイッチ用nMIS(Qs)のスイッチゲート電極SGと、スイッチ用nMIS(Qs)にワード線に対して交差する方向に沿って隣接するメモリ用nMIS(Qm)のメモリゲート電極MGとの間に、スイッチ用nMIS(Qs)のソース/ドレイン領域SDHとして機能し、同時にメモリ用nMIS(Qm)のドレイン領域Dとして機能する半導体領域を形成し、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)側のソース/ドレイン領域SDHを構成する半導体領域の形状と、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)と反対側(ビット線側)のソース/ドレイン領域SDLを構成する半導体領域の形状とを非対称とする。

(もっと読む)

ダイオードストラッピングを備えた熱アシストフラッシュメモリ

【課題】フラッシュメモリの動作速度及び耐久性を向上させる技術の提供。

【解決手段】メモリが、行及び列を含むメモリセルのアレイを有している。該メモリは、アレイ内の単数又は複数のワード線上の第1の離隔位置のセットに第1のバイアス電圧を印加するとともに、単数又は複数のワード線上の第2の離隔位置のセットに第1のバイアス電圧とは異なる第2のバイアス電圧を印加する、ワード線に結合された回路部を有し、第1の離隔位置のセットにおける位置は、第2の離隔位置のセットの位置の間に介在しており、それにより、第1の離隔位置のセットにおける位置と第2の離隔位置のセットにおける位置との間に、単数又は複数のワード線の加熱をもたらす電流の流れが誘導される。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

不揮発性メモリ装置

【課題】 パストランジスタ間の空間確保が可能な不揮発性メモリ装置を提供する

【解決手段】 不揮発性メモリ装置100が備える行デコーダ120は、パストランジスタ部123_L、123_Rを含む。パストランジスタ部123_L、123_Rは、メモリブロック110の左右に配列される。ブロック選択信号BLKWL1によって共通ゲートを形成するパストランジスタ端Pass TR 0とパストランジスタ端Pass TR 8とは、選択的に活性化される第1駆動信号ラインSI1及び第2駆動信号ラインSI2によって独立して駆動される。互に異なるブロック選択信号BLKWLによって駆動されるパストランジスタは、1つの活性領域の上に形成され得る。これにより、1つの活性領域の上に2つのパストランジスタを形成する場合、パストランジスタ部123_L、123_Rのチャンネル方向の大きさを減らすことができる。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

1 - 20 / 331

[ Back to top ]