Fターム[5F083GA03]の内容

Fターム[5F083GA03]に分類される特許

201 - 220 / 322

半導体装置及びその製造方法

【課題】ビット線及びワード線の抵抗の低い半導体装置、及びその製造方法を提供する。

【解決手段】第1のシリサイド層及び第1のポリシリコン層6を含むビット線BLと、ビット線BL上に形成された基部14a及び基部14aに立設された柱状のボディ部14cを有する第2のシリコン層14と、基部14aに形成されたソースドレイン領域SD1と、ビット線BLの一部を貫通して基板1と第2のシリコン層14を連結する第1のシリコン層13と、ボディ部14cを覆うゲート絶縁膜17を介してボディ部14cを覆うゲート電極18と、ボディ部14c上に形成されてゲート電極18に接続される第2のシリサイド層及び第2のポリシリコン層23を含むワード線WLと、ワード線WLを貫通してボディ部14cの上方に接続されるソースドレイン領域SD2を有する第3のシリコン層34とを具備してなる。

(もっと読む)

半導体記憶装置及びその製造方法

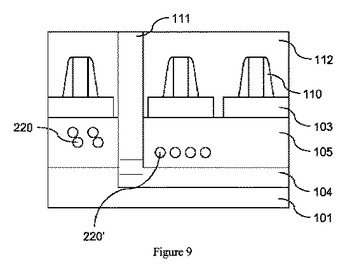

【課題】動作速度が向上し、信頼性の高い不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板101上に所定間隔を空けて形成され、順に積層された第1の絶縁膜102、電荷蓄積層103、金属酸化物を含む第2の絶縁膜104、及び制御ゲート電極105をそれぞれ有する複数のワードラインと、ワードラインの側面及びワードライン間の半導体基板表面を覆う膜厚が15nm以下の第3の絶縁膜110と、互いに隣接ワードラインの制御ゲート電極105間に形成された第4の絶縁膜111と、第3の絶縁膜110及び第4の絶縁膜111に囲まれ、互いに隣接するワードラインの電荷蓄積層間103に位置する空洞部112と、を備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】動作速度を向上させた半導体記憶装置を提供する。

【解決手段】半導体基板1上に形成された複数のワードラインWLと、前記複数のワードラインの両端にそれぞれ1つずつ配置され、隣接するワードラインWL1との間隔L1がワードラインWLの幅L2の3倍以上となる選択トランジスタSTと、ワードラインWL及び選択トランジスタSTの上面を覆うように形成された層間絶縁膜16と、ワードラインWL間に位置し、上部を層間絶縁膜16に覆われた第1の空洞部20と、選択トランジスタSTに隣接するワードラインWL1の選択トランジスタSTに対向する側壁部に形成され、上部が層間絶縁膜16に覆われた第2の空洞部20と、選択トランジスタSTの側壁部に形成され、上部が層間絶縁膜16に覆われた第3の空洞部20と、を備える。

(もっと読む)

埋め込み型トラッピング層によるトランジスタの閾値電圧の調整方法

方法は、電子サブアセンブリの形成について、調整可能な閾値電圧を有する少なくとも1つの第1のトランジスタ(110)を担持する半導体層(103)が絶縁層(102、105)に接合される組み立てステップと、半導体層および第1のトラッピングゾーンが容量結合されるように、第1のトラッピングゾーン(220)が所定の第1の深さで絶縁層に形成される形成ステップであって、前記第1のトラッピングゾーンが、前記第1のトランジスタのチャネルの少なくとも下に延び、かつ前記第1のトラッピングゾーンの外側のトラップの密度より高い密度のトラップを有する形成ステップとを含み、前記第1のトランジスタからの有用な情報はこのトランジスタ内の電荷移動である。具体的な実施形態において、第2のトランジスタのチャネルの少なくとも下に延びる第2のトラッピングゾーンが、第1のトラッピングゾーンに使用されるのとは異なるエネルギーおよび/または用量および/または原子の第2の注入によって形成される。  (もっと読む)

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】異なる配線層間で互いに直交する配線群を接続する際、接続信頼性が高く良好なスペース効率でレイアウト可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、予め設定された配列順で第1配線層に形成されそれぞれY方向(第1の方向)に延伸される複数の第1の配線20と、第2配線層に形成される複数の第2の配線21と、配列順が互いに一致する第1の配線20及び第2の配線21の間を電気的に接続する複数のコンタクト23とを備えている。各々の第2の配線21は、Y方向に直交するX方向(第2の方向)に平行な直線状に規定された隣接する2トラックのうち、一方のトラックに沿って延伸される配線部21aと、他方のトラックに沿って延伸される配線部21bと、2つの配線部21a、21bの間を接続する接続部21cとにより構成され、接続部21cに複数のコンタクト23が形成されている。

(もっと読む)

フラッシュメモリ及びその製造方法

【課題】隣接ワードラインの間をシームレスに埋め込み、セル間干渉が抑制された良好な素子特性を有するフラッシュメモリ及びその製造方法を提供することを目的としている。

【解決手段】フラッシュメモリの隣接ワードライン間を埋め込む絶縁膜としてO3−TEOS膜が埋め込まれており、特にビットライン上の隣接ワードライン間が下地依存性を有するO3−TEOS膜109によってシームレスに埋め込まれていることを特徴としている。

(もっと読む)

不揮発性半導体記憶装置

【課題】YUPIN効果を抑えるようなセルの配置デザインを実現することができ、メモリセルの微細化及び高集積化をはかる。

【解決手段】ストライプ状の素子形成領域11が並列配置され、各々の素子形成領域11に電荷蓄積層12と制御ゲート13を有する不揮発性メモリセルが複数個設けられた不揮発性半導体記憶装置であって、電荷蓄積層12は、互いに異なる素子形成領域11間で隣接するもの同士が、ストライプ方向にずらして配置されている。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】トランジスタの動作時に半導体基板から制御ゲート電極に抜けるリーク電流を低減して閾値のばらつきを低減させる

【解決手段】シリコン基板1は、トレンチ1aに素子分離用絶縁膜2aを埋め込んでSTI2を形成し、活性領域3を分離形成している。シリコン基板1の活性領域3の表面には第1のゲート絶縁膜5、浮遊ゲート電極6、第2のゲート絶縁膜7、制御ゲート電極8が積層形成されたゲート電極MGが設けられている。STI2のトレンチ1aの内壁面には素子分離用絶縁膜2aとの間に5Åの膜厚のアルミナ膜からなる絶縁薄膜4が設けられている。これにより、素子分離用絶縁膜2aがポリシラザンのような塗布型酸化膜を用いた場合でも、不純物に起因した固定電荷を中和してリーク電流の低減を図れる。

(もっと読む)

半導体記憶装置

【課題】分割されたメモリアレイの端部について、ダミーパターンを配置することにより、面積増加要因となってしまう。

【解決手段】分割されたメモリアレイの端部Y1列に構成された回路をメモリセルトランジスタと同形状のブロック選択トランジスタBTで構成する。主ビット線GBと副ビット線LBとの接続部のパターンをメモリセル(Y2,Y3列)と同形状にすることで、パターンを均一にすることができメモリアレイ生成用のダミーパターンを不要とする。

(もっと読む)

半導体装置の製造方法

【課題】隣接するメモリセル間の干渉に起因するメモリセルの誤動作を回避する半導体装置の製造方法を提供する。

【解決手段】本発明の例に関わる半導体装置の製造方法は、半導体基板上に、トンネル絶縁膜を挟んで、上部及びチャネル幅方向の側部の一部が露出する複数の浮遊ゲート電極10aを形成する工程と、浮遊ゲート電極103aの露出表層部を化学反応させて、電極間絶縁膜の最下層となる第1の絶縁膜109aを浮遊ゲート電極103a上に形成するのと同時に、浮遊ゲート電極103aの上部のチャネル幅方向の幅を、浮遊ゲート電極103aの下部のチャネル幅方向の幅よりも狭くする工程と、電極間絶縁膜109a上に互いに対向する浮遊ゲート電極103aの間に一部が埋め込まれている制御ゲート電極を形成する工程と、を具備する。

(もっと読む)

半導体記憶装置

【課題】DRAMにおいて微細化を進め、さらにメモリセルに縦型のMOSトランジスタを使用すると、隣接ワード線間の寄生容量が増加する。DRAMを安定動作させるためには、この寄生容量によって発生するカップリングノイズを低減する必要がある。また、ワード線間のカップリングノイズを低減する際にチップサイズの増加を抑制する必要がある。

【解決手段】ワード線(上層ワード線UWL)の配線順序を入れ換えるツイスト接続部WCA1をワード線のほぼ中央部に設け、そのツイスト接続部WCA1の下部領域に、ワード線の非選択状態の電位レベルを出力するレベル安定化回路TRを配置する。

(もっと読む)

半導体記憶装置

【課題】読み出し回路・書き込み回路によるビット線容量の増大を抑制することを可能とした半導体記憶装置を提供する。

【解決手段】 ビット線対BL、/BLは、たとえば16個のメモリセルMCi(i=0〜15)毎に分割されており、この分割された分割ビット線対BBL、/BBL毎に1カラムを構成している。1カラムを構成する16個のメモリセルMCi毎に、読み出し回路12、及び書き込み回路13が設けられている。読み出し回路12は、分割ビット線対BBL、/BBLのいずれか一方に接続され片側ビット線読み出し方式を採用する検知回路121を備えている。書き込み回路13は、読み出し回路12とはエリア的に分離された形で配置されている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】近接効果を低減してカップリング係数を増大し、かつ制御ゲート電極−基板間のリーク電流を低減する。

【解決手段】半導体基板10と、半導体基板10上に形成されたゲート絶縁膜11と、ゲート絶縁膜11上に第1の方向に沿って所定間隔を空けて形成された浮遊ゲート電極12と、ゲート絶縁膜11上の浮遊ゲート電極12間に前記第1の方向に直交する第2の方向に沿って帯状に形成された絶縁膜14と、絶縁膜14上方に前記第2の方向に沿って帯状に形成され側面が浮遊ゲート電極12の側面と対向する制御ゲート電極16と、浮遊ゲート電極12と制御ゲート電極16との間、及び制御ゲート電極16と絶縁膜14との間に形成され、膜厚が絶縁膜14の膜厚より大きいインターポリ絶縁膜15と、を備える。

(もっと読む)

半導体集積回路装置の製造方法

【課題】DRAM等の半導体集積回路装置の微細化を図り、また、高性能化を図る。

【解決手段】周辺回路領域に横型のnチャネル型MISFETを形成した後、その上部に酸化シリコン膜23を形成し、さらにその上部であって、メモリセル領域MAに、縦型の情報転送用MISFETQsであって、下層からn型多結晶シリコン膜41、ノンドープの多結晶シリコン膜43およびn型多結晶シリコン膜47よりなる半導体柱を有し、ノンドープの多結晶シリコン膜43の上下には、窒化シリコン膜42、46が形成され、半導体柱の側壁に形成された酸化シリコン膜53をゲート絶縁膜とし、また、n型多結晶シリコン膜55、57をゲート電極とする情報転送用MISFETQsを形成し、さらに、n型多結晶シリコン膜47の上部に、情報蓄積用容量素子Cを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離絶縁膜上に形成されたキャパシタを有する半導体装置において、寄生容量を抑制すること。

【解決手段】本発明は半導体基板10に設けられた素子分離絶縁膜12と、素子分離絶縁膜上に設けられた導電層22と、導電層を覆うように設けられた層間絶縁膜30と、層間絶縁膜内であって導電層上に接触して設けられた金属からなる下層電極42と、層間絶縁膜内であって下層電極上に設けられた誘電体層49と、層間絶縁膜内であって誘電体層上に設けられた金属からなる上層電極52と、を具備する半導体装置およびその製造方法である。

(もっと読む)

非線形導体メモリ

高速で低電力のメモリ素子は、非線形導体のアレイを備え、格納、アドレスデコーディング、および出力検出はすべて、ダイオードまたは他の非線形導体によって達成される。様々な実施形態において、行抵抗器および列抵抗器は、選択されていない行または列に接続されているときの高抵抗と、選択された行および列に接続されたときの低抵抗との間で切り替え可能である。電子メモリ素子は、情報回路と、複数の行スイッチと、複数の列スイッチと、選択回路とを含む。  (もっと読む)

(もっと読む)

不揮発性半導体メモリ及びその製造方法

【課題】電荷トラップ型の不揮発性半導体メモリの動作速度を向上させること。

【解決手段】不揮発性半導体メモリは、半導体基板1と、半導体基板1上にゲート絶縁膜10を介して形成された第1ゲート電極WGと、第1ゲート電極WGの側方に形成され第1ゲート電極WGから電気的に絶縁された第2ゲート電極CG1、CG2と、半導体基板1と第2ゲート電極CG1、CG2との間に少なくとも形成された電荷トラップ膜30と、を備える。第1ゲート電極WGは、ゲート絶縁膜10に接触する下方部WG−Lと、下方部WG−Lの上に形成された上方部WG−Uと、を含む。上方部WG−Uと第2ゲート電極CG1、CG2との間隔は、下方部WG−Lと第2ゲート電極CG1、CG2との間隔より大きい。

(もっと読む)

メモリセル、電子システム、メモリセルの形成方法、およびメモリセルのプログラミング方法

いくつかの実施形態は、誘電体材料によって互いにスペーシングされる、垂直に積層される電荷捕獲領域を有するメモリセルを含む。誘電体材料は、高k材料を含み得る。電荷捕獲領域のうちの1つ以上は、金属材料を含み得る。かかる金属材料は、ナノドット等の複数の個別の絶縁されたアイランドとして存在し得る。いくつかの実施形態は、メモリセルの形成方法を含み、トンネル誘電体上に2つの電荷捕獲領域が形成され、当該領域は互いに対して垂直に配置され、トンネル誘電体に最も近い領域は、もう1つの当該領域よりも深いトラップを有する。いくつかの実施形態は、メモリセルを含む電子システムを含む。いくつかの実施形態は、垂直に積層される電荷捕獲領域を有するメモリセルのプログラミング方法を含む。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】ゲートオーバーラップ容量を少なくすることができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】半導体基板1上に形成された柱状体3と、前記柱状体3の先端側3bに形成された先端側不純物拡散領域5と、前記柱状体3の基端側3aに形成された基端側不純物拡散領域4と、前記柱状体3の外周面3cに形成されたゲート絶縁膜7と、前記先端側不純物拡散領域5を覆うように外周面3cに形成された先端側絶縁層10と、前記基端側不純物拡散領域4を覆うように外周面3cに形成された基端側絶縁層9と、前記先端側絶縁層10および前記基端側絶縁層9の間に配置されたゲート電極8と、を具備することを特徴とする半導体装置21を用いることにより、上記課題を解決できる。

(もっと読む)

半導体記憶装置

【課題】メモリセル面積を増大させることなく、配線間のカップリングノイズを低減可能な半導体記憶装置を提供する。

【解決手段】本発明の半導体記憶装置は、マルチポートメモリを有しており、行列状に配置された複数のメモリセルMCと、第1ポート13aに接続された複数の第1のワード線WLA0〜WLAnと、第2ポート13bに接続された複数の第2のワード線WLB0〜WLBnとを備えている。複数の第1のワード線WLA0〜WLAnの各々と複数の第2のワード線WLB0〜WLBnの各々とが平面レイアウトにおいて交互に配置されている。

(もっと読む)

201 - 220 / 322

[ Back to top ]