Fターム[5F083GA03]の内容

Fターム[5F083GA03]に分類される特許

121 - 140 / 322

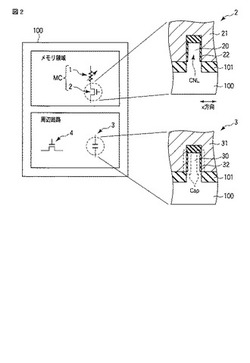

抵抗変化メモリ

【課題】大きい静電容量のキャパシタを含む抵抗変化メモリを提供する。

【解決手段】本実施形態の抵抗変化メモリは、アクティブ領域としての半導体領域20と、ゲート絶縁膜22を介して半導体領域21の側面に対向するゲート電極21とを有する選択トランジスタと、記憶するデータに応じて抵抗値が変化するメモリ素子1とを含むメモリセルMCと、第1のキャパシタ電極としての半導体領域30と、半導体領域30の側面に対向するキャパシタ電極31と、半導体領域20とキャパシタ電極31との間に設けられたキャパシタ絶縁膜32とを含むキャパシタ3と、を含む。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第1のトランジスタのゲート電極と、該ゲート電極に接する第2のトランジスタのソース電極とは、エッチングの選択比がとれる材料を用いて形成される半導体装置を提供する。第1のトランジスタのゲート電極と、第2のトランジスタのソース電極とをエッチングの選択比がとれる材料を用いて形成することで、レイアウトのマージンを低減させることができるため半導体装置の集積度を向上させることができる。

(もっと読む)

半導体装置

【課題】ゲートコンタクトプラグ形成のためのコンタクトホールの深さを適切に制御可能とする。

【解決手段】半導体装置1は、活性領域ARを囲む第1の絶縁体ピラー21と、第1の絶縁体ピラー21の活性領域AR側の側面21sとy方向に相対向する側面22sを有する第2の絶縁体ピラー22と、第1及び第2の絶縁体ピラー21,22の上面を覆う絶縁膜31と、第1のゲート電極16と電気的に接続し、かつ少なくとも側面21s,22sを覆う第2のゲート電極23と、底面に絶縁膜31及び第2のゲート電極23が露出したコンタクトホールの内部に設けられ、かつ第2のゲート電極23の上面と電気的に接続するゲートコンタクトプラグ42とを備え、側面21s,22s間の距離は、ゲートコンタクトプラグ42のx方向の長さより短く、ゲートコンタクトプラグ42は側面21s,22s間の領域で第2のゲート電極23と電気的に接続する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】書込・消去特性が高く、動作の信頼性が高い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた第1電極と、前記第1電極上に設けられた電極間絶縁膜と、前記電極間絶縁膜上に設けられた第2電極と、を備える。前記電極間絶縁膜は、積層絶縁層と、前記積層絶縁層上に設けられ、前記積層絶縁層よりもバリアハイトが低い電荷蓄積層と、前記電荷蓄積層上に設けられ、前記電荷蓄積層よりもバリアハイトが高いブロック絶縁層と、を有する。前記積層絶縁層は、第1絶縁層と、前記第1絶縁層上に設けられ、前記第1絶縁層よりもバリアハイトが低い量子効果層と、前記量子効果層上に設けられ、前記量子効果層よりもバリアハイトが高い第2絶縁層と、を有する。

(もっと読む)

パルス変換回路

【課題】回路面積を低減する。

【解決手段】第1の信号が入力され、第2の信号を出力する論理回路を具備し、論理回路は、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧に設定するか否かを制御するP型トランジスタと、エンハンスメント型であり、閾値電圧の絶対値がP型トランジスタより大きく、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧より高い第2の電圧に設定するか否かを制御するN型トランジスタと、を備え、P型トランジスタは、チャネルが形成され、第14族の元素を含有する半導体層を含み、N型トランジスタは、チャネルが形成され、キャリア濃度が1×1014/cm3未満である酸化物半導体層を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】歩留まりに優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、基板内の記憶回路領域に形成されており、多層配線層内に埋め込まれた少なくとも1以上の容量素子および周辺回路を有する記憶回路と、平面視において、基板内の憶回路領域とは異なる領域である論理回路領域に形成された論理回路と、を備え、容量素子は、下部電極、容量絶縁膜、上部電極、埋設電極および、上部接続配線で構成されており、上部接続配線と埋設電極とは、同一の材料かつ一体に構成されており、上部接続配線と下部電極との間には、論理回路を構成する前記配線が少なくとも1以上設けられており、上部接続配線の上面と、上部接続配線と同じ配線層に形成された論理回路を構成する配線の上面とが、同一面を構成する。

(もっと読む)

不揮発性半導体メモリトランジスタ、不揮発性半導体メモリ、および、不揮発性半導体メモリの製造方法

【課題】浮遊ゲートと制御ゲート間の容量を大きくすることができるとともに、かつ制御ゲートと島状半導体間の寄生容量を低減する、島状半導体を用いた構造を持つ不揮発性半導体メモリ、およびその製造方法を提供する。

【解決手段】不揮発性半導体メモリを構成する不揮発性半導体メモリトランジスタは、基板側からソース領域303、チャネル領域304及びドレイン領域302がこの順に形成された島状半導体301と、チャネル領域の外周を囲むように、トンネル絶縁膜305を間に介在させて配置された中空柱状の浮遊ゲート306と、当該浮遊ゲートの外周を囲むように、インターポリ絶縁膜307を間に介在させて配置された中空柱状の制御ゲート308と、を備えている。浮遊ゲートと、制御ゲートの上面、下面および内側面との間には、インターポリ絶縁膜が介在配置されている。

(もっと読む)

配線形成方法

【課題】配線層で、配線密度の高い領域では隣接する配線間のショートを防ぎ、配線密度の低い領域では所望の平坦度が得られるとともに所望の配線抵抗が得られるように配線高さを制御できる配線形成方法を提供する。

【解決手段】まず、基板上に第1の絶縁膜111と、第1の絶縁膜111に比してCMP研磨レートの小さい所定の厚さの第2の絶縁膜112を順に積層させて層間絶縁膜11を形成し、ついで、層間絶縁膜11の第1の領域に第1の配線密度となり、第2の領域に第1の配線密度よりも低い第2の配線密度となるように、第2の絶縁膜112を貫通し、底部が第1の絶縁膜111に至る配線形成用溝21を形成した後、配線形成用溝21を形成した層間絶縁膜11上に導電性材料膜14を形成し、そして、CMP法によって、少なくとも第1の領域で第1の絶縁膜111が露出、後退するように層間絶縁膜11と導電性材料膜14を研磨する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

不揮発性半導体メモリ

【課題】新たなコンセプトに基づく不揮発性半導体メモリを提供する。

【解決手段】本開示の不揮発性半導体メモリは、半導体基板11上の半導体層12と、半導体層12を貫通する複数のコントロールゲートCG11〜CG17と、第1方向の2つの端部における半導体層12内にそれぞれ配置される2つの第1導電型拡散層14と、半導体層12上で第1方向に延びる複数のセレクトゲート線SG1〜SG5と、複数のセレクトゲート線SG1〜SG5上で第2方向に延びる複数のワード線WL1〜WL7とを備える。複数のセレクトゲート線SG1〜SG5の各々は、第1方向に並ぶ複数のコントロールゲートCG11〜CG17と複数のワード線WL1〜WL7との間に接続される複数のセレクトトランジスタに共有されるセレクトゲートとして機能する。半導体層12及び複数のコントロールゲートCG11〜CG17は、メモリセルアレイを構成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルに書き込み用のトランジスタ、読み出し用のトランジスタおよび選択用のトランジスタを備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】どのようなレイアウトの配線に対しても、個々の配線ごとにエアギャップ部を設ける。エアギャップ部によって、配線の寄生容量を低減する。

【解決手段】半導体装置は、層間絶縁膜と、層間絶縁膜内に埋め込まれた配線と、配線の側面と層間絶縁膜との間に設けられたエアギャップ部と、を有する。半導体装置の製造方法は、配線の側面上に第2のサイドウォール膜を形成した後、第2のサイドウォール膜の一部が露出するように第1の絶縁膜を形成する。次に、第2のサイドウォール膜を除去することによりサイドスペースを形成した後、サイドスペースが埋め込まれないように第2の絶縁膜を形成することによりサイドスペースから構成されるエアギャップ部を形成する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面に第1の絶縁膜を形成し、第1の絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて第1の絶縁膜にエッチング処理を行うことにより、第2の絶縁膜を形成し、第2の絶縁膜を覆うように第1の導電膜を形成し、第1の導電膜および第2の絶縁膜に研磨処理を行うことにより、等しい厚さの第3の絶縁膜、ソース電極およびドレイン電極を形成し、第3の絶縁膜、ソース電極およびドレイン電極上に酸化物半導体膜を形成し、酸化物半導体膜上にゲート絶縁膜を形成し、ゲート絶縁膜上の第3の絶縁膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根(RMS)粗さが1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、および絶縁層表面の一部とドレイン電極表面との高低差は、5nm以上の半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】電荷を蓄積可能な電荷蓄積膜を有する不揮発性メモリセルを含む半導体装置において、データ保持特性劣化を改善し、その信頼性を向上させることにある。

【解決手段】半導体基板の主面に不揮発性メモリセルを含む半導体装置であって、不揮発性メモリセルは、半導体基板上に第1絶縁膜と、導電膜と、第2絶縁膜と、電荷を蓄積可能な電荷蓄積膜とを有する。また、電荷蓄積膜上に第3絶縁膜と、第1ゲート電極と、第1絶縁膜から前記第1ゲート電極までの一連の積層膜と接するように第4絶縁膜と、第1絶縁膜と並ぶように前記半導体基板上に第5絶縁膜とを有する。さらに、第5絶縁膜上に形成され、第4絶縁膜の側面に前記第1ゲート電極と隣り合うように第2ゲート電極と、第1ゲート電極と第2ゲート電極を挟むように半導体基板にソース領域およびドレイン領域とを有する。半導体装置は、導電膜と電荷蓄積膜が平面的に重なり合うように形成されている。

(もっと読む)

メモリセル電荷記憶素子あたりに二重のコントロールゲートを有するフラッシュメモリセルアレイ

【課題】フローティングゲートが少なくとも2つのコントロールゲートラインと容量的に結合するようになっているフラッシュNANDタイプのEEPROMシステムの提供。

【解決手段】コントロールゲートラインはフローティングゲートの側壁と結合するようにフローティングゲート間に位置し、メモリセルの結合比が望ましく高められる。フローティングゲートの選択された行の両側の両方のコントロールゲートラインは普通同じ電圧まで高められ、隣接するフローティングゲートの選択されていない行に結合された第2のコントロールゲートラインは低く保たれる。選択されたフローティングゲートの領域でその電圧を選択的に高めるために、コントロールゲートラインを基板と容量的に結合させる。フローティングゲートの長さとコントロールゲートラインの厚さとは、スペーサのエッチマスクを形成することによってプロセスの最小分解エレメントより小さくされ得る。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた高性能な半導体装置を提供する。

【解決手段】基板上に酸化物半導体層を形成し、酸化物半導体層上に第1の導電層を形成し、第1の導電層上に第2の導電層を形成し、第2の導電層をエッチングすることで、第1のパターンを形成し、第1のパターンを酸化することにより膨張させ、膨張後の第1のパターンをマスクとして第1の導電層をエッチングすることで、ソース電極及びドレイン電極となる第2のパターンを形成し、膨張後の第1のパターン及び第2のパターン及び酸化物半導体層を覆うゲート絶縁層を形成し、ゲート絶縁層上にゲート電極を形成する。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。また、量産性の高い半導体装置を提供することを課題の一とする。また、量産性の高い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】寄生容量を抑制した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】第1方向に沿って交互に積層された複数の電極膜WLと複数の電極間絶縁膜14とを有する積層構造体MLと、積層構造体MLを第1方向に貫通する半導体ピラーSPと、複数の電極膜WLのそれぞれと半導体ピラーSPとの間に設けられた電荷蓄積膜48と、電荷蓄積膜48と半導体ピラーSPとの間に設けられた内側絶縁膜42と、電極膜WLのそれぞれと電荷蓄積膜48との間に設けられた外側絶縁膜43と、を有するメモリ部MUと、メモリ部MUと、第1方向に対して直交する第2方向に沿って併設され、積層構造体MLの第1方向に沿った少なくとも一つの電極膜WLの位置と同じ位置に絶縁部50と、を有する非メモリ部PR10とを備えている。

(もっと読む)

121 - 140 / 322

[ Back to top ]