Fターム[5F083GA03]の内容

Fターム[5F083GA03]に分類される特許

61 - 80 / 322

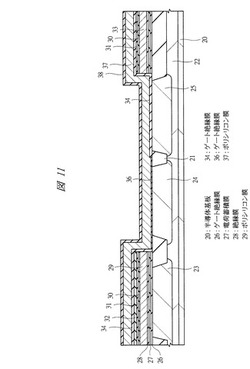

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においてリードデータの有効幅(ウィンドウ幅)を十分に確保する。

【解決手段】積層された複数のコアチップCC0〜CC7と、コアチップを制御するインターフェースチップIFとを備える。コアチップのそれぞれは、メモリセルアレイ70と、データ用の貫通電極TSV1と、メモリセルアレイ70から読み出されたリードデータをデータ用の貫通電極TSV1に出力する出力回路RBUFOとを備える。コアチップにそれぞれ設けられたデータ用の貫通電極TSV1は互いに共通接続され、コアチップにそれぞれ設けられた出力回路RBUFOはインターフェースチップIFより供給されるリードクロック信号RCLKDDに応答して活性化される。これにより、各コアチップの動作速度にばらつきが存在する場合であってもデータバス上でリードデータの競合が生じることがない。

(もっと読む)

半導体記憶装置

【課題】SOI構造のDRAMの提供

【解決手段】

半導体基板1上に複数層の絶縁膜(2、3、4、5)が選択的に設けられ、絶縁膜5上より、絶縁膜5が設けられていない領域上に延在して選択的に半導体層(8、9、10)が設けられ、半導体層の一部9の全周囲にゲート絶縁膜16を介し、絶縁膜4上に包囲構造のゲート電極17が設けられ、ゲート電極に自己整合し、直下に空孔7を有する半導体層の一部10にドレイン領域(14、15)が、半導体層の一部8にソース領域(12、13)が設けられた構造のMIS電界効果トランジスタと、ソース領域12の側面に一部を接し、絶縁膜(3、5)中にトレンチが設けられ、トレンチの側面に電荷蓄積電極19が設けられ、電荷蓄積電極の側面及び上部にキャパシタ絶縁膜20を介してセルプレート電極21が設けられた構造のトレンチ型キャパシタと、により構成されたDRAM。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】耐圧確保に有利な構造を提供する。

【解決手段】実施形態の半導体記憶装置は、基板上で所定方向に平行に延伸した複数の素子分離領域と、隣接する素子分離領域に挟まれた素子領域上の第1絶縁膜と、素子領域上の所定方向に間隔を空けて形成され、第1絶縁膜の上に順に積層された電荷蓄積層、第2絶縁膜、及び制御ゲート電極をそれぞれ有する複数のワードラインと、その両側に1つずつ配置され所定方向の幅がワードラインより大きい選択トランジスタと、ワードライン及び選択トランジスタの上面を覆う層間絶縁膜と、ワードライン間に位置し上部を層間絶縁膜に覆われた第1空洞部と、選択トランジスタのワードラインとは反対側の側壁部に形成され上部が層間絶縁膜で覆われた第2空洞部を備える。実施形態の半導体記憶装置は、互いに隣接する選択トランジスタ間の基板表面に酸化膜が形成され、その下の所定方向に垂直方向の断面が凸型形状になっている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルの高集積化を図ることができる半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板上に設けられた複数本の第1積層体と、前記複数本の第1積層体が配置された領域の外側に配置された第2積層体と、前記第1積層体及び前記第2積層体を覆う層間絶縁膜と、を備える。前記第1積層体と前記第2積層体との距離は、隣り合う前記第1積層体間の距離よりも長く、前記層間絶縁膜における前記第1積層体の相互間には第1の空隙が形成されており、前記層間絶縁膜における前記第1積層体と前記第2積層体との間には第2の空隙が形成されている。そして、前記第2の空隙の下端は、前記第1の空隙の下端よりも上方に位置している。

(もっと読む)

電子部品の製造方法

【課題】導電膜を含む層の加工によって密の配線と疎の配線とが混在して形成された配線層で、所望の配線間の領域にのみ空隙を形成することができる電子部品の製造方法を提供する。

【解決手段】実施形態によれば、電子部品の製造方法は、まず、密の配線と疎の配線とを含む配線パターンとなるように、基板1上の導電性材料膜を含む加工対象を加工する。ついで、密の配線の形成領域にのみ配線間を埋め込む犠牲膜111を形成した後、基板1上に絶縁膜112を形成する。絶縁膜112上にレジスト113を塗布し、密の配線の形成領域上の一部と疎の配線の形成領域とが露出するようにレジスト113のパターニングを行った後、レジスト113をマスクとして絶縁膜112をエッチングする。さらに、密の配線の形成領域上の一部を通して、犠牲膜111を除去する。そして、疎の配線の形成領域で隣接する配線間を埋め込むように基板1上に埋込絶縁膜114を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】配線部を通じた信号伝搬速度を向上できるようにした半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板上に形成された第1絶縁膜と、前記第1絶縁膜上に形成された、前記第1絶縁膜より比誘電率が高い第2絶縁膜と、前記第2絶縁膜と隣接する側面が順テーパ形状を有し、前記第1絶縁膜および前記第2絶縁膜を貫通して形成された複数の縦柱状プラグと、前記第2絶縁膜上に形成された、前記第2絶縁膜よりも比誘電率が低い第3絶縁膜と、前記複数の縦柱状プラグの上部に到達するように前記第3絶縁膜に形成された複数の溝と、前記複数の溝内にそれぞれ形成され、前記複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部と、を備える。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

記憶装置およびその製造方法

【課題】メモリセルの構造を最適化することにより、更なる微細化を可能にする記憶装置を提供する。

【解決手段】複数の第1の電極配線と、第1の電極配線と交差する複数の第2の電極配線と、1本の第2の電極配線と、互いに隣接する2本の第1の電極配線との間に形成される1個のビアプラグであって、前記第1の電極配線に対向する底面の、第1の電極配線の伸長方向に垂直な方向の最大径が、第1の電極配線幅の2倍と第1の電極配線間の幅を加えた長さよりも小さいビアプラグと、ビアプラグと2本の第1の電極配線の一方との間に形成される第1の記憶素子と、ビアプラグと2本の第1の電極配線の他方との間に形成される第2の記憶素子とを有する記憶装置。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の作製方法

【課題】高度に集積化したDRAMを提供する。

【解決手段】第1絶縁体101上にビット線102b、ビット線102b上に第2絶縁体103、第2絶縁体103上にストライプ状の第3絶縁体106a乃至106c等を形成し、第3絶縁体106bを覆って、半導体領域109bとゲート絶縁体110を形成する。ビット線102bと半導体領域109bは第1のコンタクトプラグ105a、105bで接続される。その後、導電性膜を形成し、これを異方性エッチングすることで、第3絶縁体106a乃至106cの側面にワード線111a乃至111dを形成し、第3絶縁体106bの頂部にキャパシタへ接続するための第2コンタクトプラグ115bを形成する。ワード線111b、111cを同期させることで、キャパシタに電荷を出入りさせる。このような構造でメモリセルの面積を4F2とできる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】浮遊ゲートと制御ゲートとの間におけるリークを抑制することができる不揮発性半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコンを含む基板と、前記基板上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた浮遊ゲートと、前記浮遊ゲート上に設けられたリーク抑制部と、前記リーク抑制部上に設けられたゲート間絶縁膜と、前記ゲート間絶縁膜上に設けられた制御ゲートと、を備える。前記リーク抑制部の誘電率は、前記ゲート間絶縁膜の誘電率よりも高くなっている。

(もっと読む)

半導体メモリ装置

【課題】DRAMに必要なキャパシタの容量を低減し、高度に集積化したDRAMを提供する。

【解決手段】分割ビット線型DRAMにおいて、サブビット線をワード線の下に形成し、ビット線をワード線の上に形成する。分割ビット方式でサブビット線の寄生容量が低減し、かつ、セルトランジスタのオフ抵抗を必要に応じて高いものとすることによって、キャパシタの容量を通常のDRAMの1/10以下とすることができる。このため、スタック型キャパシタであっても、その高さを従来のものの1/10以下とできるので、その上にビット線を設けることも容易となる。また、セルトランジスタの構造を特殊なものとすることでメモリセルあたりの面積を4F2とできる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】動作特性の向上を図ることができる不揮発性半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコンを含む基板と、前記基板上に間隔をあけて設けられた複数のメモリセルと、前記メモリセルの側壁に形成された絶縁膜と、を備えている。そして、前記絶縁膜は、前記メモリセル同士の間に形成された空隙部の上方において、隣接する前記メモリセルに向けて突出する突出部を有している。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

半導体記憶装置

【課題】動作速度が高い半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、一方向に沿って相互に平行に配列された複数枚のゲート電極膜と、前記一方向に延び、前記複数枚のゲート電極膜を貫通する半導体部材と、前記ゲート電極膜と前記半導体部材との間に設けられた電荷蓄積膜と、を備える。前記ゲート電極膜における前記半導体部材に対向した端部には、前記一方向に沿って突出した凸部が設けられており、前記ゲート電極膜間の空間の一部は気体層となっている。

(もっと読む)

半導体装置

【課題】 電源遮断機能付きで記憶容量の増減変更を伴う設計が容易なSRAMマクロを有する半導体装置を提供する。

【解決手段】 本発明の半導体装置では、SRAMのメモリセルが複数配置されているメモリアレイと、メモリアレイへのデータの書き込みおよびメモリアレイからのデータの読み出しを行う第1の周辺回路と、メモリアレイおよび第1の周辺回路と電源線との接続を遮断するスイッチ群とを含むレイアウトの単位が複数配置されている。

(もっと読む)

半導体記憶装置の製造方法

【課題】隣接するメモリセル間およびメモリセルと選択トランジスタとの間に間隙を設けつつ、選択トランジスタおよび周辺回路における短絡を抑制する。

【解決手段】本実施形態による半導体記憶装置は、ゲートを有する複数のメモリセルが直列に接続されたメモリセルストリングを備える。選択トランジスタが、メモリセルストリングの一端にある端部メモリセルに接続されている。側壁膜が、端部メモリセルと選択トランジスタとの間において、端部メモリセルのゲートの側面および選択トランジスタのゲートの側面を被覆する。端部メモリセルの側壁膜と選択トランジスタの側壁膜との間に空隙がある。

(もっと読む)

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

記憶素子、記憶装置、信号処理回路、記憶素子の駆動方法

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶素子を提供する。消費電力の低減可能な信号処理回路を提供する。

【解決手段】クロック信号に同期してデータを保持する記憶素子において、酸化物半導体層にチャネルが形成されるトランジスタ及び容量素子を用いることより、電源電圧の供給が停止した間もデータ保持ができる。ここで、電源電圧の供給を停止する前に、クロック信号のレベルを一定に保った状態で当該トランジスタをオフ状態とすることにより、データを正確に容量素子に保持させることができる。また、このような記憶素子を、CPU、メモリ、及び周辺制御装置のそれぞれに用いることによって、CPUを用いたシステム全体で、電源電圧の供給停止を可能とし、当該システム全体の消費電力を削減することができる。

(もっと読む)

61 - 80 / 322

[ Back to top ]