Fターム[5F083GA03]の内容

Fターム[5F083GA03]に分類される特許

21 - 40 / 322

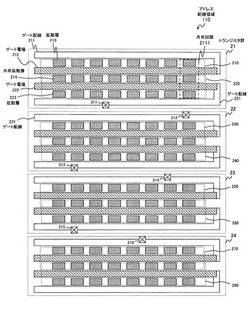

半導体記憶装置

【課題】アドレス信号の配線に起因する配線容量を低減させ、アクセス速度の高速化を実現する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のビット線と複数のワード線に対応して設けられた複数のメモリセルと、複数のメモリセルのいずれかを特定するためのアドレス信号を中継する中継バッファと、複数のワード線のうち、中継バッファにて中継されたアドレス信号に応じたワード線を選択するトランジスタを複数有するワード線ドライバ回路と、を備え、トランジスタでは、2つの拡散層のうち一方の拡散層が他のトランジスタの拡散層と共有し、拡散層を共有している2つのトランジスタで構成される複数の共有回路が、複数のトランジスタ群に分けられ、複数のトランジスタ群のうち隣り合う前記トランジスタ群の隙間部分に、隣り合うトランジスタ群のいずれかのゲート配線が設けられ、中継バッファはトランジスタ群のゲート配線と接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造のフラッシュメモリーの提供

【解決手段】

半導体基板1上にシリコン窒化膜2及びシリコン酸化膜3が選択的に設けられ、シリコン酸化膜3上には、選択的に横(水平)方向エピタキシャルSi層5が設けられ、Si層5の両側面には、それぞれ側面を接して横(水平)方向エピタキシャルSi層6が設けられた構造からなる半導体層が素子分離領域のシリコン窒化膜4により絶縁分離されている。Si層6の残りの周囲には第1のゲート酸化膜10を介して包囲型フローティングゲート電極11が設けられ、包囲型フローティングゲート電極11の周囲には第2のゲート酸化膜12を介して包囲型コントロールゲート電極13(ワード線)が設けられ、Si層5には概略ソースドレイン領域9が設けられている2重包囲型ゲート電極を有するMIS電界効果トランジスタより構成したフラッシュメモリー。

(もっと読む)

不揮発性半導体記憶装置

【課題】カップリング比の増大と書き込み/消去時のリーク電流の低減とを実現する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、半導体層11と、半導体層11上の第1の絶縁層13と、第1の絶縁層13上の電荷蓄積層14と、電荷蓄積層14上の第2の絶縁層15と、第2の絶縁層15上の制御ゲート電極16とを備える。第2の絶縁層15は、電荷蓄積層14側から制御ゲート電極16側に向かって、第1のランタンアルミネート層LAO、ランタンアルミシリケート層LASO及び第2のランタンアルミネート層LAOを備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子埋設用凹部上端部の肩落ちによるキャパシタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】半導体装置は、保護層80は、凹部(孔23)の上端部の周囲に設けられている。この保護層80は、保護層80と同一層に位置しており、論理回路領域に位置している多層配線層を構成する絶縁層よりも誘電率が高い材料で構成されており、機械強度に優れた部材となる。これにより、凹部(孔23)上端部の肩落ちを抑制し、キャパシタ高さのバラツキを抑制する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択ゲートトランジスタや周辺回路部のトランジスタの下部電極の抵抗値を低減し、しきい値電圧の増加も図れるようにする。

【解決手段】ゲート電極の加工時に、選択ゲートトランジスタのゲート電極SGD−SGD間の側壁部と、周辺回路部のトランジスタのゲート電極PGの両側壁とに、多結晶シリコン膜4の上部に段差形状を形成し、傾斜部4dを設ける。ゲート電極の多結晶シリコン膜6のシリサイド加工時に、多結晶シリコン膜4の傾斜部4dからもシリサイド化を進行させ、シリサイド膜7および7aを形成する。これにより、ゲート電極SGDおよびPGの下部電極においても低抵抗化を図ることができる。多結晶シリコン膜4に分断層4aを設けることで、シリサイド反応を停止させたり、設けないでゲート絶縁膜3の部分までシリサイド反応させてしきい値電圧を増加させたりできる。

(もっと読む)

半導体装置及びその製造方法

【課題】高品質な配線を有する半導体装置を提供する。

【解決手段】第1の領域100及び第2の領域200に設けられた第1の絶縁層10と、第1の領域に設けられた第1の絶縁層上に形成された第2の絶縁層11aと、第2の領域200に設けられた第1の絶縁層上に形成され、第2の絶縁層と略同一の高さを有する第3の絶縁層11cと、第1の領域に設けられた第1の絶縁層上及び第2の絶縁層の両方の側壁に形成された第1の配線層13aと、第2の領域に設けられた第1の絶縁層上、及び第3の絶縁層の上面及び側壁上に形成された第2の配線層13bと、第1の絶縁層、第2の絶縁層、第1の配線層、及び第2の配線層を覆う第4の絶縁層15と、第1の領域に設けられた第4の絶縁層内に形成され、第1の配線層に接続された第1のコンタクトプラグ17aと、第2の領域に設けられた第4の絶縁層内に形成され、第2の配線層に接続された第2のコンタクトプラグ17bと、を備える。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】書き込み特性を向上することが可能な不揮発性半導体記憶装置とその製造方法を提供する。

【解決手段】複数のゲート電極構造13は、半導体基板11上に形成されたゲート絶縁膜12、電荷蓄積層14、ゲート間絶縁膜15、第1制御ゲート16、及び前記第1制御ゲートより幅が広い第2制御ゲート電極17を有する。絶縁膜19は、制御ゲート電極17間及び制御ゲート電極より上方に形成された空隙19を有する。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】チップ面積の縮小を図る。

【解決手段】磁気ランダムアクセスメモリは、メモリセル部の素子領域10a上に形成された第1の拡散層17aと、第1の拡散層に接続された第1のコンタクトCB1と、第1のコンタクト上に形成された第1の下部電極層21aと、第1の下部電極層上に形成された第1の抵抗変化層22a及び第1の上部電極層23aと、周辺回路部において互いに異なる素子領域に形成された第2乃至第4の拡散層17d、17eと、第2乃至第4の拡散層に接続された第2乃至第4のコンタクトCS1、CS2と、第1の下部電極層、第1の抵抗変化層、第1の上部電極層と同じ高さに形成された第2の下部電極層21b、第2の抵抗変化層22b、第2の上部電極層23bとを具備する。第2の下部電極層は、第2及び第3のコンタクトを接続する第1のローカル配線L1として機能する。

(もっと読む)

集積回路装置及びその製造方法

【課題】FinFETの特性が均一な集積回路装置及びその製造方法を提供する。

【解決手段】実施形態に係る集積回路装置は、半導体基板の上面に形成され、第1方向に延びる複数本のフィンと、前記フィン間に配置された素子分離絶縁膜と、前記第1方向に対して交差した第2方向に延び、前記素子分離絶縁膜上に設けられたゲート電極と、前記フィンを前記ゲート電極から絶縁する絶縁膜と、を備える。そして、連続して配列された複数本の前記フィンが配置された第1領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも下方の第1の位置に位置し、前記第1領域から見て前記第2方向に位置する第2領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも上方の第2の位置に位置する。また、前記第2領域においては、前記素子分離絶縁膜が前記フィンの側面の全体を覆っている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】信頼性を向上させることができる半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、積層して設けられた複数のゲート電極と、前記ゲート電極の間に設けられた絶縁膜と、を有した積層体と、前記積層体を貫く半導体ピラーと、前記半導体ピラーと前記ゲート電極との間に空隙を介して設けられた電荷蓄積層と、前記電荷蓄積層と前記ゲート電極との間に設けられたブロック絶縁層と、を有したメモリセルを積層方向に複数備えている。そして、前記複数の各メモリセル毎に、前記電荷蓄積層と前記半導体ピラーとの間の距離を保つ支持部が設けられている。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置及び、信頼性の高い半導体装置の作製方法を提供する。また、消費電力が低い半導体装置及び消費電力が低い半導体装置の作製方法を提供する。また、量産性の高い半導体装置及び量産性の高い半導体装置の作製方法を提供する。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

半導体装置

【課題】プロセス技術が比較的簡単、且つ、少ない素子数で多値情報を記憶することがでるメモリを提供する。

【解決手段】メモリ素子426において、第1の記憶素子における第1の電極417の形状の一部を、第2の記憶素子における第1の電極417の形状と異ならせることで、第1の電極417と第2の電極420の間の電気抵抗が変化する電圧値を異ならせて、1ビットを越える多値の情報の記憶を一つのメモリセルで行う。第1の電極417を部分的に加工することで単位面積当たりの記憶容量を増大することができる。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲートトランジスタのゲート電極間の間隔の縮小を実現する不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板に、複数の第1の素子領域と、素子分離領域と、第2の素子領域を形成する。第1の素子領域上に、メモリセルゲート電極、2本の選択ゲート電極を形成し、第2の素子領域に周辺ゲート電極を形成する。第1の絶縁膜を形成し、周辺ゲート電極の側壁部上が開口される第1のレジストパターンを形成し、第1のエッチング処理を行い、側壁絶縁膜を形成する。第2のレジストパターンを形成し、第2のエッチング処理を行い、選択ゲート電極側壁部の第1の絶縁膜を除去する。第2の絶縁膜を堆積し、第3の絶縁膜を堆積する。2本の選択ゲート電極間上が開口される第3のレジストパターンを形成し、第3のエッチングおよび第4のエッチング処理を行い、コンタクトホールを形成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】抵抗変化メモリの製造プロセスにおけるPEP数を削減する。

【解決手段】実施形態に係わる抵抗変化メモリは、第1の方向及びこれに直交する第2の方向にそれぞれ交互に配置される複数の抵抗変化素子MTJ及び複数のビアV0と、複数の抵抗変化素子MTJの側壁上に配置される複数の側壁絶縁層PLとを備える。複数の抵抗変化素子MTJは、一定ピッチで格子状に配置され、複数の側壁絶縁層PLの側壁に垂直な方向の厚さは、複数の側壁絶縁層PLが互いに部分的に接触し、複数の側壁絶縁層PL間に複数のホールが形成される値に設定される。複数のビアV0は、これら複数のホール内に配置される。

(もっと読む)

半導体記憶装置

【課題】データの読み出し速度を向上する。

【解決手段】半導体記憶装置1は、メモリセルアレー1aと、コラム線1bと、第1および第2のデータ線1d,1eと、データの読み出し時には、コラム線1bに第1および第2のデータ線1d,1eの一方を選択して接続し、データの書き込み時には、コラム線1bに第1および第2のデータ線1d,1eを接続するスイッチ1cと、第1および第2のデータ線1d,1eに接続された読み出し回路1fと、第1および第2のデータ線1d,1eに接続された書き込み回路1gと、を有する。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1及び第2のノードを有する論理回路と、第1のノードに接続された第1の記憶回路と、第2のノードに接続された第2の記憶回路と、第1のノード、第2のノード、第1の記憶回路、及び第2の記憶回路に接続されたプリチャージ回路と、を有し、読み出しの際に、プリチャージ回路は、プリチャージ電位を第1のノード及び第2のノードに出力し、第1の記憶回路及び第2の記憶回路は、チャネルが酸化物半導体膜に形成されるトランジスタを含む記憶装置である。

(もっと読む)

半導体集積回路

【課題】記憶装置の消費電力を低減すること、記憶装置の面積を低減すること、記憶装置を構成するトランジスタの数を低減する。

【解決手段】第1の出力信号及び第2の出力信号の電位を比較する比較器と、第1の酸化物半導体トランジスタ及び第1のシリコントランジスタを有する第1のメモリ部と、第2の酸化物半導体トランジスタ及び第2のシリコントランジスタを有する第2のメモリ部と、当該第1の出力信号及び当該第2の出力信号の電位を確定する出力電位確定器とを有し、当該第1の酸化物半導体トランジスタのソース又はドレインの一方は、当該第1のシリコントランジスタのゲートに電気的に接続されており、当該第2の酸化物半導体トランジスタのソース又はドレインの一方は、当該第2のシリコントランジスタのゲートに電気的に接続されている記憶装置に関する。

(もっと読む)

21 - 40 / 322

[ Back to top ]