Fターム[5F083GA03]の内容

Fターム[5F083GA03]に分類される特許

161 - 180 / 322

抵抗変化型メモリ

【課題】抵抗変化型メモリの動作特性を向上する。

【解決手段】本発明の一態様に関わる抵抗変化型メモリは、複数のブロックBKが設けられるメモリセルアレイと、複数のブロック内に設けられる複数の抵抗変化型記憶素子と、複数のブロック内に設けられ、抵抗変化型記憶素子に接続される第1及び第2の配線BL,WLと、前記複数のブロックにおいて動作の対象となる選択ブロック及び前記選択ブロックを除く複数の非選択ブロックの状態をそれぞれ制御する制御回路と、を具備し、

制御回路は、選択ブロックを動作させている期間中に、非選択ブロック内の第1及び第2の配線BL,WLに電位VUXを供給する。

(もっと読む)

半導体装置

【課題】同一の半導体基板上に容量素子を備えたメモリ回路部と論理回路部を有する半導体集積回路装置において、論理回路部のみからなる半導体集積回路装置と完全互換の配線設計パラメーターを確保し、かつ微細化が進んでもセル容量を確保する。

【解決手段】容量素子を備えたメモリ回路部と論理回路部を同一の半導体基板上に有する半導体集積回路装置において、論理回路部に形成される多層配線を絶縁分離する層間絶縁膜の少なくとも複数の配線層にまたがる領域に該容量素子を埋め込むことで、該容量素子の接続に必要な配線をすべて論理回路部の多層配線で構成することにより、論理回路部の設計パラメーターを、該メモリ回路部を有しない半導体集積回路装置と完全に同一とする。また多層配線の複数層に渡るように該容量素子を配置させることで該容量素子の高さを確保し、スケーリングが進んでも必要な容量値を確保する。

(もっと読む)

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

半導体装置の製造方法

【課題】浮遊ゲート電極を有するメモリセルの高集積化を実現する半導体装置の製造方法を提供する。

【解決手段】半導体層11の表面にトンネル絶縁膜12を介してシリコンを含む第1の導電体層を形成する工程と、第1の導電体層の表面から半導体層11に至る分離溝9を形成し、第1の導電体層が所定幅で分離された、浮遊ゲート電極となる複数の導電板13bを形成する工程と、導電板13b側面の中間部まで、分離溝9を素子間絶縁膜15で埋め込む工程と、複数の導電板13bの間隔を所定幅と同等以上の幅に維持しながら、導電板13bの露出面にシリコン窒化膜16aを形成する工程と、制御ゲート電極19aとなる第2の導電体層を形成して分離溝9の上部を埋め込む工程と、を備え、シリコン窒化膜16aは、窒素元素を含む原料ガスを励起させて生成する窒素ラジカルによって、導電板13bに含まれるシリコンを窒化して形成される。

(もっと読む)

階層ビット線を有する半導体メモリ素子

【課題】 DRAMメモリセルのセル容量に記憶されたデータの検出に使用されるセンス増幅器に、より短いビット線を配線すること。

【解決手段】 ダイナミックランダムアクセスメモリ(DRAM)素子は、異なる金属層に形成されたローカルビット線およびグローバルビット線を有する階層ビット線構造を有する。ローカルビット線は、複数のローカルビット線区分に分けられ、ビット線絶縁スイッチが、ローカルビット線区分を、グローバルビット線に接続するように、またはグローバルビット線から切断するように構成される。その結果、長さ当たりでより低い静電容量を有するグローバルビット線が、メモリセルのセル容量から離れたセンス増幅器への信号のルーティングに使用されるため、長さ当たりでより高い静電容量を有するローカルビット線を短くすることができる。

(もっと読む)

半導体装置

【課題】複数の被制御チップを積層して構成される積層半導体装置では、制御チップが積層半導体層の外部に設けられており、被制御チップと制御チップとの間のデータ転送による遅延等が問題となっている。

【解決手段】制御チップと共に複数の被制御チップを積層し、制御チップは、それぞれの被制御チップに異なるI/Oセットをアサインし、複数のI/Oセットを同一のアクセスサイクルで処理するシステムインパッケージにおいて、制御チップに近い下位の被制御チップのI/O貫通電極に関連する貫通配線は、使用されることのない上位の被制御チップまで延伸されることによって、すべての被制御チップで使用するそれぞれの貫通配線を等長配線とする半導体装置が得られる。

(もっと読む)

半導体装置及びその製造方法並びにデータ処理システム

【課題】ダミーシリコンピラーとゲートコンタクトプラグとがショートしてしまうことを防止する。

【解決手段】半導体装置10は、半導体基板1と、半導体基板1の主面に対して垂直に設けられたシリコンピラー14と、シリコンピラー14の側面の一部分を覆うゲート絶縁膜15Aと、シリコンピラー14の側面の残りの部分を覆う絶縁体ピラー15Bと、第1及び絶縁体ピラー15A,15Bを介してシリコンピラー14を覆うゲート電極16と、シリコンピラー14、第1及び絶縁体ピラー15A,15B、並びにゲート電極16の上方に設けられた層間絶縁膜30と、層間絶縁膜30に設けられたコンタクトホールに埋め込まれ、ゲート電極16及び絶縁体ピラー15Bに接するゲートコンタクトプラグGCとを備え、絶縁体ピラー15Bの横方向の膜厚TBは、ゲート絶縁膜15Aの横方向の膜厚TAに比べて厚くなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートコンタクトプラグとシリコン基板とのショートを防ぐ。

【解決手段】半導体装置10は、半導体基板11と、半導体基板11の主面に対して垂直な側面を有するシリコンピラー14Bと、シリコンピラー14Bの側面を覆うゲート絶縁膜15Bと、半導体基板11の主面に対して垂直な内周側面16a及び外周側面16bを有し、ゲート絶縁膜15Bを介して内周側面16aとシリコンピラー14Bの側面とが対向するよう、シリコンピラー14Bの側面を覆うゲート電極16と、ゲート電極16の外周側面16bの少なくとも一部を覆うゲート電極保護膜17と、ゲート電極16及びゲート電極保護膜17の上方に設けられた層間絶縁膜30と、層間絶縁膜30に設けられたコンタクトホールに埋め込まれ、ゲート電極16及びゲート電極保護膜17に接するゲートコンタクトプラグGCとを備える。

(もっと読む)

半導体記憶装置

【課題】隣接セルとの容量を低減し、カップリング比を向上させる。

【解決手段】半導体記憶装置は、半導体基板101と、前記半導体基板上に所定間隔を空けて設けられた複数の第1の絶縁膜103と、前記第1の絶縁膜間にビット線方向に沿って設けられた素子分離領域102と、前記第1の絶縁膜上に設けられた第1の電荷蓄積膜104a、前記第1の電荷蓄積膜上に設けられ、ワード線方向の幅が前記第1の電荷蓄積膜より狭い第2の電荷蓄積膜104b、及び前記第2の電荷蓄積膜上に設けられ、ワード線方向の幅が前記第2の電荷蓄積膜より広い第3の電荷蓄積膜104cを有する電荷蓄積層104と、前記第2の電荷蓄積膜と前記素子分離領域との間に設けられた第2の絶縁膜107と、前記電荷蓄積層上及び前記素子分離領域上に前記第2の方向に沿って設けられた第3の絶縁膜105と、前記第3の絶縁膜上に設けられた制御ゲート電極106と、を備える。

(もっと読む)

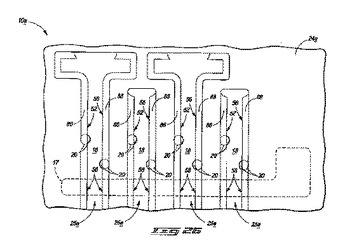

集積回路の製造において複数の導電線を形成する方法、導電線アレイを形成する方法、および集積回路

集積回路の製造において導電線対を形成する方法は、基板上に受けられるダマシン材料にトレンチを形成することを含み、導電性材料34a/35aが、そのダマシン材料を覆ってそしてトレンチ内へ蒸着されてそのトレンチを過充填する。その導電性材料は、少なくともダマシン材料へと戻すように除去されて、そのトレンチ内に残っている導電性材料の少なくともいくらかが残される。エッチングがトレンチ内で導電性材料を通って縦方向に処理されて、トレンチ内に少なくとも第1および第2の導電線の長さの大部分に沿って横断面図において互いにミラー像となる第1および第2の導電線が形成される。他の装いが考えられる。  (もっと読む)

(もっと読む)

半導体装置

【課題】高価な露光装置や高価なマスクを用いることなく、配線等のピッチを狭くすることができる半導体装置を提供する。

【解決手段】第1の導電パターン42と、第1の導電パターンに隣接して形成された第2の導電パターン42と、第1の導電パターンの所定領域下に形成された第1の導体プラグと、第1の導電パターンの所定領域上に形成された第2の導体プラグ62nと、第2の導電パターンのうちの、第1の導電パターンの所定領域に隣接する所定領域下に形成された第3の導体プラグと、第2の導電パターンの所定領域上に形成された第4の導体プラグ62n+1と、第1の導電パターン42の上方に形成され、第2の導体プラグに接続された第3の導電パターン62と、第2の導電パターンの上方に形成され、第4の導体プラグに接続された第4の導電パターン64とを有し、第4の導体プラグは、第2の導体プラグに対して、ずれた位置に配されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】可変抵抗素子を記憶素子として利用する不揮発性半導体記憶装置のアクセス時間を消費電流を増大することなく短縮する。

【解決手段】メモリセル(MC)に対し、書込ビット線(WBL)および読出ビット線(RBL)をそれぞれ別々に設け、またメモリセルの接続するソース線(SL)を、基板領域と同一導電型のソース不純物領域(3)で形成する。メモリセルトランジスタ(MT)とソース不純物領域とは、低抵抗のメタル配線(4)により接続する。ソース線電位の浮き上がりを防止することができ、正確に記憶データに応じたメモリセル電流を生じさせることができ、高速でデータの読出を行うことができる。また、読出ビット線単位でプリチャージおよびデータ増幅を行うことにより読出ビット線負荷を軽減して高速読出を実現することができる。

(もっと読む)

不揮発性記憶装置及びその製造方法

【課題】不揮発性記憶装置の信頼性を向上させる。

【解決手段】第1の方向に延在する、少なくとも一つの第1の配線と、前記第1の配線の上層に配置され、前記第1の方向に対して非平行な第2の方向に延在する、少なくとも一つの第2の配線と、前記第1の配線と前記第2の配線とが交差する、前記第1の配線と前記第2の配線との間に配置された、記憶素子を有した記憶セルと、前記記憶セル間に配置された素子分離層と、を備え、前記記憶セルの側面に、前記素子分離層よりも密度の高い、少なくとも一層の絶縁膜が配置していることを特徴とする不揮発性記憶装置が提供される。

(もっと読む)

半導体記憶装置

【課題】横型メモリセルレイアウトの6トランジスタ型SRAMメモリセルにおいて、ワード線の寄生容量負荷の増大や、配線パーティクルによる歩留低下を解消する。

【解決手段】第2層目配線にて、列方向に並んで配置された複数のワード線351と、第3層目配線にて、行方向に並んで配置された複数の対をなすビット線352,353と、それぞれ対をなすビット線の間に配置された複数のVDD電源配線354と、第4層目配線にて、ビット線より1層上の配線層で形成されたVSS電源配線とを設けた。VSS電源配線は、VSS電源配線より1層下の配線層で形成された島形状VSSパターンを介してCMOS型SRAMセルと接続されており、VSS電源配線と島形状VSSパターンとの接続が1つの島形状VSSパターンあたり複数のビア部の配置によってなされる。

(もっと読む)

半導体装置

【課題】シリコン基板に結晶欠陥が発生するのを抑制して、動作の信頼性が確保され高い歩留まりが得られる半導体装置を提供する。

【解決手段】シリコン基板2に形成された溝にトレンチ分離酸化膜3が形成されている。そのトレンチ分離酸化膜3上にフローティングゲート電極10a〜10dおよびコントロールゲート電極12a〜12dが形成されている。フローティングゲート電極等によって挟まれた領域にシリコン基板2の表面を露出する開口部3aが形成されている。開口部3aを埋込むとともにコントロールゲート電極を覆うようにBPTEOS膜16が形成されている。BPTEOS膜16によって埋込まれた開口部3a内にボイド21が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】コストの増加を抑制して異なる開口幅の溝状絶縁部を形成可能な半導体装置の製造方法を提供する。

【解決手段】波長λの照射光43を遮る遮光膜33から下方の半導体基板11方向に開けられ、開口幅DSがλ未満の素子分離溝35と、遮光膜33から下方の半導体基板11方向に開けられ、開口幅DWがλ以上の素子分離溝36であって、照射光33に感光する感光性膜41で素子分離溝35、36の少なくとも内部を埋めて、開口幅DSの方向に振動する偏光した照射光33を感光性膜41に照射し、感光性膜41を現像して、露光した感光性膜41を溶解除去し、感光性膜41が全て除去された素子分離溝36及び残された素子分離溝35の内部及び上部にCVD絶縁膜を形成し、感光性膜41の上面が露出するように加工し、素子分離溝35の感光性膜41を除去し、素子分離溝35に塗布絶縁膜を形成する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 簡易な工程で水素バリア膜を形成することで水素による信頼性劣化を抑制し、かつワード線間に空隙を設けてワード線間容量を減少させる。

【解決手段】 本発明は、半導体基板上100に配置された複数のメモリセルトランジスタCの電荷蓄積層11および、前記複数の電荷蓄積層11上にゲート間絶縁膜7を介して前記複数の電荷蓄積層11を一定方向に接続し前記一定方向に直交する直交方向に互いに隣接して複数配置された制御ゲート電極17を形成する工程と、前記複数の制御ゲート電極17の上面に接してまたがるように水素をブロックするバリア絶縁膜15を形成する工程と、前記バリア絶縁膜15の上面に層間絶縁膜16を形成する工程と、を備え、少なくとも前記直交方向に隣接する電荷蓄積層11のそれぞれの側壁と、前記半導体基板100と前記バリア絶縁膜15とで囲まれた領域が空隙20となっていること、を特徴とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】 浮遊ゲート電極を含んでおり、メモリセルトランジスタの電気的特性劣化を防ぐことができる不揮発性半導体記憶装置を提供する。

【解決手段】 本発明では、半導体基板1上に形成されたトンネル絶縁膜と、トンネル絶縁膜上に形成された第1の浮遊ゲート電極と第1の浮遊ゲート電極上に形成された非縮退状態の半導体からなる第2の浮遊ゲート電極とを有する浮遊ゲート電極と、浮遊ゲート電極上に形成された電極間絶縁膜と、電極間絶縁膜上に形成された制御ゲート電極とを有する不揮発性半導体記憶装置が得られる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エッチングストッパ膜を有し、配線間容量の増大を抑制可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板11と、半導体基板11の表面上部に配設された層間絶縁膜29と、層間絶縁膜29に埋め込まれ、半導体基板11に対向する上面が層間絶縁膜29の上面と面一に配設され、互いに離間して配置された複数のビアプラグ31と、層間絶縁膜29及びビアプラグ31の表面上部に配設された層間絶縁膜39と、層間絶縁膜39によって分離され、ビアプラグ31と接続され、ビアプラグ31に対向する上面が層間絶縁膜39の上面と面一に配設され、層間絶縁膜39を挟んで相対向する側面に、層間絶縁膜29の側から順に、層間絶縁膜29とはエッチング性が異なり且つ層間絶縁膜39より比誘電率の高い側壁絶縁膜35、及び側壁絶縁膜35とはエッチング性が異なる側壁絶縁膜37を有する複数の第2配線33とを備える。

(もっと読む)

半導体記憶装置

【課題】チップサイズの拡大を抑制するとともに、信号線を形成する領域を確保すること。

【解決手段】本発明の一態様に係る半導体記憶装置1は、複数のサブアレイが行列状に配置され、複数のサブアレイ列A12を有するメモリセルアレイA13と、メモリセルアレイA13の外側に形成され、サブアレイ列A12と略平行に並ぶように配置された複数のアドレスパッドを含むアドレスパッド列A11と、メモリセルアレイの中間部に形成され、サブアレイ列と略平行に並ぶように配置されたデータI/Oパッドを含むデータI/Oパッド列A10と、メモリセルアレイの中間部に配置されたアドレス入力回路A8と、メモリセルアレイA13上に、サブアレイ列A12と略直交する方向に形成され、アドレスパッドA14とアドレス入力回路A8とを直接接続するパッド入力アドレス配線A4とを備える。

(もっと読む)

161 - 180 / 322

[ Back to top ]