Fターム[5F083GA09]の内容

Fターム[5F083GA09]の下位に属するFターム

三次元化 (1,175)

Fターム[5F083GA09]に分類される特許

1,741 - 1,760 / 2,405

マイクロ電子工学装置のための電子部品、およびその製造方法

マイクロ電子工学装置用の電子部品および電子部品の製造方法。こうした方法にかかる特定の実施形態のひとつには、下地層を工作物の上に堆積するステップと、導電層をその下地層の上に形成するステップと、が含まれる。この方法ではさらに続けて、誘電層を導電層の上に堆積するステップを行ってもよい。この下地層の材料は、誘電層の誘電率を、その下地層が導電層の下に無い場合に較べて高めるようなものである。例えば下地層は、誘電層を導電層の上に堆積した後にあらためて高温焼き鈍し工程にかけなくとも、別の方法で非晶質誘電層を結晶化させる構造もしくはそのほかの特性を薄膜積層に与え得る。本方法の実施例のいくつかでは、あらためての高温焼き鈍し工程を使わないようにできるので、高誘電率を持つ誘電層をつくるにあたって非常に役立つであろう。  (もっと読む)

(もっと読む)

ダイナミックランダムアクセスメモリおよび半導体記憶装置

【課題】アスペクト比が1:2のパッケージに高い有効比率で収容できる22N+1ビットの半導体記憶装置を提供する。

【解決手段】アスペクト比が1:2の半導体基板2の主表面を3行3列の9個の領域に等分割し、中央領域以外の各領域にアスペクト比が1:2で22N−2ビットのサブアレイ部3を配置する。中央領域には制御回路4およびパッド5群を設ける。アスペクト比が1:2のメモリチップを形成することができ、従来と同様のアスペクト比が1:2のパッケージに高い有効比率で収容できる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】データ線に対して面積ペナルティの少ない取り出し構造を提供する。

【解決手段】グローバルデータ線となる配線12とp型ウェル領域3内に形成されるローカルデータ線とを選択トランジスタST1を介して接続する。選択トランジスタST1のゲート電極13a上に2本の選択線16および選択線17を形成する。一方の選択線16は、選択トランジスタST1のゲート電極13aと電気的に接続されるが、もう一方の選択線17は、選択トランジスタST1とは接続されない。すなわち、選択線17とゲート電極13aの間には絶縁膜14が形成されている。このように1つの選択トランジスタST1上にゲート長よりも短い2本の選択線16、17を設ける。選択線17は、別の選択トランジスタと接続されるようになっている。

(もっと読む)

半導体集積回路装置、デジタルカメラ、デジタルビデオカメラ、コンピュータシステム、携帯コンピュータシステム、論理可変LSI装置、ICカード、ナビゲーションシステム、ロボット、画像表示装置、光ディスク記憶装置

【課題】 ある程度の小さいメモリセルを実現しつつ、プレート線を共有化でき、且つメモリセルの直列接続による遅延を無くして高速動作が可能な半導体集積回路装置を提供する。

【解決手段】 半導体集積回路装置は、それぞれが、ゲート端子をワード線と接続されたセルトランジスタQ0〜Q3と、セルトランジスタのソース端子に一端を接続された強誘電体キャパシタC0〜C3と、を具備する複数の第1メモリセルを具備する。複数の第1メモリセルのそれぞれのセルトランジスタのドレイン端子を第1ローカルビット線LBLとし且つそれぞれの強誘電体キャパシタの他端を第1プレート線PLとして、第1リセットトランジスタは、ソース端子を第1プレート線と接続され、且つドレイン端子を第1ローカルビット線と接続される。第1ブロック選択トランジスタQSは、ソース端子を第1ローカルビット線と接続され、且つドレイン端子を第1ビット線と接続される。

(もっと読む)

半導体記憶装置

【課題】給電セルのレイアウト面積を縮小することによりメモリアレイ全体のレイアウト面積をさらに縮小することが可能な半導体記憶装置を提供する。

【解決手段】第1の金属配線層に、Nウェル電圧VDDBを供給するメタル312を設ける。メタル312は、共有コンタクト216および219によりNウェル領域に設けられた活性層300と電気的に結合され、Nウェル領域に対してNウェル電圧VDDBが供給される。第3の金属配線層にPウェル電圧VSSBを供給するメタル332,333を設ける。Nウェル電圧VDDBを供給するメタル312は、第1の金属配線層のメタルを用いた構成としているため下層へのくい打ち領域を必要とせず、Pウェル電圧VSSBのメタル332,333の下層へのくい打ち領域のみ確保すればよい。したがって、給電セルPMCのY方向の長さを縮小して、給電セルのレイアウト面積を縮小することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】立体的なキャパシタ構造を有するとともに、ゲート電極の角部付近において電界集中やリーク電流が生じ難く、かつ、微細化が図られた半導体装置を提供する。

【解決手段】半導体装置19を、ゲート絶縁膜2、第1のゲート電極3、電極間絶縁膜8、および第2のゲート電極9などから構成する。ゲート絶縁膜2は半導体基板1の表面上に設けられている。第1のゲート電極3はゲート絶縁膜2上に設けられている。電極間絶縁膜8は第1のゲート電極3の表面を覆って設けられている。また、電極間絶縁膜8は、第1のゲート電極3が有する角部3c,3dのうちゲート絶縁膜2と接触していない角部3c以外を覆っている部分の少なくとも一部の膜厚が、角部3cを覆っている部分の少なくとも一部の膜厚よりも薄く形成されている。第2のゲート電極9は電極間絶縁膜8の表面を覆って設けられている。

(もっと読む)

不揮発性半導体メモリ

【課題】NANDセルユニット内のセレクトゲート電極の低抵抗化を図る。

【解決手段】本発明の例に係る不揮発性半導体メモリは、NANDセルユニットのドレイン拡散層又はソース拡散層を挟んでカラム方向に隣接し、ロウ方向に伸びる第1及び第2セレクトゲート電極SGDが、それぞれ、ロウ方向に規則的に複数のコンタクト領域を有し、第1セレクトゲート電極のコンタクト領域と第2セレクトゲート電極のコンタクト領域が互いに対向しないように配置され、第1セレクトゲート電極のコンタクト領域には、第1セレクトゲート電極よりも上層に形成される配線SDLが接続され、配線SDLは、第1セレクトゲート電極側のNANDセルユニット内のメモリセル上に配置される。

(もっと読む)

不揮発性半導体記憶装置

【課題】フローティングゲート間の電気容量を抑制できる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、直線状の第1のコントロールゲートと、第1のコントロールゲートと隣り合って並走する直線状の第2のコントロールゲートと、第1および第2のコントロールゲートと交差するアシストゲートと、それぞれが第1のコントロールゲートと半導体基板との間に配置されアシストゲートを挟んで互いに隣り合うように配置された第1および第2のフローティングゲートと、第2のコントロールゲートと半導体基板との間に配置された第3のフローティングゲートとを有している。第1のコントロールゲートの直線状に延びる方向に直交する方向を直交方向としたとき、第1および第2のフローティングゲートに挟まれる領域の直交方向に位置する領域に第3のフローティングゲートが配置されている。

(もっと読む)

自己整合相変化材料層を使用する相変化メモリ素子、ならびに、それを製造および使用する方法。

相変化メモリ素子、および、それを形成する方法。このメモリ素子は、第1の電極を支持する基板を含む。絶縁材料構成要素は、第1の電極の上に配置され、また、相変化材料層は、相変化材料層が、第1の電極と電気的につながる(通信する)下表面を有するように、第1の電極の上に絶縁材料構成要素を取り囲んで形成される。メモリ素子は、また、相変化材料層の上表面と電気的につながる第2の電極も有する。  (もっと読む)

(もっと読む)

半導体装置

【課題】SOI構造であり、且つ一括消去可能な新規なNAND型セル構造を提供すること目的とする。また、SOI技術の素子分離技術を適用し、NAND型メモリセルの大容量化、高集積化を目的とする。

【解決手段】浮遊ゲートと制御ゲートを有するメモリ素子が複数直列接続されたNANDセルと、複数のメモリ素子の制御ゲートがそれぞれ接続されているワード線と、消去線と、を有し、複数のメモリ素子の端子は、それぞれ、消去線とダイオード接続されている半導体装置である。ダイオード接続により、複数のメモリ素子の端子を消去線に電気的に接続することにより、消去動作を可能とする。

(もっと読む)

MOSFETゲート電極のランディング・パッドのための構造および方法

マイクロエレクトロニクス・トランジスタおよび製作方法の性能および製造可能性を強化するための新たな技術を提供する。

【課題】

【解決手段】トランジスタ装置およびそれを形成する方法であって、基板と、基板上の第1のゲート電極と、基板上の第2のゲート電極と、第2のゲート電極に重なり合うフランジ付き端部の対を備えるランディング・パッドとを備え、第2のゲート電極の構造は、ランディング・パッドの構造と不連続である。

(もっと読む)

SOIトランジスタならびにバルクトランジスタを備えた半導体デバイスとその製造方法

SOIベースのCMOS回路の、センシティブなRAM領域にバルク状のトランジスタ(151B)を形成することによって、RAM領域はバルクトランジスタ構造に基づいて形成されているので、トランジスタの幅を増加させることにより、あるいはボディ接続をすることによって典型的に考慮されうるヒステリシス効果が削減されることから、有効チップ領域を非常に節約することができる。よって、高速スイッチング速度の恩恵は、CPUコアなどの速度クリティカル回路に維持されると同時に、RAM回路は非常に空間効率的な方法で形成されうる。  (もっと読む)

(もっと読む)

改良された電極を備える電気デバイス

本発明は、第1表面(106)を有する第1電極(104)と前記第1表面から第1の方向(110)に延在するピラーとを備える電気素子を含む電気デバイスに関し、前記ピラーは前記第1表面から前記第1の方向に平行に測った長さを有し、前記第1の方向に直角の断面(116)を有し且つ前記第1の方向に広がり前記ピラーを覆う側壁表面(120)を有している電気デバイスにおいて、前記ピラーに向上した機械的安定性を与えるために、前記ピラーは前記ピラーの長さの少なくとも一部分に沿って延在するへこみ部(120)及び突部(122)の何れか一つを備えることを特徴とする。この電極によればキャパシタ、エッチング蓄積デバイス又はダイオードのような電気素子を改善された特性で費用効果的に形成することができる。  (もっと読む)

(もっと読む)

記憶素子及び記憶装置

【課題】熱による記憶素子へのダメージの発生を抑えて、繰り返し動作を安定して行うことを可能にする記憶素子を提供する。

【解決手段】2つの電極3,6間に記憶層4が配置され、この記憶層4に接して、Cu,Ag,Znから選ばれるいずれかの元素が含まれたイオン源層5が設けられ、記憶層4が、金、銀、イリジウム、ルテニウム、レニウム、白金、パラジウム、ロジウム、オスミウムから選ばれる少なくとも一種以上の元素即ち貴金属元素を含有する酸化物から成る記憶素子10を構成する。

(もっと読む)

不揮発性メモリ素子、その動作方法、及びその製造方法

【課題】低い動作電流、高集積化及び高速度化を提供できる不揮発性メモリ素子、その動作方法及びその製造方法を提供する。

【解決手段】半導体基板を備え、複数の抵抗層は、半導体基板の表面付近にそれぞれ形成され、可変抵抗状態を保存するとき、複数の埋め込み電極は、複数の抵抗層下の半導体基板部分にそれぞれ形成され、複数の抵抗層とそれぞれ連結され、複数のチャネル領域は、隣接する複数の抵抗層間を連結し、隣接する複数の下部電極を連結しないように、半導体基板の表面付近に形成され、ゲート絶縁膜は、半導体基板のチャネル領域上に提供され、ゲート電極は、ゲート絶縁膜上に形成され、複数の抵抗層上を横切って伸張している不揮発性メモリ素子である。

(もっと読む)

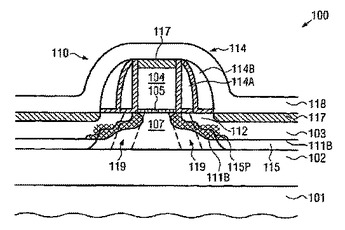

ボディポテンシャルが低減したSOIトランジスタとその製造法

炭素、フッ素などの原子種(111B)をドレイン及びソース領域(115、206)とボディ領域(107、207)とに導入することで、SOIトランジスタ(110、210M)の接合部のリークが著しく増加し、これにより、蓄積した少数電荷キャリアに対してリークパス(119、219A)が強化される。これにより、ボディポテンシャルの変動が著しく減り、その結果、最新のSOIデバイス(100)の全体のパフォーマンスが向上する。具体的な実施形態では、このメカニズムは、スタティックRAM領域(250M)などのしきい値電圧にセンシティブなデバイス領域に選択的に適用することができる。  (もっと読む)

(もっと読む)

不揮発性半導体メモリ

【課題】セル間干渉効果による閾値変動なく、カップリング比を向上させる。

【解決手段】本発明の例に関わる不揮発性半導体メモリは、フローティングゲートFG1,FG2とコントロールゲートCGとを持つスタックゲート構造の第1及び第2メモリセルを備え、第1及び第2のメモリセルのフローティングゲートFG1,FG2は、それぞれ、第1部分FG1と、第1部分FG1上に配置され、コントロールゲートCGが延びる方向における幅が第1部分FG1のそれよりも狭い第2部分FG2とから構成され、第1及び第2メモリセルの第1部分FG1の間の第1スペースには、1種類の絶縁体が満たされ、第1及び第2メモリセルの第2部分の間の第2スペースには、その1種類の絶縁体の誘電率よりも高い誘電率を持つ誘電体を介してコントロールゲートCGが配置される。

(もっと読む)

半導体記憶装置

【課題】6F2セルレイアウトを有する半導体記憶装置において、ストレージキャパシタを最密状態でレイアウトし、しかもHSG閉塞マージンを十分に確保する。

【解決手段】複数の活性領域13は、ワード線14と直交するX方向と約18度をなす直線上に整列しているとともに、ワード線14に平行なY方向に整列している。各活性領域13の両端部及び中央部にはセルコンタクト18が形成される。ストレージノードコンタクト24は活性領域13の両端部に形成されたセルコンタクト18の上方に形成され、その中心位置はセルコンタクト18の中心位置からオフセットされて、ストレージノードコンタクト24は等間隔な千鳥状にレイアウトされる。その後、ストレージノードコンタクトパッド26の中心位置はストレージノードコンタクト24の中心位置からさらにオフセットされて、ストレージノードコンタクトパッド26は等間隔な千鳥状にレイアウトされる。

(もっと読む)

不揮発性記憶素子およびその製造方法

【課題】キャパシタとトランジスタで構成される不揮発性記憶素子は、微細化や高速化が難しい。今後の微細化や高速化に適した不揮発性記憶素子の素子構造が望まれる。

【解決手段】半導体プロセスと親和性のあるプロセスを用いて、下部電極25上に形成された可変抵抗膜26と、可変抵抗膜26上に形成されて可変抵抗膜26の側面を含む全面を覆い、かつ外側に拡大して形成された上部電極27とから記憶部が構成される。さらに、上部電極27の外側に拡大された拡大電極部28に接し、拡大電極部28の下に形成された接続電極29と、下部電極25と接続電極29との側面を埋めて形成される第2の層間絶縁膜30とは記憶部の下部を覆っている。また、記憶部の上部には電極引き出し部および記憶部を覆い、かつ第2の層間絶縁膜30上に形成された第3の層間絶縁膜31が形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】寄生バイポーラとしての動作を防止でき、かつ高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】支持基板1と埋め込み絶縁層2と半導体層3とからSOI基板が構成されている。1poly型メモリセル10は、1対のソース/ドレイン領域11と、フローティングゲート電極層13と、コントロールゲート用不純物拡散領域14とを有している。分離絶縁層6は、半導体層3の表面から埋め込み絶縁層2に達しながらコントロールゲート用不純物拡散領域14の周囲を取り囲むことで、ソース/ドレイン領域11が形成された領域とコントロールゲート用不純物拡散領域14とを分け隔てている。

(もっと読む)

1,741 - 1,760 / 2,405

[ Back to top ]