Fターム[5F083GA21]の内容

Fターム[5F083GA21]に分類される特許

201 - 220 / 791

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼できる非常に小型の記憶素子を含む、3次元集積回路メモリ用の構造を低い製造コストで提供すること。

【解決手段】3次元メモリデバイスは、絶縁材料によって分離され、復号化回路を介してセンスアンプに結合可能なストリングとして配置された複数の隆起した形状スタック含む。ダイオードは、ストリングのストリング選択端部又は共通ソース選択端部のどちらか一方においてビット線構造に接続される。導電材料の帯片は、隆起した形状のスタックのサイドに側面を有する。ワード線として配列された複数の導電線は、行デコーダに結合することができ、複数の隆起した形状のスタックの上で直交して延びる。記憶素子は、スタック上の電導性帯片の側面と導電線との間の交点における界面領域の多層アレイに設けられる。

(もっと読む)

半導体装置

【課題】高集積化を図り、単位面積あたりの記憶容量を増加させた新たな構造の半導体装置を提供することを目的の一とする。高集積化に伴い増加する回路素子数の低減が可能で、かつ、素子数低減による電力削減が可能な、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ビット線と、m(mは3以上の自然数)本のワード線と、ソース線と、m本の信号線と、第1乃至mのメモリセルと、駆動回路と、を有する半導体装置において、メモリセルは、第1のトランジスタ、容量素子に蓄積された電荷を保持する第2のトランジスタを含み、第2のトランジスタは酸化物半導体層で形成されるチャネルを有する。上記構成において、駆動回路は、第j(jは3以上の自然数)の信号線に出力される信号を用いて第(j−1)の信号線に出力される信号を生成する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】周辺回路領域の素子の寿命が劣化するのを抑制しつつ、浮遊ゲート電極と制御ゲート電極とのカップリング性を確保する。

【解決手段】シリコン基板11は、セル領域および周辺回路領域が設けられている。トンネル絶縁膜12は、セル領域および周辺回路領域のシリコン基板11上に形成されている。浮遊ゲート電極膜13は、セル領域および周辺回路領域のトンネル絶縁膜12上に形成されている。電極間絶縁膜16は、セル領域の浮遊ゲート電極膜13上に形成されている。シリコン酸化膜14および電極間絶縁膜16は、周辺回路領域の浮遊ゲート電極膜13上に形成されている。制御ゲート電極膜17は、セル領域および周辺回路領域の電極間絶縁膜16上に形成されている。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】専有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、該記憶ゲートを絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1及び第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された読み出し信号線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】メモリセル間の短絡を防止した上で、活性領域上にシリコン膜が十分に形成された半導体装置を提供する。

【解決手段】半導体基板2の表層に埋め込み形成された素子分離膜8によって、活性領域7が区画された半導体装置1であって、前記活性領域7の側面17が露出するように、前記素子分離膜8の上面の一部が除去されて設けられた凹部と、前記凹部を埋め込みつつ、前記活性領域7の上面7d及び前記側面17と接するように設けられたシリコン膜10と、を有することを特徴とする。

(もっと読む)

Zr−Ge−Ti−OまたはHf−Ge−Ti−Oの誘電材料を備えた物質とその製造方法

【課題】 フィルム、またはRがZrとHfから選択されたR−Ge−Ti−Oを備えた誘電材料とその製造方法を提供する。

【解決手段】 本発明は、RがZrとHfから選択される、R−Ge−Ti−Oのフィルムを備えた誘電材料に関し、また、その製造方法に関連する。誘電材料は、公式Rx−Gey−Tiz−Owを有することが好ましく、ここで、.05≧x≦1、.05≦y≦1、0.1≧z≦1、1≧w≦2、x+y+z≡1であり、さらに好ましくは、0.15≧x≦0.7、.05≧y≦0.3、0.25≧z≦0.7、1.95≧w≦2.05であり、x+y+z≡1である。本発明は、ダイナミック・ランダム・アクセス・メモリ(DRAM)装置のコンデンサを備えたシリコンチップ集積回路装置での使用に特に有用である。

(もっと読む)

不揮発性半導体記憶装置

【課題】ゲート電極間絶縁膜のリーク電流を抑制し、電気的信頼性を向上した不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板上に行列状に形成された複数のメモリ素子と、同一列方向のメモリ素子に選択的に接続される複数のビット線と、同一行方向のメモリ素子に接続される複数のワード線とを具備し、各メモリ素子は、半導体基板上に順次形成された第1のゲート絶縁膜、電荷蓄積層、第2のゲート絶縁膜、制御電極と、電荷蓄積層の対向する側面に沿って、前記シリコン基板上面に形成された1対の不純物注入層とを具備し、ビット線に垂直な方向に沿った断面における電荷蓄積層の上部コーナー部が曲面を有し、上部コーナー部が前記第1のゲート絶縁膜の上方にある。

(もっと読む)

メモリ素子

【課題】低消費電力であり、信頼性の高い不揮発性のメモリ素子を提供する。

【解決手段】電極11上に絶縁層12を間にして非晶質半導体層13が設けられ、非晶質半導体層13表面には電極14および電極15が設けられる。電極15と非晶質半導体層13との間には固体電解質層16が介在している。電極11にパルス電圧を印加すると、可動イオンが固体電解質層16と非晶質半導体層13との間で移動し、非晶質半導体層13の一部の伝導型が変化する。電極14と電極15との間の抵抗状態を選択でき、多値記録が可能である。抵抗変化の原理が第二種相転移であるので、潜熱の放出・吸収、非晶質半導体層の融点を超える温度上昇および体積変化を伴わず、消費電力が低減されると共に、信頼性が向上する。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、キャパシタ誘電体膜の劣化を防止すること。

【解決手段】半導体基板の上方に絶縁膜27を形成する工程と、絶縁膜27の上に、下部電極31a、強誘電体材料を含むキャパシタ誘電体膜32a、及び上部電極33aを備えたキャパシタQを形成する工程と、キャパシタQの側面と上面に、スパッタ法で第2の保護絶縁膜43を形成する工程と、第2の保護絶縁膜43の上に、原子層堆積法により第3の保護絶縁膜44を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

メモリ素子

【課題】低消費電力であり、信頼性の高いメモリ素子を提供する。

【解決手段】半導体層14と可動イオンを含む固体電解質層16との間に非晶質半導体層13を有する。半導体層14と非晶質半導体層13との伝導型が異なる。セットあるいはリセット電圧の印加により、可動イオンが固体電解質層16と非晶質半導体層13との間で移動し、非晶質半導体層13の伝導型が変化することにより、データの書き込み・消去が行われる。伝導型と共に電気抵抗も変化するため、高い抵抗分離特性が得られる。この非晶質半導体層13の変化は第二種相転移であり、潜熱の放出・吸収、非晶質半導体層の融点を超える温度上昇および体積変化を伴わず、消費電力が低く、高い信頼性を示す。

(もっと読む)

抵抗変化素子の駆動方法及び不揮発性記憶装置

【課題】エンデュランス特性の良好な動作が可能な抵抗変化素子の駆動方法を提供する。

【解決手段】第1の極性を有する書き込み電圧パルスを印加することによって、遷移金属酸化物層3の抵抗状態を高抵抗状態から低抵抗状態へ変化させる書き込み過程と、第1の極性とは異なる第2の極性を有する消去電圧パルスを印加することによって、遷移金属酸化物層3の抵抗状態を低抵抗状態から高抵抗状態へ変化させる消去過程と、第1回目の書き込み過程の前に、第2の極性を有する初期電圧パルスを印加することによって、遷移金属酸化物層3に導電パスを形成し初期状態の抵抗値を低下させるブレーク過程と、ブレーク過程の後であって第1回目の書き込み過程の前に、消去電圧パルス以上の電圧値を有する第2の極性を有する追加処理電圧パルスを印加することによって、ブレーク後の遷移金属酸化物層3の抵抗値をさらに低下させる追加処理過程とを有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 フォーミング処理の完了に伴う急峻な電流を抑制することで、特性のばらつきが低減され、安定的にスイッチング動作を行うことが可能な可変抵抗素子、および当該可変抵抗素子を備える不揮発性半導体記憶装置を実現する。

【解決手段】

第1電極12aと第2電極14の間に抵抗変化層13を挟持してなる可変抵抗素子2を情報の記憶に用いる不揮発性半導体記憶装置であり、可変抵抗素子2は、スイッチング界面が形成される第1電極12aと抵抗変化層13の間にバッファ層12bが挿入されてなる。バッファ層12bと抵抗変化層13はともにn型の金属酸化物を含んで構成され、バッファ層12bを構成するn型の金属酸化物の伝導帯の底のエネルギーが抵抗変化層13を構成するn型の金属酸化物のそれよりも低くなるように、バッファ層12aおよび抵抗変化層13の材料が選択される。

(もっと読む)

半導体装置及びその製造方法

【課題】フローティングゲートとコントロールゲートとが積層されたスタック構造のゲート電極を有する半導体装置に関し、隣接メモリセル間やメモリセルとビット線との間における短絡不良を防止しうる半導体装置及びその製造方法を提供する。

【解決手段】トンネルゲート絶縁膜22上に、第1の幅を有する導電膜24、ONO膜28、コントロールゲート40を形成する。コントロールゲート40をマスクとして導電膜24をエッチングしてフローティングゲート26を形成した後、層間絶縁膜80を形成し、第1の方向の幅が第1の幅よりも広いコンタクトホール84を形成する。その後、コンタクトホール84の内壁に、サイドウォールスペーサ88を形成する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ビット線に拡散層を用いる半導体記憶装置のチャネル領域に発生する2次電子を抑制して信頼性を向上できるようにする。

【解決手段】半導体記憶装置100は、P型の半導体基板101の上部にそれぞれが互いに並行に延びるように形成された複数のビット線拡散層108と、半導体基板101の上で、且つそれぞれが各ビット線拡散層108と交差する方向に互いに並行に延びるように形成された複数のワード線電極110とを有している。さらに、半導体基板101における各ワード線電極110の下方の領域には、周囲よりも濃度が低いP型の複数の第3の不純物層111Aがそれぞれ自己整合的に形成されている。

(もっと読む)

半導体記憶装置

【課題】誤書き込みの虞の小さい半導体記憶装置を提供する。

【解決手段】実施の形態の半導体記憶装置は、第1配線と第2配線との間に配置され且つ可変抵抗素子とスイッチング素子を直列接続してなるメモリセルを備える。可変抵抗素子は、低抵抗状態と高抵抗状態との間で抵抗値を変化させるように構成された可変抵抗層を備える。可変抵抗層は、遷移金属酸化物にて構成されている。遷移金属酸化物を構成する遷移金属に対する酸素の割合は、第1配線から第2配線へ向かう第1方向に沿って1:1から1:2までの間で変化する。

(もっと読む)

不揮発性記憶装置及びその製造方法

【課題】高集積化が可能な不揮発性記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る不揮発性記憶装置は、下部電極層と、前記下部電極層上に設けられ、複数の微小導電体が隙間を介して集合したナノマテリアル集合層と、前記ナノマテリアル集合層上に設けられた上部電極層と、を備える。そして、前記上部電極層の少なくとも下部には、前記微小導電体の一部が埋め込まれている。

(もっと読む)

記憶素子および記憶装置

【課題】電圧による抵抗変化の制御性が向上した記憶素子および記憶装置を提供する。

【解決手段】下部電極10、記憶層20および上部電極30をこの順に積層した記憶素子1において、記憶層20は抵抗変化層22と、抵抗変化層22よりも高い抵抗値を示すイオン源層21とを有する。これにより電圧または電流パルスを印加した際の低抵抗部(伝導パス)の形成速度が抑えられ抵抗変化層の抵抗値の変化を緩やかになるため、印加電圧による抵抗値の制御性が向上する。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ特性の劣化を抑制し、かつ耐疲労特性を制御可能とする。

【解決手段】半導体基板10の上方に下部電極16を形成する工程と、下部電極16上に第1誘電体膜18を形成する工程と、酸化性ガスを含む雰囲気中で605℃以上の温度において熱処理することにより、第1誘電体膜18を結晶化する工程と、第1誘電体膜18上に第2誘電体膜20を形成する工程と、第2誘電体膜20を形成した後に熱処理を行なわず上部電極の少なくとも一部の層22を形成する工程と、酸化性ガスを含む雰囲気で熱処理することにより、第2誘電体膜20を結晶化する工程と、第2誘電体膜20および第1誘電体膜18をエッチングする工程と、エッチングする工程の後、側面が露出した状態において酸化性ガスを含む雰囲気中で550℃以上の温度で熱処理する工程と、を含み、第2誘電体膜20の膜厚は第1誘電体膜18の膜厚の30%以上である半導体装置の製造方法。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 隣接メモリセル間の電荷の移動を抑制することができ、メモリセルの電荷保持特性の向上をはかる。

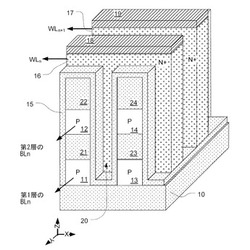

【解決手段】 シリコン基板10上に柱状に形成されたシリコン層70と、シリコン層70を囲むようにトンネル絶縁膜60,電荷蓄積層50,及びブロック絶縁膜40が形成されたゲート絶縁膜部と、ゲート絶縁膜部を囲むように形成され、且つ基板10上に複数の層間絶縁膜20と複数の制御ゲート電極層30が交互に積層された積層構造部とを有し、シリコン層70,トンネル絶縁膜60,電荷蓄積層50,ブロック絶縁膜40,及び制御ゲート電極層30からなる縦型トランジスタでメモリセルを構成した半導体記憶装置であって、電荷蓄積層50は、縦方向に隣接するメモリセル間に電荷蓄積層50のメモリセルに隣接する部分よりもトラップ準位の低い領域を有する。

(もっと読む)

201 - 220 / 791

[ Back to top ]