Fターム[5F083GA21]の内容

Fターム[5F083GA21]に分類される特許

121 - 140 / 791

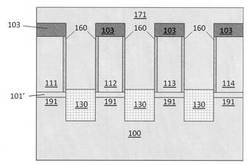

フローティングゲート半導体メモリデバイスおよびそのようなデバイスの製造方法

【課題】NANDフラッシュメモリデバイスを電気的、物理的に小型化し、良好なデータ保持と電気的特性を備えたフローティングゲートデバイスを提供する。

【解決手段】フローティングゲートメモリデバイスの製造方法に関し、ベース基板100、埋め込み絶縁層、および単結晶半導体上部層から形成される、半導体−オン−絶縁体基板が提供される。トレンチが基板中に形成され、フローティングゲートとして働く単結晶上部部分を有する高層フィン型構造111−114を形成する。埋め込み絶縁層の一部は、フローティングゲートデバイスのトンネル酸化物層101’として働く。ゲート誘電体層160は、熱酸化により単結晶上部部分の側壁の上に形成され、薄い膜厚のゲート誘電体層を可能にする。

(もっと読む)

記憶素子および記憶装置

【課題】低電流動作に優れると共に良好な保持特性を有する記憶素子および記憶装置を提供する。

【解決手段】下部電極10、記憶層20および上部電極30をこの順に積層した記憶素子1において、記憶層20はテルルを(Te)を最も多く含む層を有する抵抗変化層22と、アルミニウム(Al)を27.7原子%以上47.4原子%以下の範囲内で含有するイオン源層21とを有する。これにより、消去時に抵抗変化層22中に析出した金属元素がイオン源層21へ溶解しやすくなると共に、書き込みおよび消去後の抵抗状態が維持される。

(もっと読む)

固体メモリ

【課題】固体メモリの記録層として、これまで広く用いられているGe−Sb−Te系合金に代わって、希少金属であるSbフリーでありながら、Ge−Sb−Te系合金を用いた固体メモリと遜色のない性能を有する固体メモリを提供する。

【解決手段】固体メモリ10は、物質の相変化に起因して電気特性が変化する記録層11を備えた固体メモリであって、記録層11が、ゲルマニウムとテルル4とから形成されている薄膜、および、銅とテルルとから形成されている薄膜5が積層されてなる超格子によって構成されている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】信頼性が高い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、アモルファスカーボンを含むカーボンナノマテリアルが隙間を介して集合したナノマテリアル集合層24と、前記ナノマテリアル集合層24の上面に設けられた上部電極層25と、前記ナノマテリアル集合層24の前記上面に対向する下面に直接的又は間接的に設けられた下部電極層23とを備え、前記ナノマテリアル集合層24が含むアモルファスカーボンの量は、前記下面よりも前記上面の方が少ない。

(もっと読む)

半導体装置

【課題】相変化メモリを低電圧動作および高温の動作又は放置させる場合に、記録保持信頼性を向上させる技術を提供する。

【解決手段】読み出し電圧をセット電圧およびリセット電圧以上として高速動作させ、読み出し後に読み出し前の状態を再書込みする、いわゆる破壊読出しを行う。または、複数個のセルを用いて1ビットの情報を記録する、いわゆるオアセルを用いて、高温時の動作又は放置のける信頼性を向上させる。破壊読出しおよびオアセルを用いた相変化メモリに必要な、回路構成および動作方法を用いる。

(もっと読む)

ランダム・アクセス電気的プログラム可能なEヒューズROM

【課題】ランダム・アクセス電気的プログラム可能なeヒューズROMを提供する。

【解決手段】1回プログラム可能な読み出し専用メモリ(OTPROM)が、アグレッシブにスケール縮小された、シリサイド移動可能なeヒューズの2次元配列において実施される。ワード・ライン選択は、VDDにおいて動作するデコード論理によって実施され、一方ビット・ライン・ドライブは、VDDとプログラミングのためのより高い電圧VPとの間でスイッチ切替えされる。OTPROMは、それゆえコストを加算することなしに他の技術と適合可能で、統合することができ、そして、ヒューズ・プログラミングの間、電圧降下を最小にする高電流経路の最適化をサポートする。プログラム可能参照を有する差動センス増幅器は、センス・マージンを改善するために使用され、個々のヒューズに設けられるセンス増幅器の代りに、ビット・ライン全体をサポートすることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ヒータ電極と相変化材料の接触面積を縮小する。

【解決手段】半導体装置1は、スルーホール10aを有する層間絶縁膜10と、スルーホール10a内に設けられた相変化記憶素子P1とを備え、相変化記憶素子P1は、スルーホール10aの内壁に沿って設けられた筒型の導電膜である外部電極OEと、外部電極OEの内壁に沿って設けられ、かつ上端の一部が凹んで凹部11aを構成する筒型の絶縁膜であるバッファ絶縁膜11と、凹部11aの内部を埋める相変化膜GSTと、相変化膜GSTの表面を含むバッファ絶縁膜11の内壁に沿って設けられた導電膜である内部電極IEとを有する。

(もっと読む)

半導体装置

【課題】動作特性に対する信頼性を向上させることができる半導体装置を提供する。

【解決手段】シリコンを含む基板7と、前記基板7上に設けられた積層体6と、を有する半導体装置1であって、前記積層体6は、少なくとも前記積層体6の側壁の前記基板側にフッ素を含む抑制領域13を有している。前記抑制領域13は、基板7上に設けられた絶縁膜2の前記側壁側に設けられ、フッ素濃度は、チャネル領域11のフッ素濃度よりも高い。

(もっと読む)

不揮発性抵抗変化素子

【課題】電極との間で金属の出し入れが行われることで可逆的に抵抗が変化される抵抗変化層の絶縁性の劣化を抑制する。

【解決手段】抵抗変化層2は半導体元素を有し、第2電極4の金属元素が出し入れされることで可逆的に抵抗変化が可能で、誘電体層3は、第2電極4と抵抗変化層2との間に挿入され、抵抗変化層2よりも第2電極4の金属元素の拡散係数が小さい。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

記憶装置及びその製造方法

【課題】高集積化が可能な記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る記憶装置は、下部電極層と、前記下部電極層上に設けられ、複数の微小導電体が隙間を介して集合したナノマテリアル集合層と、前記ナノマテリアル集合層上に設けられ、導電性であり、前記微小導電体に接し、開口部が形成された保護層と、前記保護層上に設けられ、前記保護層に接した上部電極層と、を備える。

(もっと読む)

抵抗変化素子の駆動方法、不揮発性記憶装置、抵抗変化素子および多値記憶方法

【課題】多値の記憶状態を安定して読み書きできる抵抗変化素子の駆動法を提供する。

【解決手段】第1電極2を基準とする第2電極4の電位である電極間電圧を抵抗変化素子10に印加することによって第1電極2と第2電極4との間の抵抗値である電極間抵抗値を可逆的に変化させる抵抗変化素子10の駆動方法であって、Vα<Vβ<0およびVγ>0およびRL<RM<RHを満たすVα、Vβ、Vγ、RL、RM、RHについて、電極間電圧Vαの印加によって電極間抵抗値をRLにする書き込み過程と、書き込み過程の後、電極間電圧Vγの印加によって電極間抵抗値をRMにする第1の消去過程と、第1の消去過程の後、電極間電圧Vβの印加によって電極間抵抗値をRHにする第2の消去過程とを有する。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置、およびその作製方法を提供することである。

【解決手段】基板上に下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、第1の加熱処理を行って第2の酸化物半導体膜を形成した後、選択的にエッチングして、第3の酸化物半導体膜を形成し、第1の絶縁膜および第3の酸化物半導体膜上に絶縁膜を形成し、第3の酸化物半導体膜の表面が露出するように絶縁膜の表面を研磨して、少なくとも第3の酸化物半導体膜の側面に接するサイドウォール絶縁膜を形成した後、サイドウォール絶縁膜および第3の酸化物半導体膜上にソース電極およびドレイン電極を形成し、ゲート絶縁膜およびゲート電極を形成する。

(もっと読む)

半導体装置

【課題】不揮発型抵抗変化素子の低抵抗時の信頼性を向上させる。

【解決手段】少なくとも2つの論理回路15、16と、前段の論理回路15と後段の論理回路16との間を電気的に接続可能とする抵抗変化型不揮発素子14とを備え、抵抗変化型不揮発素子は、抵抗値が電気的に書き換え可能であり、抵抗値が高抵抗状態から低抵抗状態へ遷移するために必要な印加電圧もしくは電流の方向と、低抵抗状態から高抵抗状態へ遷移するために必要な印加電圧もしくは電流の方向とが逆の関係にあるような両極型の遷移特性を有し、前段の論理回路は、前段の論理回路から出力され抵抗変化型不揮発素子を介して流れる信号電流のピーク値が、抵抗変化型不揮発素子が低抵抗状態に遷移する方向に大きく逆方向に小さくなるような駆動能力を有するように構成される。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】フローティングゲート電極を、掘り下げ領域に埋め込んで形成し、ドレイン領域内のトンネル領域と掘り下げ領域に埋め込まれて形成されたフローティングゲート電極の側面との間にトンネル絶縁膜を設ける。

(もっと読む)

記憶装置およびその動作方法

【課題】長期的な信頼性を向上させることが可能な記憶装置およびその動作方法を提供する。

【解決手段】記憶装置1は、印加される電圧の極性に応じて可逆的に抵抗状態が変化する複数の記憶素子21と、駆動対象の記憶素子21の抵抗状態を、低抵抗状態と高抵抗状態との間で選択的に変化させる駆動部とを備えている。この駆動部は、低抵抗状態および高抵抗状態のうちの一方の抵抗状態から他方の抵抗状態へと変化させる第1の動作(セット動作またはリセット動作)を実行する際に、以下の段階的動作を行う。すなわち、第1の動作に関する強ストレス印加工程を実施した後に第2の動作に関する弱ストレス印加工程を実施するというステップを少なくとも1回以上繰り返して行った後、第1の動作に関する強ストレス印加工程を実施する。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

ドープされた相変化材料を形成するための複合ターゲットのスパッタリング

【課題】本発明の主な目的は、相変化材料層を形成する方法を提供することにより、従来の技術でのウエハの表面の汚染、歩留まりの減少という問題を克服することができる。

【解決手段】ケイ素又は他の半導体、或いは、ケイ素系や他の半導体系の添加剤を有する相変化材料層が、ケイ素や他の半導体及び相変化材料を含む複合スパッタターゲットを使用することによって形成される。その複合スパッタターゲットのケイ素または他の半導体の濃度は、形成される前記層におけるケイ素または他の半導体の特定された濃度よりも5倍以上大きい。GST型の相変化材料のケイ素系添加剤に対し、スパッタターゲットは40原子%以上のケイ素を含むことができる。ケイ素系又は他の半導体系の添加剤は、成膜時のスパッタチャンバー内に、酸素や窒素のような反応ガスの流れを伴なう複合スパッタターゲットを用いて形成され得る。

(もっと読む)

半導体装置の駆動方法

【課題】新たな構造の半導体装置、及びその駆動方法を提供することを目的の一とする。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のpチャネル型トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電荷を保持させることで行う。また、保持期間において、メモリセルを選択状態とし、且つ、読み出し用トランジスタのソース電極およびドレイン電極を同電位とすることで、ノードに蓄積された電荷を保持する。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】ノイズによるデータ信号への影響を抑制する半導体記憶装置を提供する。

【解決手段】記憶回路を具備し、記憶回路は、それぞれが電界効果トランジスタであり、1個目の電界効果トランジスタ111a−1のソース及びドレインの一方にデジタルデータ信号が入力され、k個目(kは2以上n(nは2以上の自然数)以下の自然数)の電界効果トランジスタのソース及びドレインの一方がk−1個目の電界効果トランジスタのソース及びドレインの他方に電気的に接続されるn個の電界効果トランジスタと、それぞれ一対の電極を有し、m個目(mはn以下の自然数)の容量素子の一対の電極の一方が、n個の電界効果トランジスタのうち、m個目の電界効果トランジスタのソース及びドレインの他方に電気的に接続され、少なくとも2つの容量素子における容量値が異なるn個の容量素子112aー1〜112aーnとを備える。

(もっと読む)

121 - 140 / 791

[ Back to top ]