Fターム[5F083GA21]の内容

Fターム[5F083GA21]に分類される特許

101 - 120 / 791

半導体装置および半導体装置の製造方法

【課題】埋め込みビットライン型不揮発メモリの微細化に適した製造方法を提供し、かつコンタクトの位置ずれに起因するビットライン間ショートを生じ難い構造を提供する。

【解決手段】導電体膜が埋め込まれたシャロートレンチ溝内にビットライン拡散層を設けてSONOS構造セルとする。これにより、ビットライン拡散層の半導体基板主面上での面積を大きくせずにビットライン拡散層の抵抗を低くすることができ、セル面積を増大させることなく安定した電気的特性の半導体記憶装置が得られる。また、Si3N4のサイドウォールを設けてイオン注入することでビットラインを形成する。これにより、メモリセルの微細化が可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】従来のReRAMを有する半導体装置では、メモリ素子特性にばらつきが生ずるおそれがあった。

【解決手段】基板11を覆う第1の絶縁膜23を形成する工程と、第1の絶縁膜23を貫通する導電プラグ24を形成する工程と、導電プラグ24の上部を一部除去して、導電プラグ24の上面を底面として有し、かつ、一部除去した導電プラグ24に覆われていた部分の第1の絶縁膜23を側壁として有する孔部を形成する工程と、孔部の側壁を覆い、孔部の底面の一部を露出させる側壁絶縁膜25を形成する工程と、孔部の側壁絶縁膜25および底面を覆う可変抵抗膜26を形成する工程と、可変抵抗膜26を覆う導電膜27を形成する工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグ形成時に位置ずれが発生しても水分や不純物が溜まる窪みが発生することがなく、微細化しても長期間にわたる信頼性を確保できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1の絶縁膜121の上に形成された強誘電体キャパシタ131と、強誘電体キャパシタ131を覆う第2の絶縁膜311及びエッチングストッパ膜312と、エッチングストッパ膜312の上面からトランジスタTの不純物領域に到達する第1のコンタクトホール内に導電体材料を充填して形成された第1のプラグ313と、エッチングストッパ膜の上に形成された第3の絶縁膜314と、第3の絶縁膜314の上面から第1のプラグに到達する第2のコンタクトホール内に導電体材料を充填して形成された第2のプラグ315とを有する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を用いた半導体装置であるトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させる。具体的には、酸化物半導体膜を用いたトランジスタのゲート絶縁膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、接合リーク電流を低減可能で、かつトランジスタの信頼性を向上させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート電極61よりも上方に配置されたゲート絶縁膜21、及びゲート電極61の上面61aを覆う水素含有絶縁膜62と、水素含有絶縁膜62を介して、ゲート電極用溝17の上部17Bを埋め込むフッ素含有絶縁膜63と、を備え、ゲート絶縁膜21と接触する第1及び第2の不純物拡散領域65,66の面に、半導体基板13に含まれるシリコンと水素含有絶縁膜62に含まれる水素とが結合したSi−H結合、及び半導体基板13に含まれるシリコンとフッ素含有絶縁膜63に含まれるフッ素とが結合したSi−F結合を有する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、酸化シリコン膜上に、酸化物半導体が結晶状態における化学量論的組成比に対し、酸素の含有量が過剰な領域が含まれている非晶質酸化物半導体層を形成し、該非晶質酸化物半導体層上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体層の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体層を形成する。

(もっと読む)

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

有機分子メモリおよびその製造方法

【課題】メモリセルに流れる電流を制御し、安定した動作と高い信頼性を備える有機分子メモリを提供する。

【解決手段】第1の電極と、第1の電極と異なる材料で形成される第2の電極と、第1の電極と第2の電極との間に設けられる有機分子層であって、有機分子層を構成する抵抗変化型分子鎖の一端が第1の電極と化学結合し、抵抗変化型分子鎖の他端と第2の電極との間に空隙が存在する有機分子層と、を備える有機分子メモリ。

(もっと読む)

不揮発性半導体記憶装置

【課題】上側のメモリセルと下側のメモリセルとの間におけるデータリテンションのばらつきを低減できる不揮発性半導体記憶装置を提供する。

【解決手段】第1のメモリセルMC111は、第1のラインWL11の半導体基板SBと反対側に配されている。第2のラインBL11は、第1のメモリセルMC111を介して第1のラインWL11に交差する。第2のメモリセルMC211は、第2のラインBL11の半導体基板SBと反対側に配されている。第3のラインWL21は、第2のメモリセルMC211を介して第2のラインBL11に交差する。第1のメモリセルMC111は、第1の抵抗変化層R111と第1の整流層D111とを有する。第1の抵抗変化層R111は、カーボン系の材料で形成されている。第2のメモリセルMC211は、第2の抵抗変化層R211と第2の整流層D211とを有する。第2の抵抗変化層R211は、金属酸化物で形成されている。

(もっと読む)

有機分子メモリ

【課題】電荷保持特性に優れた有機分子メモリを提供する。

【解決手段】実施の形態の有機分子メモリは第1の導電層と、第2の導電層と、第1の導電層と第2の導電層との間に設けられ、電荷蓄積型分子鎖または抵抗変化型分子鎖を含み、電荷蓄積型分子鎖または前記抵抗変化型分子鎖が縮合多環系の基を備える有機分子層と、を備えている。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置の面積を削減する。

【解決手段】複数のメモリセル(NMC,DMC)のうち周辺回路領域(PC)に隣接するメモリセル(DMC)と半導体基板(100)との間には、そのメモリセル(DMC)の下部電極(M13)から半導体基板(100)に向けて延伸するコンタクトプラグが形成されていない。第1のコンタクトプラグ(C101)は、半導体基板(100)の平面視において第1のコンタクトプラグの端面の少なくとも一部がメモリセルアレイ(MARY)の周縁よりも内側に配置されるように形成されている。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置の提供。

【解決手段】酸化物半導体材料を用いたトランジスタ162と、酸化物半導体以外の半導体材料を用いたトランジスタ160を組み合わせて用いることにより、書き込み回数にも制限が無く、長期間にわたる情報の保持ができる、新たな構造の半導体装置を実現することができる。さらに、酸化物半導体以外の半導体材料を用いたトランジスタと酸化物半導体材料を用いたトランジスタとを接続する接続電極130bを、当該接続電極と接続する酸化物半導体以外の半導体材料を用いたトランジスタの電極129より小さくすることにより、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることができる。

(もっと読む)

半導体装置

【課題】実動作キャパシタとダミーキャパシタとが形成された半導体装置において、水素・水分、不均一なストレスによる実動作キャパシタの性能劣化を抑制し、FeRAMの寿命特性を向上する。

【解決手段】半導体基板10上の実動作キャパシタ部26の下部電極30と強誘電体膜32と上部電極34を有する複数の実動作キャパシタ36aと、半導体基板10上の実動作キャパシタ部26の外側のダミーキャパシタ部28の下部電極30と強誘電体膜32と上部電極34を有する複数のダミーキャパシタ36bと、複数の実動作キャパシタ36a上の複数の配線40と、複数のダミーキャパシタ36b上の配線40を有し、ダミーキャパシタ36bのピッチの実動作キャパシタ36aのピッチに対する比は、0.9〜1.1の範囲にあり、ダミーキャパシタ36b上の配線40のピッチの実動作キャパシタ36a上の配線40のピッチに対する比は、0.9〜1.1の範囲にある。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

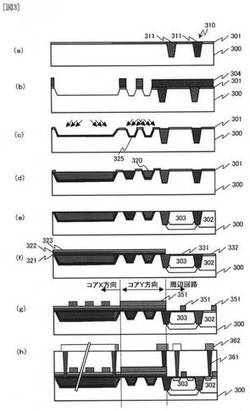

半導体記憶装置およびその作製方法

【課題】半導体記憶装置におけるデータ保持のためのリフレッシュ動作の回数を低減し、消費電力の小さい半導体記憶装置を提供する。また、三次元の形状を適用することで、集積度を高めても短チャネル効果の影響が低減され、かつ従来に比べてフォトリソグラフィ工程数の増加を抑えた半導体記憶装置を提供する。

【解決手段】溝部の設けられた絶縁膜103と、溝部を挟んで離間した一対の電極116と、溝部の側面および底面と接し、溝部の深さよりも厚さの薄い、一対の電極116と接する酸化物半導体膜106と、酸化物半導体膜106を覆うゲート絶縁膜112と、ゲート絶縁膜112を介して酸化物半導体膜106と重畳して設けられたゲート電極112と、を有するトランジスタ150と、キャパシタ160と、を有する半導体記憶装置である。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】可変抵抗素子のデータ保持特性を向上させることのできる半導体記憶装置及びその製造方法を提供する。

【解決手段】一の実施の形態に係る半導体記憶装置は、基板上に配置された複数の第1配線と、第1配線と交差するように配置され、第1配線と基板との間に位置する複数の第2配線と、第1配線と第2配線との各交差部に配置され、電流整流素子及び可変抵抗素子を直列接続してなる第1のメモリセルを含む第1のメモリセルアレイとを備える。第1のメモリセルの可変抵抗素子は、第1の金属材料の酸化物により形成された第1記録層と、第1の金属材料により形成され、且つ、第1記録層と接するように形成された第2記録層とを有する。第2記録層は第1記録層に比べ第1配線に近い側に設けられる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量コンタクトプラグと半導体基板の活性領域との間の重ねマージンを十分に確保して、低抵抗且つ接続信頼性の高い半導体装置を提供する。

【解決手段】埋め込みゲート電極19A及びキャップ絶縁膜20Aと、活性領域1Aの上面に設けられたビットコンタクト27A及びビット線27と、半導体基板1上に設けられた絶縁層32,40と、第1容量コンタクトプラグ39Aと、を備え、第1容量コンタクトプラグ39Aは、柱状部39aとこの柱状部39aの下方に設けられた板状部39bとを有し、板状部39bの底面と、素子分離領域及びキャップ絶縁膜20Aによって区画された活性領域1Aの表面1a,1cとが全面で接触するように設けられていることを特徴とする半導体装置を選択する。

(もっと読む)

チャージトラップインシュレータメモリ装置

【課題】ナノスケールチャージトラップインシュレータメモリ装置において維持特性を向上させ、多数のセル絶縁層を用いて多数のチャージトラップインシュレータセルアレイが垂直方向に積層してセル集積容量を高める技術を開示する。

【解決手段】

多数の上部ワードライン及び下部ワードラインと、多数のビットライン及びセンシングラインと、上部/下部ワードラインとビットラインの交差領域に配置される多数のメモリセルアレイと、チャージトラップインシュレータからビットラインに格納データが出力される多数のメモリセルと、メモリセルをビットライン及びセンシングラインと各々選択的に連結する第1のスイッチング素子及び第2のスイッチング素子とを含み、チャージトラップインシュレータの極性に従い抵抗変化するP型フロートチャンネルと、その両側に形成されたP型ドレイン領域及びP型ソース領域とを含む。

(もっと読む)

101 - 120 / 791

[ Back to top ]