Fターム[5F083GA21]の内容

Fターム[5F083GA21]に分類される特許

41 - 60 / 791

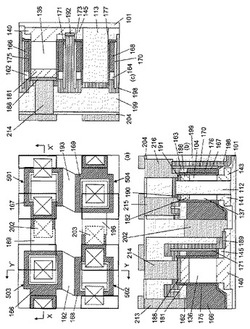

半導体装置

【課題】高集積なCMOS SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

半導体メモリ装置およびその製造方法

【課題】消去、書き込みを繰り返してもON/OFF比を高く維持できる半導体メモリ装置を提供する。

【解決手段】本発明に係る半導体メモリ装置100は、基板10と、基板10の上に形成された炭化シリコン層20と、炭化シリコン層20の上に形成された金属酸化物層30と、金属酸化物層30と電気的に接続された第1電極40と、基板10と電気的に接続された第2電極50と、を含む。

(もっと読む)

抵抗変化型不揮発性記憶素子の書き込み方法および抵抗変化型不揮発性記憶装置

【課題】書き込み動作の安定性および信頼性を向上した抵抗変化型不揮発性記憶素子の書き込み方法を提供する。

【解決手段】抵抗変化素子を含むメモリセルに対して電圧パルスを印加することにより、抵抗変化素子を、印加される電圧パルスの極性によって第1の抵抗状態と第2の抵抗状態とを可逆的に変化させる書き込み方法であって、抵抗変化素子を第2の抵抗状態から第1の抵抗状態に変化せしめる時に、抵抗変化素子に対して、第2の電圧パルス(VL)よりも電圧の絶対値が小さく、かつ、第1の電圧パルス(VH)と極性が異なる第1の抵抗化プレ電圧パルス(VLpr)を印加する第1ステップと、その後、第1の電圧パルス(VH)を印加する第2ステップとを含む第1の抵抗状態化ステップを含む。

(もっと読む)

半導体記憶装置

【課題】書き込み/消去の繰り返しによる信頼性の低下を抑制することが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ウェル上にトンネル絶縁膜を介して形成された浮遊ゲートに蓄積する電荷量を制御することにより電気的にデータを書き換え可能な複数のメモリセルを備える。半導体記憶装置は、前記ウェル、及び前記浮遊ゲート上に絶縁膜を介して形成された制御ゲートに、電圧を印加する制御回路を備える。

前記メモリセルの消去動作において、前記制御回路は、第1の消去電圧が階段状に上昇する第1のパルス波を、前記ウェルに印加し、その後、第2の消去電圧の第2のパルス波を、前記ウェルに印加する。

(もっと読む)

半導体記憶装置

【課題】データ保持特性に対する信頼性を回復させることができる半導体記憶装置を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、それぞれ複数の絶縁膜及び電極膜が交互に積層された積層体と、前記積層体を貫く半導体ピラーと、前記電極膜と前記半導体ピラーとの間に設けられた電荷蓄積層と、前記電荷蓄積層と前記半導体ピラーとの間に設けられたトンネル層と、前記積層体の積層方向に対して直交する一の方向において、前記半導体ピラー同士の間に設けられた前記電極膜を分離する分離溝と、前記分離溝の内部に設けられた加熱部と、を備えている。

(もっと読む)

半導体装置の製造方法

【課題】同一セル内に複数設けられたビットへの個々への書き込み動作が他ビットへの書き込み量に依存することなく正常に行われ、さらには、書き込み・読み出し特性を損なうことなくSONOS構造セルのいっそうの微細化を可能とする半導体装置およびその製造方法を提供する。

【解決手段】本発明による半導体装置は、一対の第1拡散領域を有する基板と、該基板上に形成された酸化膜および該酸化膜上に形成された電荷蓄積層とを有するゲート部とを有し、前記電荷蓄積層は当該電荷蓄積層中に離隔して位置する複数のビット領域を有する電気的絶縁膜である。また、酸化膜は、ビット領域に対応する部分がトンネル酸化膜として作用する膜厚の薄膜部およびビット領域間に位置する部分がトンネル効果による電荷輸送を抑制する膜厚の厚膜部を有している。

(もっと読む)

抵抗変化型素子の抵抗状態変化方法

【課題】素子の耐久性の向上を図る。

【解決手段】抵抗変化型素子20に1回以上の第1のパルス電圧を印加することによって抵抗変化型素子20の抵抗状態を高抵抗状態から低抵抗状態に切り替えるセットと、抵抗変化型素子20に1回以上の第1のパルス電圧とは異なる第2のパルス電圧を印加することによって抵抗変化型素子20の抵抗状態を高抵抗状態から低抵抗状態に切り替えるリセットと、の実行によって抵抗変化型素子20の抵抗状態を変化させるものにおいて、リセットを実行する際には、第2のパルス電圧のパルス幅を徐々に大きくする。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

半導体装置

【課題】一定時間電力が供給されない状況でも記憶内容の保持が可能な半導体装置を提供すること。さらに、半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させること。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料として、ワイドバンドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、トランジスタの下に設けた配線層と、酸化物半導体膜の高抵抗領域と、ソース電極とを用いて容量素子を形成することで、トランジスタと容量素子の占有面積の低減を図る。

(もっと読む)

相変化メモリ

【課題】三次元構造を有する相変化メモリの熱ディスターブを抑制する。

【解決手段】三次元構造を有する相変化メモリにおいて、選択用MOSトランジスタのゲート絶縁膜として、高い熱伝導率を有する材料を使用し、相変化記録膜からSiチャネル層に伝達する熱を良好にゲート電極に拡散させる。これにより、記録ビットから発生する熱が非選択の隣接ビットに拡散し、隣接ビットのデータを消去する熱ディスターブを抑制する。高い熱伝導率を有するゲート絶縁膜材料としては、BN、Al2O3、AlN、TiO2、Si3N4、ZnOなどを挙げることができる。

(もっと読む)

不揮発性メモリ要素及びこれを含むメモリ素子

【課題】不揮発性メモリ要素及びこれを含むメモリ素子を提供する。

【解決手段】両電極の間にメモリ層を含み、該メモリ層は複数層構造を持つ不揮発性メモリ要素である。メモリ層は、ベース層及びイオン種交換層を含み、これらの間のイオン種の移動による抵抗変化特性を持つ。イオン種交換層は、少なくとも2つの層を含む複数層構造を持つ。不揮発性メモリ要素は、複数層構造のイオン種交換層によりマルチビットメモリ特性を持つ。ベース層は酸素供給層であり、イオン種交換層は酸素交換層である。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

導電性側壁スペーサを有する不揮発性メモリ装置及びその製造方法

【課題】従来の窒化膜側壁を電荷トラップ媒体に利用する場合の信頼性劣化を改善した不揮発性メモリ装置を提供する。

【解決手段】半導体基板21上のゲート絶縁膜22Aと、該ゲート絶縁膜上に順に積層して形成された第1電極膜23、第2電極膜24、及びハードマスク膜25を有するゲート100と、該ゲートの第1電極膜23及び第2電極膜24の両側壁に形成された一対の再酸化側壁スペーサ27と、該再酸化側壁スペーサ及びゲート100のハードマスク膜25の両側壁上に形成された一対の側壁スペーサ28Aと、一対の側壁スペーサ28A上に形成された、電荷を捕獲及び放出する一対の導電性側壁スペーサ29Bと、半導体基板21内に形成された一対のLDD領域26と、半導体基板21内に形成されたソース/ドレイン領域30とを備え、導電性側壁スペーサ29Bが、ゲート100及び側壁スペーサ28Aよりも低い高さを有する。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、犠牲絶縁膜に形成された孔に導電膜を形成し、その後、犠牲絶縁膜を除去後に、導電膜への炭素成分に起因する残渣の付着を抑制することで、半導体装置の歩留まりを向上可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】炭素成分を含まない原料を用いた成膜方法により、半導体基板の表面に犠牲絶縁膜を形成する工程と、犠牲絶縁膜を貫通する孔を形成する工程と、犠牲絶縁膜のうち、前記孔の側壁部分を覆う導体膜を形成する工程と、犠牲絶縁膜を除去する工程と、を有する。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】消費電力の増大を抑制し且つ微細化を達成した半導体装置および当該半導体装置の作製方法を提供する。また、安定した電気的特性が付与された、信頼性の高い半導体装置および当該半導体装置の作製方法を提供する。

【解決手段】酸化物半導体膜に電界で加速されたイオンを照射して、当該酸化物半導体膜の表面の平均面粗さを低減することにより、トランジスタのリーク電流の増大および消費電力の増大を抑制することができる。さらに、加熱処理を行って、酸化物半導体膜が当該酸化物半導体膜表面に垂直なc軸を有する結晶を含むように形成することにより、酸化物半導体膜の可視光や紫外光の照射による電気的特性の変化を抑制することができる。

(もっと読む)

半導体装置の作製方法

【課題】トランジスタの微細化を達成し、電界緩和がなされた、酸化物半導体を用いた半導体装置を提供することを課題の一とする。

【解決手段】ゲート電極の線幅を微細化し、ソース電極層とドレイン電極層の間隔を短縮する。ゲート電極をマスクとして自己整合的に希ガスを添加し、チャネル形成領域に接する低抵抗領域を酸化物半導体層に設けることができるため、ゲート電極の幅、即ちゲート配線の線幅を小さく加工しても位置精度よく低抵抗領域を設けることができ、トランジスタの微細化を実現できる。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供と、さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図る。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

41 - 60 / 791

[ Back to top ]