Fターム[5F083GA21]の内容

Fターム[5F083GA21]に分類される特許

141 - 160 / 791

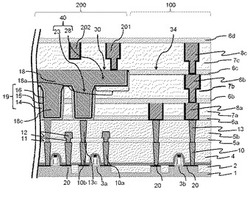

半導体装置及び半導体装置の製造方法

【課題】容量素子の容量の増大が実現される半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、半導体基板1内の記憶回路領域に形成されており、多層配線層内に設けられた凹部40内に埋め込まれた少なくとも1以上の容量素子19および周辺回路を有する記憶回路200と、平面視において、半導体基板1内の記憶回路領域とは異なる領域である論理回路領域に形成された論理回路100と、当該凹部40内において、下部電極14、容量絶縁膜15、及び上部電極16から構成される前記容量素子19上に積層している上部接続配線18と、容量素子19が埋め込まれている配線層のうち最上層に設けられた論理回路100を構成する配線8bの上面に接するように設けられたキャップ層6cと、を備え、上部接続配線18の上面30とキャップ膜6cの上面34とが、同一面を構成している。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】良好な電気特性及び信頼性を有する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板と、半導体基板に形成された素子分離溝に埋め込まれた素子分離絶縁膜と、素子分離溝により所定間隔だけ隔てられ、且つ、半導体基板上に第1の絶縁膜と電荷蓄積膜とが順次積層されてなる積層構造の複数のメモリセルと、電荷蓄積膜と素子分離絶縁膜との上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された制御電極膜とを有し、素子分離絶縁膜の上面は電荷蓄積膜の上面よりも低く、第2の絶縁膜は、電荷蓄積膜上のセル上部分と素子分離絶縁膜上のセル間部分とを備え、セル上部分の誘電率はセル間部分の誘電率よりも低い。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】支持基板上に絶縁層を形成し、当該絶縁層上に高純度化された酸化物半導体と、SOI(Silicon On Insulator)基板である単結晶シリコンを用いて半導体装置を構成する。高純度化された酸化物半導体を用いて構成したトランジスタは、リーク電流が極めて小さいため、長期間にわたって情報を保持することが可能である。また、SOI基板を用いることにより、絶縁層上に形成された薄い単結晶シリコンの特長を生かすことで、トランジスタを完全空乏型とすることができるため、高集積、高速駆動、低消費電力など付加価値の高い半導体集積回路が実現できる。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】トンネル領域を有する半導体不揮発性メモリにおいて、トンネル領域の周囲部分は掘り下げられており、掘り下げられたドレイン領域には、空乏化電極絶縁膜を介して、トンネル領域の一部を空乏化するための電位を自由に与えることが可能な空乏化電極を配置する。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体膜を薄膜化して低電圧の動作を可能にしつつ、飽和反転電荷量を増大ささせる。

【解決手段】半導体装置は、下部電極41と、強誘電体膜36と、上部電極35とから形成されるキャパシタ42を有する。強誘電体膜36は、PZTから形成され、膜厚方向の中央部分のTiの含有量が他の領域の比べて多くなっている。Tiの分布は、膜厚方向の中央から上下の電極35,41に向けて減少するような分布である。さらに、Srなどのドーパント元素の含有量が、下部電極41との界面で最も多く、上部電極35に向けて減少する分布を有する。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】DRAMの微細化及び高集積化により、プロセス低温化が進み、400〜500℃熱処理による基板内の酸素ドナー化による電子発生量が多くなってきた。そのため、基板深くに形成されるウェル同士の分離耐圧が厳しくなり、デバイス劣化を引き起こしてしまう。

【解決手段】P型半導体基板11の表面から0.2〜1μmの範囲の深さに2E+17atom/cm3以上のピーク濃度を有するNウェル層12の下方に、P型半導体基板11中に発生するキャリア電子濃度より高濃度のP型不純物を含有する空乏層拡大防止層17を有する半導体装置。

(もっと読む)

半導体不揮発性メモリ装置

【課題】 占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】 ドレイン領域内のトンネル領域と微細穴に埋め込まれる形で形成されたフローティングゲート電極の側面との間にはトンネル絶縁膜を設け、微細穴に接するドレイン領域の表面付近には、電気的にフローティング状態である第1導電型のトンネル防止領域を設けた。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】ドレイン領域内のトンネル領域には、ドレイン領域と同一の電位に固定されたドレイン領域に比べて不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域とを形成し、不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域のそれぞれの上面に、フローティングゲート電極への電子注入用と電子引き抜き用のトンネル絶縁膜を独立して設けた。また、データ書き換え時に印加されるストレスが偏らないように、電子引き抜き用のトンネル絶縁膜に比べて電子注入用のトンネル絶縁膜の面積を大きくあるいは厚くした。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】複数のメモリセルを3次元状に配置し、かつ、メモリセルにMONOS型トランジスタを使用するNAND型不揮発性メモリにおいて、データ保持特性の劣化を抑制することができる技術を提供する。

【解決手段】ギャップ絶縁層GIL1の右端部側に凹部CUが形成されている。このとき、この凹部CUの形状を反映するように、凹部CUの内部に上部電位障壁層EB2と電荷蓄積層ECが形成されており、この凹部CUの形状を反映した電荷蓄積層ECの内側に形成される下部電位障壁層EB1によって、凹部CUが完全に埋め込まれている。このため、凹部CUを埋め込んだ下部電位障壁層EB1の表面は平坦になっており、この平坦になっている下部電位障壁層EB1の内側に柱状半導体部PSが形成される。

(もっと読む)

記憶素子およびその製造方法、並びに記憶装置

【課題】良好な絶縁耐圧性を有する記憶素子を提供する。

【解決手段】下部電極、記憶層および上部電極をこの順に有し、記憶層は、抵抗変化層とイオン源層とにより構成されている。イオン源層は可動イオンとなる元素を含み、上部電極および下部電極に電圧を印加すると、記憶層の抵抗値が変化して情報を記憶する。抵抗変化層はフッ化マグネシウムなどのフッ化物を含有する。または、下部電極がフッ素またはリンを含有する。これにより、抵抗変化層は電圧印加の影響を受けにくく、抵抗変化層の劣化に起因するメモリ特性の低下が抑制される。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】Y方向に延在するように半導体基板13に設けられ、底面18c及び対向する第1及び第2の側面18a,18bを有するゲート電極用溝18と、ゲート絶縁膜21を介して、ゲート電極用溝18の下部を埋め込むように配置されたゲート電極22と、ゲート電極用溝18を埋め込むように配置され、ゲート電極22の上面22aを覆う埋め込み絶縁膜24と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆うように、半導体基板13に設けられた第1の不純物拡散領域28と、少なくとも第2の側面18bに配置されたゲート絶縁膜21を覆うように、半導体基板13に設けられた第2の不純物拡散領域29と、を有する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル領域とフローティングゲート電極との間には、膜厚の異なる複数のトンネル絶縁膜を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】フローティングゲート電極は、高い不純物濃度領域と低い不純物濃度領域とからなり、高い不純物濃度領域は、コントロールゲート絶縁膜と接する部分に配置し、低い不純物濃度領域はトンネル絶縁膜と接する領域に配置し、フローティングゲート電極のコントロールゲート絶縁膜と接する表面部分には微細凹凸を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル領域のエッジ近傍のトンネル絶縁膜上には、トンネル絶縁膜とは異なる材質の絶縁膜からなる電界緩和層を配置した。

(もっと読む)

不揮発性記憶素子及びその製造方法

【課題】 信頼性を向上可能な不揮発性記憶素子及びその製造方法を提供する。

【解決手段】 不揮発性素子は、基板100、基板100の上に形成され、制御ベースゲート120a及び制御ベースゲート120aの上に形成される制御金属ゲート125anを有する制御ゲート電極137、制御ゲート電極137と基板100との間に形成される電荷格納領域110a、制御ゲート電極137の上に形成される制御ゲートマスクパターン130、及び制御ゲートマスクパターン130及び制御ベースゲート120aの間に形成された制御金属ゲート125aの側壁の上に形成される酸化防止スペーサ135aを備える。このとき、制御金属ゲート125anの幅は、制御ゲートマスクパターン130の幅より小さくなるように形成されている。これにより、制御金属ゲート125anが酸化工程又は酸化物等によって酸化されることを防止することができる。

(もっと読む)

半導体記憶装置

【課題】メモリセルの特性の劣化を抑制した半導体記憶装置を提供する。

【解決手段】メモリセルは、ダイオード層、可変抵抗層、及び電極層を備える。ダイオード層は、整流素子として機能する。可変抵抗層は、可変抵抗素子として機能する。電極層は、可変抵抗層とダイオード層との間に設けられ、可変抵抗層及びダイオード層に接するように形成されている。電極層は、窒化チタンにて構成された窒化チタン層を備える。ここで、窒化チタン層内の第1領域における窒素原子に対するチタン原子の割合を第1割合とし、窒化チタン層内であって且つ第1領域よりも可変抵抗層に近い第2領域における窒素原子に対するチタン原子の割合を第2割合とする。この場合、第2割合は第1割合よりも大きい。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】浮遊ゲート電極の細りを補償して信頼性を向上させた不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置10では、第1の幅W1を有する活性領域12が、半導体基板11の主面に形成された素子分離層13で分離されている。第1ゲート絶縁膜14が、活性領域12に形成されている。第1の幅W1より狭い第2の幅W2を有する第1導電層15aが、第1ゲート絶縁膜14を介して活性領域12に形成されている。第1の幅W1と第2の幅W2の差を補償するように第3の幅W3を有する第2導電層15aが第1導電層15aの側壁に形成されている。第1ゲート電極15は、第1導電層15aと第2導電層15bを含んでいる。第2ゲート絶縁膜16が、第1ゲート電極15および素子分離層13上にコンフォーマルに形成されている。第2ゲート電極17が、第2ゲート絶縁膜16上に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

141 - 160 / 791

[ Back to top ]