Fターム[5F083JA02]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104)

Fターム[5F083JA02]の下位に属するFターム

酸化膜を含む複合膜 (2,564)

酸化窒化膜 (1,013)

タンタル酸化膜(Ta2O5) (705)

ハロゲンを含む酸化膜 (7)

複酸化物 (3,106)

Fターム[5F083JA02]に分類される特許

181 - 200 / 1,709

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、単位面積あたりの記憶容量を増加させる。

(もっと読む)

記憶装置

【課題】リフレッシュ動作の回数を減らすことで、消費電力を抑える。また、先に書き込んだデータを破壊することなく、データを読み出す。

【解決手段】ソースまたはドレインの一方となる第1の電極と、ソースまたはドレインの他方となる第2の電極と、第1のチャネル形成領域に絶縁膜を介して重畳して設けられた第1のゲート電極と、を有する第1のトランジスタと、ソースまたはドレインの一方となる第3の電極と、ソースまたはドレインの他方となる第4の電極と、第2のチャネル形成領域が第2のゲート電極と第3のゲート電極との間に絶縁膜を介して設けられた第2のトランジスタと、を有するメモリセルを複数有し、第1のチャネル形成領域及び第2のチャネル形成領域は、酸化物半導体を含んでおり、第2の電極は、第2のゲート電極に直接接続されている記憶装置とする。

(もっと読む)

半導体装置及びその駆動方法

【課題】信号処理回路に対する電源電圧の供給及び遮断を選択することができるスイッチとして機能する回路(電源供給制御回路)として好ましい回路を提供する。

【解決手段】信号処理回路に対する電源電位の供給を担う第1の配線と、電源電位を供給する第2の配線との電気的な接続を制御するトランジスタ、及び、信号処理回路に対する電源電位の供給を担う第1の配線を接地させるか否かを制御するトランジスタとを設け、当該2つのトランジスタの少なくとも一方として、チャネルが酸化物半導体層に形成されるトランジスタを適用する。これにより、2つのトランジスタの少なくとも一のカットオフ電流に起因する消費電力を低減することが可能となる。

(もっと読む)

記憶装置、及び半導体装置

【課題】プロセスを複雑化させることなく、単位面積あたりの記憶容量を高めることができる記憶装置を提案する。

【解決手段】複数のメモリセルと、複数のワード線と、複数のビット線とを有し、複数のメモリセルは、スイッチング素子と、第1の電極及び第2の電極を有する容量素子と、をそれぞれ有し、複数のメモリセルの少なくとも1つにおいて、複数のワード線のうち一のワード線に与えられる電位に従って、スイッチング素子が複数のビット線のうち一のビット線と第1の電極の接続を制御し、なおかつ、第2の電極が複数のワード線のうち一のワード線とは異なる一のワード線に接続されている記憶装置。

(もっと読む)

半導体装置およびその駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のチャネル形成領域と、第1のゲート電極と、第1のソース領域およびドレイン領域と、を有する第1のトランジスタと、少なくとも第1のソース領域またはドレイン領域の一部と重畳するように設けられた、酸化物半導体材料からなる第2のチャネル形成領域と、第2のソース電極と、第1のゲート電極に電気的に接続される第2のドレイン電極と、第2のゲート電極と、を有する第2のトランジスタと、第1のトランジスタと第2のトランジスタとの間の絶縁層と、を含むメモリセルを有し、第2のトランジスタをオフ状態とすべき期間において、少なくとも第1のソース領域またはドレイン領域に正の電位が与えられるときに第2のゲート電極に負の電位が与えられる半導体装置。

(もっと読む)

半導体装置の駆動方法

【課題】半導体装置の駆動方法を提供する。

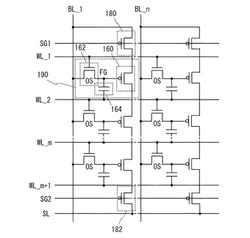

【解決手段】ビット線と、選択線と、選択トランジスタと、m(mは2以上の自然数)本の書き込みワード線と、m本の読み出しワード線と、ソース線と、第1乃至mのメモリセルと、を有する半導体装置において、メモリセルは、第1のトランジスタ、容量素子に蓄積された電荷を保持する第2のトランジスタを含み、第2のトランジスタは酸化物半導体層で形成されるチャネルを有する。上記構成の半導体装置の駆動方法において、メモリセルに書き込みを行う場合、第1のトランジスタを導通させて第1のソース端子または第1のドレイン端子を固定電位とし、容量素子に安定した電位の書き込みを行う。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体装置、記憶装置および半導体装置の作製方法

【課題】書き込み回数に制限がなく、消費電力が低く、記憶内容(電荷)の保持特性が改善され、かつ小型化に適した構造の半導体装置および、当該半導体装置を備える、消費電力が低く、記憶内容(電荷)の保持特性が改善された記憶装置を提供する。

【解決手段】半導体装置の有するトランジスタの半導体層として酸化物半導体を用いることで、ソースとドレイン間のリーク電流を低減できるため、半導体装置および当該半導体装置を備える記憶装置の消費電力低減、保持特性の改善を達成できる。また、トランジスタのドレイン電極、半導体層およびドレイン電極と重なる第1の電極により容量素子を形成し、容量素子と重なる位置でゲート電極を上層へ取り出す構造とした。これにより、半導体装置および当該半導体装置を備える記憶装置を小型化できる。

(もっと読む)

半導体装置

【課題】ワード線の負荷を増大させることなく、ワード線に生じるノイズを低減する。

【解決手段】少なくとも一のスイッチング素子を有する複数の記憶素子がマトリクス状に配置され、前記記憶素子のそれぞれにはワード線とビット線がそれぞれ接続され、前記ワード線には少数キャリアが実質的に存在しないトランジスタのゲート(またはソース及びドレイン)が接続され、前記少数キャリアが実質的に存在しないトランジスタのソース及びドレイン(またはゲート)の電位が制御されることで前記少数キャリアが実質的に存在しないトランジスタの容量値の制御を行う半導体装置とする。前記少数キャリアが実質的に存在しないトランジスタは、ワイドギャップ半導体により設けられていればよい。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の電気的性能および信頼性を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGは、金属膜6aと金属膜6a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極であり、金属膜6aの上端部には、金属膜6aの一部が酸化することで金属酸化物部分17が形成されている。スプリットゲート型の不揮発性メモリの制御ゲート電極は、金属膜4aと金属膜4a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極である。

(もっと読む)

選択トランジスタ、選択トランジスタの作成方法、メモリ装置及びメモリ装置の製造方法

【課題】少ない工程数で製造でき、フラットバンド電圧のシフトを抑制できる選択トランジスタ、選択トランジスタの作成方法、メモリ装置及びメモリ装置の製造方法を提供すること。

【解決手段】直列接続された複数のメモリトランジスタを備えたメモリ装置で用いられる選択トランジスタであって、半導体基板上に形成されたトンネル絶縁層と、トンネル絶縁層上に形成された電荷蓄積層と、電荷蓄積層上に形成され、アルゴンをソースガスとするガスクラスタイオンビームが照射されたブロッキング絶縁層と、ブロッキング絶縁層上に形成されたゲート電極と、ゲート電極の両側の半導体基板中に形成されたソース/ドレイン領域と、を具備する。

(もっと読む)

高誘電性ナノシート積層体、高誘電性ナノシート積層体、高誘電体素子、および高誘電体薄膜素子の製造方法

【課題】コンデンサなどに好適な、非常に薄くしても高い誘電率と良好な絶縁特性を同時に実現する高誘電体薄膜を提供する。

【解決手段】上記課題は、ペロブスカイト構造を有する酸化物ナノシートなどの高誘電体により構成される薄膜により達成される。

(もっと読む)

半導体装置

【課題】半導体集積回路の微細化に伴い非常に短くなったゲート長を有するトランジスタにおいて、ゲート絶縁膜におけるリーク電流の発生を抑制し、トランジスタとしての機能を高めることが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面に形成された1対のソース/ドレイン領域と、1対のソース/ドレイン領域に挟まれる領域上であって、主表面に接するように形成されたゲート絶縁膜AFEと、ゲート絶縁膜AFEの上面に接するように形成されたゲート電極POとを備える。上記1対のソース/ドレイン領域の一方から他方へ向かう方向のゲート電極POの長さは45nm未満である。ゲート絶縁膜AFEは反強誘電体膜を有する。

(もっと読む)

半導体記憶装置

【課題】不揮発性の記憶装置を有するCAMとする際に、メモリセルの低消費電力化を図ることのできる半導体記憶装置を提供することを課題の一とする。また、データの書き込みを繰り返し行う際の劣化をなくすことができる半導体記憶装置を提供することを課題の一とする。また、メモリセルの高密度化が可能な不揮発性の記憶装置を提供する。

【解決手段】酸化物半導体を半導体層に有する第1のトランジスタ及び当該第1のトランジスタをオフ状態とすることで書き込んだデータに対応する電位を保持できる容量素子を有するメモリ回路と、書き込んだ電位を参照するための参照回路を有し、参照回路を構成する第2のトランジスタの導通状態を検出することで、整合するデータのアドレスを取得し、高速な検索機能を可能にした半導体記憶装置である。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート

電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第

2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジ

スタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトラ

ンジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

パターン形成方法

【課題】微細なパターンと比較的サイズが大きめのパターンとを有するパターン形成方法で、サイズが大きめのパターンを従来に比して精度良く形成することができるパターン形成方法を提供する。

【解決手段】実施形態によれば、加工対象上の芯材膜31に開口を形成した後、マスク膜32をコンフォーマルに形成する。マスク膜32をエッチバックして芯材膜31の側面に第1の幅のマスク膜32を残す。開口の形成領域以外の領域にレジストパターン35aを形成し、これをマスクに芯材膜31をエッチングする。さらに、芯材膜31をスリミングして第1の幅より小さい第2の幅のラインアンドスペース状のパターンを形成する。側壁膜をコンフォーマルに形成した後、エッチバックし、さらに芯材膜31を除去して、加工対象上に側壁膜からなる側壁パターンを形成する。そして側壁パターンで加工対象をエッチングする。

(もっと読む)

ダイオードストラッピングを備えた熱アシストフラッシュメモリ

【課題】フラッシュメモリの動作速度及び耐久性を向上させる技術の提供。

【解決手段】メモリが、行及び列を含むメモリセルのアレイを有している。該メモリは、アレイ内の単数又は複数のワード線上の第1の離隔位置のセットに第1のバイアス電圧を印加するとともに、単数又は複数のワード線上の第2の離隔位置のセットに第1のバイアス電圧とは異なる第2のバイアス電圧を印加する、ワード線に結合された回路部を有し、第1の離隔位置のセットにおける位置は、第2の離隔位置のセットの位置の間に介在しており、それにより、第1の離隔位置のセットにおける位置と第2の離隔位置のセットにおける位置との間に、単数又は複数のワード線の加熱をもたらす電流の流れが誘導される。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜(第1の結晶性酸化物半導体膜ともいう)を形成し、該酸化物半導体膜に酸素を導入して少なくとも一部を非晶質化し酸素を過剰に含む非晶質酸化物半導体膜を形成する。該非晶質酸化物半導体膜上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体膜の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜(第2の結晶性酸化物半導体膜ともいう)を形成する。

(もっと読む)

181 - 200 / 1,709

[ Back to top ]