Fターム[5F083JA02]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104)

Fターム[5F083JA02]の下位に属するFターム

酸化膜を含む複合膜 (2,564)

酸化窒化膜 (1,013)

タンタル酸化膜(Ta2O5) (705)

ハロゲンを含む酸化膜 (7)

複酸化物 (3,106)

Fターム[5F083JA02]に分類される特許

341 - 360 / 1,709

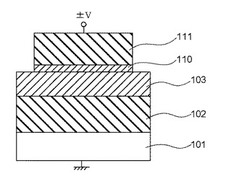

半導体記憶装置及びその製造方法

【課題】半導体記憶装置におけるトランジスタの特性向上と、キャパシタのリーク電流特性の両方を改善し、高信頼、高歩留のデバイスを提供する。

【解決手段】窒化チタンからなる下部電極102上に酸化ジルコニウムを主成分とする誘電体膜103を有するキャパシタにおいて、微結晶状態の酸化ジルコニウムを主成分とする誘電体膜を成膜し、2次的な結晶粒成長を伴わない条件でチタン化合物を主成分とする第一の保護膜110を形成し、その後、上部電極111を形成することで、上部電極形成時に伴う熱処理を行っても、またトランジスタの界面準位を低減する水素アニールを行っても、リーク電流の増大を抑制できる。

(もっと読む)

半導体装置の駆動方法

【課題】信頼性の高い書き込み動作を高速に行うことのできる半導体装置の駆動方法を提供する。

【解決手段】多値書き込みを行う半導体装置の駆動方法において、酸化物半導体層を含むトランジスタを用いたメモリセルに、書き込みを行う書き込みトランジスタのオンオフを制御する信号線を、ビット線に沿うように配置し、読み出し動作時に容量素子に与える電圧を書き込み時にも利用して、多値書き込みを行う。書き込みを行いながらビット線の電位を検知することによって、書き込みベリファイ動作を行うことなく、書き込みデータに対応した電位がフローティングゲートに正常に与えられたかを確認することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】立体構造キャパシタを備えた半導体装置であって、上下部電極に金属若しくは金属化合物を用いるMIM構造で、容量絶縁膜に高誘電体膜を用いるキャパシタにおいて、高誘電率でリーク電流が抑制された信頼性の高いキャパシタを備える半導体装置を提供する。

【解決手段】TiN下部電極102上に酸化ジルコニウム誘電体膜113を形成し、誘電体膜上にTiNを含む上部電極117を形成する際、誘電体膜をALD法で形成し、上部電極を形成する前に誘電体膜形成時のALD法の成膜温度を70℃以上超える温度を付加することなく、第一の保護膜116を成膜する。

(もっと読む)

半導体装置及びその製造方法

【課題】更なる微細化に対応した高集積度のDRAMを得ることが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2の表層に、第1の方向Yに延在する第1の溝部3と、第2の方向Xに延在し且つ第1の溝部3よりも深くなる第2の溝部5と、第1の溝部3と第2の溝部5との交差部分において第2の溝部5よりも深くなる第3の溝部7と、第1の溝部3と第2の溝部5との間から突出されたピラー部8と、ピラー部8に形成された下部拡散層9、チャネル領域10及び上部拡散層11と、第2の溝部5の内側において第2の方向Xに延在するビット配線層と、第1の溝部3の内側においてピラー部8の側面を覆うゲート絶縁膜と、第1の溝部3の内側においてゲート絶縁膜を介してピラー部8の側面を横切るように第1の方向Yに延在するワード配線層とを備える。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな半導体装置を提供する。また、回路規模を縮小し、書き込み、読み出しに対する信頼性を向上させる。

【解決手段】酸化物半導体層を含むトランジスタを用いたメモリセルに対して、ベリファイ動作と、読み出しを行う際に、異なるしきい値電圧を示すデュアルゲート駆動のトランジスタを抵抗素子として用いることで、一系統の基準電位回路のみで安定したベリファイ動作、及び読み出し動作が可能となる。

(もっと読む)

不揮発性メモリー装置の製造方法

【課題】不揮発性メモリー装置の製造方法であって、特に半導体パターン厚さの均一性が向上される3次元半導体装置の製造方法、及び当該製造方法によって製造された3次元半導体装置を提供する。

【解決手段】この製造方法は、基板10の上に複数の第1の膜(鋳型膜)120及び複数の第2の膜(犠牲膜)が交互に積層された積層膜構造体を形成する段階、積層膜構造体を貫通する開口部、及び開口部周囲にアンダーカット領域を形成する段階、アンダーカット領域に局所的に配置される絶縁スペーサー155を形成する段階、絶縁スペーサー155が形成された開口部内に半導体パターン165を形成する段階を含む。

(もっと読む)

半導体装置

【課題】小型化が可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】基板901上に画素と不揮発性メモリとを備え、不揮発性メモリは、基板901上に形成される半導体活性層と、半導体活性層上に形成される絶縁膜923と、絶縁膜923上に形成されるフローティングゲイト電極907と、フローティングゲイト電極907を酸化して得られる酸化膜908,915,922と、酸化膜908,915,922に接して形成されるコントロールゲイト電極929と、を備え、画素と不揮発性メモリとは、基板901上に一体形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去電圧を低減させることができる半導体記憶装置を提供することを課題とする。

【解決手段】チャネル形成領域を有する半導体膜と、半導体膜のチャネル形成領域上に、第1の絶縁層、浮遊ゲート電極、第2の絶縁層、制御ゲート電極を設ける。浮遊ゲート電極材料には、半導体基板よりも仕事関数があまり大きくならない窒化チタンとすることにより、消去電圧低減を図ったものである。なお、上記窒化チタンのチタン組成比は、低消費電力化及び誤書き換え耐性の観点から56atomic%以上75atomic%以下がよい。

(もっと読む)

半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな駆動方法を提供する。また、新たな駆動方法により、メモリ素子への書き込み電位のばらつきを低減し、信頼性を向上させる。

【解決手段】半導体装置の駆動方法において、書き込み電位を段階的に上昇させて、同時に読み出し電流を確認し、読み出し電流の結果を書き込み電位に利用して書き込みを行う。つまり、正しい電位で書き込みが行われたか確認しながら書き込みを行うことで、信頼性の高い書き込みを行うことが可能である。

(もっと読む)

電界効果トランジスタおよび半導体装置の作製方法

【課題】導体半導体接合を用いた電界効果トランジスタのゼロ電流を低減せしめる構造を提供する。

【解決手段】半導体層101とゲート105の間に、絶縁物104により周囲を覆われた導体もしくは半導体よりなり、半導体層101を横切るように形成されたフローティング電極102を形成し、これを帯電させることにより、ソース電極103aやドレイン電極103bからのキャリアの流入を防止する。このため半導体層101中のキャリア濃度を十分に低く維持でき、よって、ゼロ電流を低減できる。

(もっと読む)

半導体記憶装置

【課題】 本発明の実施形態によれば、プロセッサの処理速度を低下させることなく、フラッシュメモリの信頼性を維持する半導体記憶装置を提供することができる。

【解決手段】 第1の電極に第1の電位を与え、全てのバックゲート電極に第1の電位よりも低い第2の電位を与え、第1乃至第n−1のフロントゲート電極に第1の電位よりも高い第3の電位を与え、第n以上のフロントゲート電極に第2の電位と第3の電位との間の第4の電位を与えることで半導体層に情報を書き込むことを特徴とする

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】不揮発性半導体記憶装置の高集積化と高歩留りを実現する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、複数のメモリストリングを有する第1乃至第4のフィン型積層構造9−1,9−2,9−3,9−4と、第1及び第2のフィン型積層構造9−1,9−2の第2の方向の一端を互いに接続する第1の部分P1と、第3及び第4のフィン型積層構造9−3,9−4の第2の方向の一端を互いに接続する第2の部分P2と、第1及び第3のフィン型積層構造9−1,9−3の第2の方向の他端を互いに接続する第3の部分P3と、第2及び第4のフィン型積層構造9−2,9−4の第2の方向の他端を互いに接続する第4の部分P4とを備える。第1及び第2の部分P1,P2は、ソース領域であり、第3及び第4の部分P3,P4は、ドレイン領域である。

(もっと読む)

記憶装置、半導体装置

【課題】長い期間においてデータの保持が可能な記憶装置を提供する。

【解決手段】記憶素子と、上記記憶素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタとを有する。上記トランジスタは、通常のゲート電極の他に、閾値電圧を制御するための第2のゲート電極が備えられており、また、活性層に酸化物半導体を含むためにオフ電流が極めて低い。上記記憶装置では、絶縁膜に囲まれたフローティングゲートに高電圧で電荷を注入するのではなく、オフ電流の極めて低いトランジスタを介して記憶素子の電荷量を制御することで、データの記憶を行う。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜の形成を1000℃以上で行う場合に、Grow−in欠陥の発生の抑制と、BMDを用いたゲッタリング効果の向上を両立させる。

【解決手段】初期状態での酸素濃度が5×1017atoms/cm3以下の半導体基板に素子分離領域3を形成し、ゲート絶縁膜5aを1000℃以上の熱酸化により形成した後、酸素をイオン注入して熱処理することで、BMD層30を素子分離領域3の底面よりも下方に形成する。

(もっと読む)

半導体記憶装置

【課題】動作速度が高い半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、それぞれ複数の絶縁膜及び電極膜が交互に積層され、前記絶縁膜及び前記電極膜の積層方向に延びる貫通ホールが形成された積層体と、前記貫通ホールの内面上に設けられたブロック層と、前記ブロック層に囲まれた電荷蓄積層と、前記電荷蓄積層に囲まれたトンネル層と、前記トンネル層に囲まれた半導体ピラーと、を備える。そして、前記トンネル層における前記半導体ピラー側の部分の誘電率は、前記トンネル層における前記電荷蓄積層側の部分の誘電率よりも高い。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】不揮発性半導体記憶装置の高信頼性及び高集積化を図る。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1乃至第iのメモリストリング(iは、2以上の自然数)を有し、第2の方向に延び、第3の方向に隣接する第1及び第2のフィン型積層構造9−1,9−2と、第1のフィン型積層構造9−1の第2の方向の一端に接続され、第3の方向の幅が第1のフィン型積層構造9−1のそれよりも広い第1の部分7aと、第2のフィン型積層構造9−2の第2の方向の一端に接続され、第3の方向の幅が第2のフィン型積層構造9−2のそれよりも広い第2の部分7bとを備える。第1乃至第iのメモリストリングは、それぞれ、複数のメモリセルとアシストゲートトランジスタとを備える。アシストゲートトランジスタのアシストゲート電極AG1,AG2は、電気的に独立である。

(もっと読む)

半導体装置

【課題】メモリセルの保持データが多値化された場合であっても正確なデータを保持することが可能なメモリセルを有する半導体装置を供給すること。

【解決手段】半導体装置に、酸化物半導体によってチャネル領域が形成されるトランジスタのソース及びドレインの一方が電気的に接続されたノードにおいてデータの保持を行うメモリセルを設ける。なお、当該トランジスタのオフ電流(リーク電流)の値は、極めて低い。そのため、当該ノードの電位を所望の値に設定後、当該トランジスタをオフ状態とすることで当該電位を一定又はほぼ一定に維持することが可能である。これにより、当該メモリセルにおいて、正確なデータの保持が可能となる。

(もっと読む)

半導体装置及びその製造方法、並びに吸着サイト・ブロッキング原子層堆積法

【課題】キャパシタの誘電体膜において、リーク特性改善のためのAlドープ層を設けても、誘電体膜がAlドープ層で分断されず、サイズ効果の影響を抑え、結晶性の良好な誘電体膜を提供する。

【解決手段】誘電体膜中に少なくとも1層のAlドープ層を有し、Alドープ層の1層におけるAl原子の面密度を1.4E+14[atoms/cm2]未満とする。また、その面密度を達成するため、通常のALDによる誘電体膜成膜と、Alソースの吸着サイトを制限するブロッカー分子の吸着を行った後、Alソースを吸着させ、反応ガスを導入して反応させる吸着サイト・ブロッキングALD法によるAl添加の組み合わせを採用する。

(もっと読む)

半導体装置の製造方法

【課題】容量コンタクトパッドと容量コンタクトプラグが一体となった構造を形成する。これにより、従来は2回、必要だったフォトリソグラフィ工程を1回に削減して、製造コストを低減する。

【解決手段】半導体装置の製造方法では、層間絶縁膜上に、開口を有するマスクパターンを形成する。このマスクパターンを用いて、層間絶縁膜をエッチングすることにより、開口の下の層間絶縁膜内に容量コンタクトホールを形成する。湿式エッチングにより、マスクパターン内の開口を大きくした後、開口内に導電材料を埋め込むことにより、それぞれ容量コンタクトプラグ及び容量コンタクトパッドを形成する。この後、容量コンタクトパッド上にキャパシタを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGとp型ウエルPW1との間および制御ゲート電極CGとメモリゲート電極MGとの間には、絶縁膜5が形成されている。この絶縁膜5のうち、メモリゲート電極MGの下面と半導体基板1の上面との間の部分は、酸化シリコン膜9a,9bと酸化シリコン膜9a,9bに挟まれた窒化シリコン膜10aとを有している。絶縁膜5のうち、制御ゲート電極CGの側面とメモリゲート電極MGの側面との間の部分は、酸化シリコン膜6aからなり、窒化シリコン膜10aを有していない。

(もっと読む)

341 - 360 / 1,709

[ Back to top ]