Fターム[5F083JA02]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104)

Fターム[5F083JA02]の下位に属するFターム

酸化膜を含む複合膜 (2,564)

酸化窒化膜 (1,013)

タンタル酸化膜(Ta2O5) (705)

ハロゲンを含む酸化膜 (7)

複酸化物 (3,106)

Fターム[5F083JA02]に分類される特許

401 - 420 / 1,709

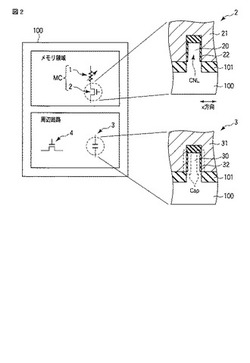

抵抗変化メモリ

【課題】大きい静電容量のキャパシタを含む抵抗変化メモリを提供する。

【解決手段】本実施形態の抵抗変化メモリは、アクティブ領域としての半導体領域20と、ゲート絶縁膜22を介して半導体領域21の側面に対向するゲート電極21とを有する選択トランジスタと、記憶するデータに応じて抵抗値が変化するメモリ素子1とを含むメモリセルMCと、第1のキャパシタ電極としての半導体領域30と、半導体領域30の側面に対向するキャパシタ電極31と、半導体領域20とキャパシタ電極31との間に設けられたキャパシタ絶縁膜32とを含むキャパシタ3と、を含む。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、チャネル形成領域を含む半導体層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、ゲート絶縁層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

垂直的に集積された不揮発性記憶セルサブストリングを含む不揮発性記憶装置の形成方法、及び形成された不揮発性記憶装置

【課題】 セルの電気的特性の均一性を向上させ得る3次元不揮発性記憶装置及びその形成方法を提供する。

【解決手段】 本発明の不揮発性記憶装置の形成方法は不揮発性記憶セルが高集積化された垂直的積層を形成するための段階を含む。不揮発性記憶セルでは、直列に電気的に連結される複数の垂直サブストリングを使用して記憶セルが半導体基板上に垂直に積層される。このとき、記憶セルの垂直方向の積層は劣等に作用するメモリセルストリングが発生しないように、製造工程において補正するためにダミー記憶セルを利用する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第1のトランジスタのゲート電極と、該ゲート電極に接する第2のトランジスタのソース電極とは、エッチングの選択比がとれる材料を用いて形成される半導体装置を提供する。第1のトランジスタのゲート電極と、第2のトランジスタのソース電極とをエッチングの選択比がとれる材料を用いて形成することで、レイアウトのマージンを低減させることができるため半導体装置の集積度を向上させることができる。

(もっと読む)

半導体不揮発性記憶素子及びその製造方法

【課題】MFMIS構造の半導体不揮発性記憶装置において、メモリセル面積を大きくすることなく、効率的に強誘電体キャパシタに分配電圧を加えることができる半導体不揮発性記憶装置及びその製造方法を提供する。

【解決手段】強誘電体不揮発性記憶素子において、チャンネル領域上に第1絶縁体層(3)、第1導電体層(4)、強誘電体層(5)、及び第2導電体層(6)が順次積層された構造を持ち、ソース領域とドレイン領域上にそれぞれ積層された第3導電体(9)と第4導電体(10)を持ち、第3導電体(9)及び第4導電体(10)が、第1導電体層(4)と第2絶縁体薄膜(11)を介して対向する構造を持つ。

(もっと読む)

パルス変換回路

【課題】回路面積を低減する。

【解決手段】第1の信号が入力され、第2の信号を出力する論理回路を具備し、論理回路は、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧に設定するか否かを制御するP型トランジスタと、エンハンスメント型であり、閾値電圧の絶対値がP型トランジスタより大きく、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧より高い第2の電圧に設定するか否かを制御するN型トランジスタと、を備え、P型トランジスタは、チャネルが形成され、第14族の元素を含有する半導体層を含み、N型トランジスタは、チャネルが形成され、キャリア濃度が1×1014/cm3未満である酸化物半導体層を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化を行った場合であっても、下部電極の倒壊を防止して静電容量の大きいキャパシタ素子を容易に形成する。

【解決手段】半導体装置は、下部電極、容量絶縁膜、及び上部電極を有するキャパシタを複数、備える。各キャパシタの下部電極は、底部及び筒状の側壁部を有する。各下部電極の側壁部における底部側の端部の外壁側面上には、第1の支持部が設けられている。また、各下部電極の側壁部の第1の支持部で覆われていない外壁側面の少なくとも一部に接するように第2の支持部が設けられている。

(もっと読む)

記憶装置、半導体装置

【課題】データを保持する期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置の提案を目的の一とする。

【解決手段】記憶素子と、記憶素子における電荷の蓄積、保持、放出を制御するための、酸化物半導体を活性層に含むトランジスタと、記憶素子に接続された容量素子とを有する記憶装置。上記容量素子が有する一対の電極の少なくとも一方は、遮光性を有している。さらに、上記記憶装置は遮光性を有する導電膜或いは絶縁膜を有しており、上記活性層が、遮光性を有する電極と、遮光性を有する導電膜或いは絶縁膜との間に位置する。

(もっと読む)

強誘電体薄膜及び該強誘電体薄膜を用いた薄膜キャパシタ

【課題】寿命信頼性を向上し得る、強誘電体薄膜及び該強誘電体薄膜を用いた薄膜キャパシタを提供する。

【解決手段】(PbxLay)(ZrzTi(1-z))O3(式中、0.9<x<1.3、0≦y<0.1、0≦z<0.9)で示される複合金属酸化物に、Bi、Si、Pb、Ge、Sn、Al、Ga、In、Mg、Ca、Sr、Ba、V、Nb、Ta、Sc、Y、Ti、Zr、Hf、Cr、Mn、Fe、Co、Ni、Zn、Cd、Li、Na、K、P、B、Ce、Nd、Sm及びCsからなる群より選ばれた1種或いは2種以上の元素から構成される金属酸化物がある一定の割合で混合した混合複合金属酸化物の形態をとる強誘電体薄膜が、2〜23層の焼成層を積層して構成され、焼成層の厚さtが45〜500nmであり、焼成層中に存在する結晶粒の定方向最大径の平均xが200〜5000nmであり、焼成層のいずれにおいても1.5t<x<23tの関係を満たす。

(もっと読む)

半導体装置の製造方法

【課題】ボーイング形状に形成される深孔をストレート形状にする。

【解決手段】シリコン窒化膜4上に、不純物ドープした第1のシリコン酸化膜5と、不純物非ドープの第2のシリコン酸化膜6の積層構造の層間絶縁膜に、ドライエッチングによりボーイング形状の第1のホール8を形成し、熱リン酸を用いたウエットエッチングによりシリコン窒化膜4と第1のシリコン酸化膜5とを後退させてボーイング部の下部を拡幅した第2のホール9を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】歩留まりに優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、基板内の記憶回路領域に形成されており、多層配線層内に埋め込まれた少なくとも1以上の容量素子および周辺回路を有する記憶回路と、平面視において、基板内の憶回路領域とは異なる領域である論理回路領域に形成された論理回路と、を備え、容量素子は、下部電極、容量絶縁膜、上部電極、埋設電極および、上部接続配線で構成されており、上部接続配線と埋設電極とは、同一の材料かつ一体に構成されており、上部接続配線と下部電極との間には、論理回路を構成する前記配線が少なくとも1以上設けられており、上部接続配線の上面と、上部接続配線と同じ配線層に形成された論理回路を構成する配線の上面とが、同一面を構成する。

(もっと読む)

半導体装置の駆動方法

【課題】酸化物半導体層によってチャネル領域が形成されるトランジスタのソース及びドレインの一方に電気的に接続されたノードにおいて電荷の保持を行う半導体装置に記憶された情報の経時変化を抑制すること。

【解決手段】書き込み期間と保持期間の間に、トランジスタのゲートに強い負電位を与える期間(反転期間)を設ける。反転期間において、当該トランジスタのドレインから酸化物半導体層に対する正電荷の供給が促進される。これにより、酸化物半導体層内又は酸化物半導体層及びゲート絶縁膜の界面への正電荷の蓄積を短期間で収束させることができる。そのため、反転期間後の保持期間における当該トランジスタのドレインに電気的に接続されたノードにおける正電荷の減少を抑制することが可能である。すなわち、当該半導体装置に記憶された情報の経時変化を抑制することが可能である。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】専有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】バックゲート電極を有する読み出し用トランジスタと、書き込み用トランジスタと、を有する多値型メモリセルを用いる。情報の書き込みは、書き込み用トランジスタをオン状態とすることにより、書き込み用トランジスタのソース電極またはドレイン電極の一方と、読み出し用トランジスタのゲート電極が電気的に接続されたノードに、情報に応じた電位を供給し、その後、書き込み用トランジスタをオフ状態とすることにより、ノードに所定の電位を保持させる。情報の読み出しは、読み出し用トランジスタのソース電極またはドレイン電極の一方と接続された制御信号線に、読み出し制御電位を供給し、その後、読み出し信号線の電位変化を検出することで行う。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】オフ電流を低減し、特性ばらつきが抑制された多結晶半導体層をチャネル領域とする半導体装置の製造方法を提供する。

【解決手段】半導体基板の上に絶縁体層を形成する工程と、絶縁体層上に狭窄部を有する非晶質または多結晶質の半導体層を形成する工程と、半導体層上に半導体層よりも熱膨張係数の大きい絶縁体層を形成する工程と、熱処理を行う工程と、絶縁体層を除去する工程と、狭窄部の側面にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、半導体層中にソース・ドレイン領域を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の平面形状を大きくせずに、その容量を大きくすることができ、かつ容量素子のリーク電流が増大することを抑制する。

【解決手段】下部電極410は、表層に、厚さが2nm以下の金属含有酸化層414を有している。金属含有酸化層414は、下部電極410の表面を酸化することにより形成されている。そして誘電膜420は、バルク状態において常温で出現する第1相と、バルク状態において第1相より高温で出現する第2相と、を含んでいる。第2相は第1相より比誘電率が高い。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の長時間にわたる保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと、第2のトランジスタと、を含む複数のメモリセルと、増幅回路と、スイッチ素子と、を含む読み出し回路と、リフレッシュ制御回路と、を有し、第1のチャネル形成領域と第2のチャネル形成領域は、異なる材料を主成分として構成され、第1のゲート電極と、第2のソース電極および第2のドレイン電極の一方は電気的に接続され、第2のソース電極および第2のドレイン電極の他方と、増幅回路の入力端子の一は電気的に接続され、増幅回路の出力端子は、スイッチ素子を介して第2のソース電極および第2のドレイン電極の他方と接続され、スイッチ素子の導通状態または非導通状態は、リフレッシュ制御回路によって制御される半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】ゲート電極を形成し、ゲート電極上に第1の絶縁膜を形成し、第1の絶縁膜にハロゲンドープ処理を行って、第1の絶縁膜にハロゲン原子を供給し、第1の絶縁膜上に、ゲート電極と重畳して酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供給し、酸素原子が供給された酸化物半導体膜に熱処理を行い、酸化物半導体膜上に接して、ソース電極およびドレイン電極を形成し、第2の絶縁膜を形成する半導体装置の作製方法である。

(もっと読む)

不揮発性記憶素子

【課題】本発明は、中間絶縁膜、半導体層、及びトンネル絶縁膜のうちの少なくとも1つが酸化ガリウムを含まない場合に比べて、動作安定性の向上した不揮発性記憶素子を提供する。

【解決手段】不揮発性記憶素子10は、基板30上と、ソース電極34S及びドレイン電極34Dと、半導体層36と、トンネル絶縁膜38と、電荷蓄積層40と、中間絶縁膜42と、ゲート電極44Gと、を備えており、半導体層36、トンネル絶縁膜38、及び中間絶縁膜42が、酸化ガリウムを含んでいる。

(もっと読む)

401 - 420 / 1,709

[ Back to top ]