Fターム[5F083JA40]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | 金属窒化物 (3,610)

Fターム[5F083JA40]に分類される特許

201 - 220 / 3,610

半導体装置の作製方法

【課題】信頼性の高い半導体装置及び、信頼性の高い半導体装置の作製方法を提供する。また、消費電力が低い半導体装置及び消費電力が低い半導体装置の作製方法を提供する。また、量産性の高い半導体装置及び量産性の高い半導体装置の作製方法を提供する。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

記憶素子およびその製造方法ならびに記憶装置

【課題】低電流動作に優れると共に良好な保持特性を有する記憶素子および記憶装置を提供する。

【解決手段】本開示の記憶素子は、第1電極、記憶層および第2電極をこの順に有し、記憶層は、酸化物を含むと共に、第1電極側に設けられた抵抗変化層と、テルル(Te),硫黄(S)およびセレン(Se)のうちの少なくとも1種のカルコゲン元素および記憶層内の移動が容易な移動容易元素を含み、第1電極から第2電極に向かって移動容易元素の濃度分布を有する第1層と、記憶層内を移動しにくい移動困難元素を含む第2層とからなる単位イオン源層が少なくとも2層積層され、第2電極側に設けられたイオン源層とを備える。

(もっと読む)

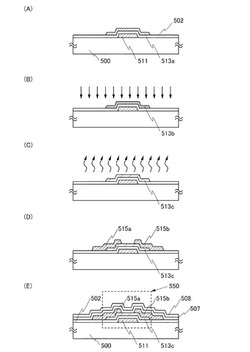

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】PRAMの高集積化を行うこと。

【解決手段】第1層間絶縁膜のホールの内壁面を覆うサイドウォール絶縁膜と、ホール内においてサイドウォール絶縁膜を介して埋め込まれたコンタクトプラグと、第1層間絶縁膜上の所定の領域にてコンタクトプラグに接続されるように配された下部電極と、下部電極を含む前記第1層間絶縁膜上を覆う第2層間絶縁膜と、第2層間絶縁膜を貫通し、下部電極の側端面の一部が表れ、かつ、第1層間絶縁膜の所定深さまで形成された開口部と、開口部を含む前記第2層間絶縁膜上の所定の領域に配されるとともに、前記開口部にて前記下部電極の側端面の一部と接続された相変化材料層と、相変化材料層上に配された上部電極と、を備える。

(もっと読む)

半導体装置

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提

供を目的の一つとする。

【解決手段】記憶素子として機能するトランジスタに蓄積された電荷を保持するためのス

イッチング素子として、酸化物半導体膜を活性層として用いたトランジスタを、記憶装置

の各メモリセルに設ける。また、記憶素子として用いるトランジスタは、第1のゲート電

極と、第2のゲート電極と、第1のゲート電極と第2のゲート電極の間に位置する半導体

膜と、第1のゲート電極と半導体膜の間に位置する第1の絶縁膜と、第2のゲート電極と

半導体膜の間に位置する第2の絶縁膜と、半導体膜に接するソース電極及びドレイン電極

と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】容量絶縁膜の絶縁性の劣化が生じにくく、かつ容量プレート電極の厚みが薄い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、互いに異なる平面面積を持つメモリセル部と補償容量部とを単一の基板上に備える。メモリセル部と補償容量部とは、同一構成の容量プレート電極を含む。容量プレート電極は、ボロンドープシリコンゲルマニウム膜と金属膜とを含む積層構造を有している。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】抵抗変化メモリの製造プロセスにおけるPEP数を削減する。

【解決手段】実施形態に係わる抵抗変化メモリは、第1の方向及びこれに直交する第2の方向にそれぞれ交互に配置される複数の抵抗変化素子MTJ及び複数のビアV0と、複数の抵抗変化素子MTJの側壁上に配置される複数の側壁絶縁層PLとを備える。複数の抵抗変化素子MTJは、一定ピッチで格子状に配置され、複数の側壁絶縁層PLの側壁に垂直な方向の厚さは、複数の側壁絶縁層PLが互いに部分的に接触し、複数の側壁絶縁層PL間に複数のホールが形成される値に設定される。複数のビアV0は、これら複数のホール内に配置される。

(もっと読む)

半導体装置

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体メモリ装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に、書き込みトランジスタのソースおよび読み出しトランジスタのソースをビット線に、読み出しトランジスタのドレインを読み出しワード線に接続する。ここで、書き込みトランジスタと読み出しトランジスタの導電型を異なるものとする。集積度を高めるために、バイアス線を他行の読み出しワード線で代用したり、記憶セルを直列に接続し、NAND構造とし、読み出しワード線と書き込みワード線を共用してもよい。

(もっと読む)

半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供する

ことを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウ

ム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて

、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化

物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以

下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有

し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でス

パッタリングを行う。

(もっと読む)

エッチング方法及びこれに用いられるシリコンエッチング液

【課題】少なくとも無機アルカリ化合物、ヒドロキシルアミン化合物、及びアニオン性化合物を含むシリコンエッチング液を、多結晶シリコン膜またはアモルファスシリコン膜に適用して、該膜の少なくとも一部を除去するエッチング方法。

【解決手段】アモルファスシリコン又は多結晶シリコン膜を的確かつ効率よく除去して半導体基板に凹凸を形成するに当たり、ウエハの中央部から端部に至るまでバランスよくエッチングするシリコンエッチング液及びこれを用いたエッチング方法を提供する。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置および半導体装置の制御方法

【課題】信頼性を確保しつつ、高速動作を実現することができる半導体装置を提供する。

【解決手段】抵抗変化素子10を有するメモリセル11と、メモリセル11に印加する電圧を制御する制御部80と、を備え、抵抗変化素子10は、第1の金属材料を含有する下部電極14と、第2の金属材料を含有する上部電極16と、酸素を含有する絶縁膜12と、を有しており、第1の金属材料は、第2の金属材料よりも規格化酸化物生成エネルギーが大きく、制御部80は、絶縁膜12の抵抗値を高抵抗化させる動作時および低抵抗化させる動作時において上部電極16に正電圧を印加し、絶縁膜12の抵抗値を読み出す動作時において下部電極14に正電圧を印加する。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

相変化メモリデバイスの研磨用化学機械研磨用スラリー組成物およびそれを使った相変化メモリデバイスの研磨方法

【課題】高速で相変化メモリデバイスを研磨することができる、相変化メモリデバイスの化学機械研磨(CMP)用スラリー組成物、及びそれを用いた研磨方法を提供する。

【解決手段】脱イオン水および窒素化合物を含む、相変化メモリデバイスの化学機械研磨(CMP)用スラリー組成物を用いる。窒素化合物は、脂肪族アミン、芳香族アミン、アンモニウム塩、アンモニウム塩基またはこれらの組み合わせから選択される少なくとも1種の化合物を含む。

(もっと読む)

半導体装置

【課題】FETの駆動力性能や遮断性能などを向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備える。前記半導体素子は、前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、前記絶縁膜の上方に配置されるゲート電極と、前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜に酸素ドープ処理を行って、第1の絶

縁膜に酸素原子を供給し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに

、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半

導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された

酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳す

る領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の占有面積を実質的に減少させる。

【解決手段】半導体装置は、第1の方向及びそれと交差する第2の方向に沿って半導体基板上に配列形成された複数の第1の接続領域と、複数の第1の接続領域を第1の方向に沿った列ごとに電気的に接続する複数の配線とを含む。複数の配線は、第2の方向に隣り合う2つの配線が互いに異なる配線層に配置され、かつ平面視において一部が重なってハニカム状に見えるように屈曲させてある。

(もっと読む)

GeリッチなGST−212相変化材料

【課題】本発明の主な目的は、GeリッチなGST−212相変化材料を提供することにより、従来のGST−225の相変化メモリよりも高い結晶化温度、低いリセット電流要件及び優れた保持率を有することができる。

【解決手段】相変化材料は、Ge原子濃度xは、30%〜65%の範囲内にあり、Sb原子濃度yは、13%〜27%の範囲内にあり、Te原子濃度zは、20%〜45%の範囲内にある。このような材料のGeリッチな族も記載されている。そのような材料を含む集積回路に適したメモリデバイスは記載されている。

(もっと読む)

相変化素子及びその製造方法

【課題】相変化記録材料膜/上部電極層界面の接触抵抗の増大とばらつきを抑制することができる相変化素子を提供する。

【解決手段】導電性プラグ(13)と、相変化記録材料膜(20)と上部電極層(15)とを含む相変化素子であって、該導電性プラグ(13)と該相変化記録材料膜(20)とが縦方向に接続されるとともに、該相変化記録材料膜(20)と該上部電極層(15)とが、該相変化記録材料膜(20)の側面の少なくとも一部で接続されている相変化素子。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

201 - 220 / 3,610

[ Back to top ]