Fターム[5F083JA40]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | 金属窒化物 (3,610)

Fターム[5F083JA40]に分類される特許

3,601 - 3,610 / 3,610

酸化物薄膜製造方法及びその製造装置

酸化物薄膜の酸素欠損の低下とエピタキシャル成長との促進を図ることにより、優れた特性を有する酸化物薄膜を製造する薄膜製造方法であって、原料ガス、キャリアガス及び酸化ガスを混合して得た混合ガスを、加熱手段により原料の液化、析出、成膜が起こらない温度に維持されたガス活性化手段を通してシャワープレートから反応室内の加熱基板上に供給して反応させ、基板上に酸化物薄膜を製造する。その際、酸化ガスの割合を混合ガス基準で60%以上とする。また、核形成による初期層を形成する場合、その成膜プロセスにおける酸化ガス流量割合を60%未満とし、その後の成膜プロセスにおける酸化ガス流量割合を60%以上として行う。また、酸化物薄膜製造装置において、混合器とシャワープレートとの間に加熱手段を備えてなる。 (もっと読む)

メモリ用相変化アクセス装置

メモリは、カルコゲナイド材料を用いて形成されたアクセス装置を有する。アクセス装置は、アクセスされた対応メモリ素子の読み出しを妨害するスナップバック電圧を生じない。相変化メモリ素子の場合、スナップバック電圧は、層変化メモリ素子の閾値電圧よりも小さい。  (もっと読む)

(もっと読む)

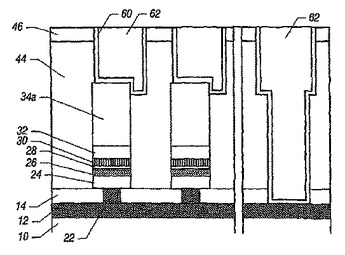

下地メモリ素子と接触するダマシン導線

ダマシン法を用いて、相変化メモリ内の底部導線に接続される電極が形成される。層変化メモリは、複数の分離されたメモリセルで構成されても良く、各メモリセルは、相変化メモリ閾値スイッチと、相変化メモリ記憶素子とを有する。  (もっと読む)

(もっと読む)

FETベースの磁気ランダム・アクセス・メモリ・デバイス用の自己整列型導電線およびこれを形成する方法

【課題】下部メタライズ線(302)に導電的に結合された横方向の金属ストラップ(326)を含む、電界効果トランジスタ(FET)ベースの磁気ランダム・アクセス・メモリ(MRAM)デバイス用の導電線構造を提供すること。

【解決手段】金属ストラップ(326)上に磁気トンネル接合(MTJ)スタック(316)が形成され、MTJスタック(316)を覆って金属シールド(324)が形成され、金属シールド(324)は金属ストラップ(326)に対して自己整列される。上部メタライズ線(332)は金属シールド(324)に導電的に結合され、金属シールド(324)は上部メタライズ線(332)の形成時にエッチ・ストップとして働く。

(もっと読む)

ビア開口部中に形成されるポリマーメモリデバイス

本発明は、ビア内にポリマーメモリデバイスを製造する方法に関する。この方法は、少なくとも1つの金属を含む層をその上に備える半導体基板を提供するステップと、この金属を含む層中に少なくとも1つの銅コンタクトを形成するステップと、銅コンタクト上に少なくとも1つの絶縁層を形成するステップと、絶縁層に少なくとも1つのビアを形成し、銅コンタクトの少なくとも一部を露出するステップと、ビアの下側部分にポリマー材料を形成するステップと、ビアの上側部分にトップ電極材料層を形成するステップとを含む。  (もっと読む)

(もっと読む)

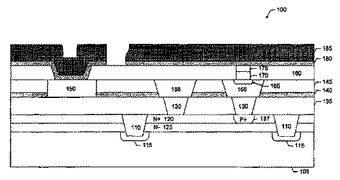

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

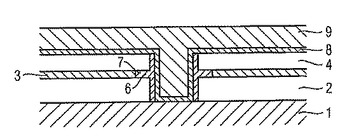

デバイス内にバリア層を有するコンタクトホールを形成する方法及び得られるデバイス

デバイスの下層(2)にコンタクトを形成する方法は、コンタクトホール(5)を形成するステップと、デバイスのコンタクトホール内にバリア材からなるコンタクトホールバリア層(7)を形成するステップと、コンタクトホールの底面のコンタクトホールバリア層をエッチングするステップと、コンタクトホール内にライナ材(8)を堆積するステップと、コンタクトホールに導電性材料(9)を充填するステップとを有する。半導体、受動素子、キャパシタ又はFeRAMなどのデバイスが上記方法に従って形成される。コンタクトホールの側壁にあるコンタクトホールバリア層(7)が、水素及び/又は酸素の側方拡散を抑制する。コンタクトホールバリア層は、ウェットエッチングプロセスによって生じる既存のバリア層(3)内のボイド(6)を充填するために上記プロセス後に、又は既存のバリア層への損傷を抑制するために上記プロセス前に行うことができる。

(もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜の埋め込み性が高く高集積化に適切に対応することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の上方に強誘電体キャパシタを形成した後、強誘電体キャパシタを覆うAl2O3膜を形成する。その後、Al2O3膜を覆う高密度プラズマ絶縁膜を、O2ガス及びSiH4ガスを用いて形成する。このとき、O2ガスの流量をSiH4ガスの流量の6乃至9倍とすると共に、半導体基板の温度を280℃乃至320℃とする。

(もっと読む)

半導体装置の製造装置および製造方法

【課題】 加水分解性の液体材料が大気と接触するのを確実に防止できる液体自動供給システムを提供する。

【解決手段】 このCVD装置50は、処理室51にペンタエトキシタンタル(PET)を供給するための容器53に予備容器73を接続し、容器53内のペンタエトキシタンタル(PET)の残量が少なくなったときは、配管54と容器53とを切り離して新しい容器53と交換するのではなく、予備容器73からペンタエトキシタンタル(PET)を補充する。これにより、配管54と容器53とを切り離すためのジョイント61jを通じて配管54内に大気が侵入し、配管54内の残留ペンタエトキシタンタル(PET)が加水分解されて酸化タンタルが生成することはない。

(もっと読む)

半導体装置およびその製造方法

【課題】 強誘電体キャパシタに保護膜を設け、強誘電体膜の還元を抑制する。

【解決手段】 前記保護膜としてAl2 O3 膜を、3.0〜3.1g/cm3 、あるいはそれ以上の密度に形成する。

(もっと読む)

3,601 - 3,610 / 3,610

[ Back to top ]