Fターム[5F083JA53]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | ポリサイド構造、サリサイド構造 (1,816)

Fターム[5F083JA53]に分類される特許

1,801 - 1,816 / 1,816

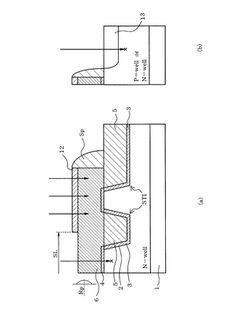

半導体装置の製造方法

【課題】 SRAMセルのサイズが縮小化された場合、ゲート電極配線の抵抗要素の抵抗値を調整してSRAMセルを形成できるようにする。

【解決手段】 SRAMセルの製造時において、1回目に不純物イオンを注入するときにはイオン濃度を比較的高く低加速電圧の条件でイオン注入し、ソース/ドレイン拡散層13を形成する。2回目に不純物イオンを注入するときには、イオン濃度を比較的低く高加速電圧の条件でイオン注入し、第1の多結晶シリコン膜6の抵抗値を調整する。

(もっと読む)

半導体記憶装置

【課題】 1交点方式(オープンビット線型)のダイナミック型RAMにおいて、隣接するビット線間に生じる干渉ノイズを有効に減少させる。

【解決手段】 センスアンプ列7を中心に左右にサブアレイ8、8が配置される。この各サブアレイは多数のダイナミック型メモリセルMC…を有する。センスアンプ列7の左方及び右方に位置するサブアレイ8、8において、同一行のビット線同士(BL0、NBL0)〜(BLn、NBLn)により相補のビット線対が構成されていて、オープンビット線型となっている。各サブアレイ8、8において、各ビット線BL0〜BLn、NBL0〜NBLn間には、各々、これらのビット線と平行に且つ同一配線層に形成された第1の配線パターンSLDが配置される。これらの配線パターンSLDは全て電源電位などの固定電位に設定される。

(もっと読む)

半導体装置の製造方法

【課題】 セルトランジスタの拡散層に接続された多結晶シリコン電極と、周辺回路トランジスタの拡散層に接続された金属電極とを備え、多結晶シリコン電極が形成された拡散層の接合リーク電流が抑制され、これによって、良好な情報保持特性を有する半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、多結晶シリコン電極に接続された拡散層を有するトランジスタを形成する工程と、980〜1020℃の基板温度で熱処理する第1の高温熱処理工程(工程A2)と、700〜850℃の基板温度で熱処理する第1の低温熱処理工程(工程A3)とをこの順に有する。

(もっと読む)

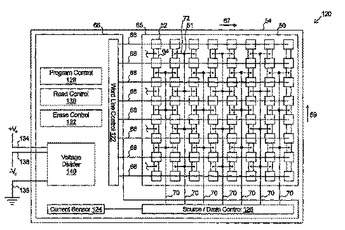

ビットライン短絡のないメモリ装置用ハードマスクプロセス

MirrorBit(トレードマーク)フラッシュメモリの製造方法は、半導体基板(102)を準備し(602)、電荷トラップ誘電体層(504)を堆積する(606)。第1及び第2のビットライン(512)が埋め込まれ(608)、ワードライン層(515)が堆積される(610)。ハードマスク層(516)はワードライン層(515)の上に堆積される(612)。ハードマスク層(516)は、電荷トラップ誘電体層(504)を破損することなく除去するため調製された材料からなる。フォトレジスト(518)はワードライン層(515)の上に堆積され、ハードマスク(519)を形成するため使用される(618)。フォトレジスト(518)は除去される(620)。ワードライン層(515)はワードライン(525−528)を形成するためハードマスク(519)を使用して処理される。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】 複数のスタックゲート型メモリセルを含むフラッシュメモリにおいて、消去前書込動作を不要とすることにより一括消去動作に要する時間を短縮し、データの書換動作に要する時間も短縮することである。

【解決手段】 消去時に、複数のメモリセルのソース1003からフローティングゲート1005に同時に電子を注入する。それにより、複数のメモリセルのしきい値電圧が上昇する。プログラム時に、選択されたメモリセルのフローティングゲート1005からドレイン1002に電子を放出する。それにより、選択されたメモリセルのしきい値電圧が下降する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置、例えばSRAMのメモリセルのα線によるソフトエラーを低減する。

【解決手段】基板1aをエッチングして第1配線溝HM1を形成し、第1配線溝HM1下の素子分離2(または素子分離溝2および絶縁層1c)をエッチングして第2配線溝HM2を形成し、第1配線溝HM1および第2配線溝HM2の内壁に沿って局所配線16a,16bを形成し、一方の局所配線16aを下部電極ELとして、その下部電極EL上に容量絶縁膜となる窒化シリコン膜17、さらに上部電極EUを形成することにより、容量CA1の面積を増加させて、メモリセルの記憶ノードに相対的に大きな静電容量を付加する。

(もっと読む)

フラッシュメモリ装置のワード線を保護するための方法および装置

製造中に、プロセスに関連する帯電からフラッシュメモリのワード線(WL)およびメモリセル(101)を保護するための方法と構造とが与えられる。ドープされたポリシリコンのワード線(110a)の端部にドープされていないポリシリコン(110b)が形成され、抵抗(110b)が生成される。これを通じて、プロセスにより生じる電荷が、基板(102)に結合された、ドープされたポリシリコン放電構造(110c)へ放電される。ワード線抵抗(110b)、および、放電構造(110c)は、単一のパターニングされたポリシリコン構造として形成される。ワード線(110a)および放電部分(110c)は導電性になるように選択的にドープされ、また、抵抗部分(110b)は、製造後に通常のセル動作が可能なほどに十分高い抵抗が与えられる一方で、製造中にプロセスに関連する電荷に対しては放電路を供給するように、実質的にドープされない。  (もっと読む)

(もっと読む)

半導体構成及び半導体構造の形成方法

本発明は、ケイ化物を含む埋込みビット線を有する半導体構造を含む。縦型SGT(サラウンド・ゲート・トランジスタ)構造がビット線の上に形成される。SGT構造は、DRAMデバイスなどのメモリ・デバイスに組み込むことができる。本発明は4F2DRAMデバイスの形成に利用することができる。  (もっと読む)

(もっと読む)

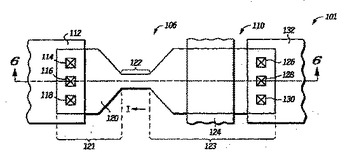

スタガー式ローカル接続構造を持つメモリセルアレイ

メモリセルアレイ(50)は、半導体基板(54)に製造された、2次元アレイのメモリセル(52)を含む。メモリセル(52)は、行方向(67)を形成する複数の行と、列方向(69)を形成する複数の列で並べられている。メモリセル(52)の各列は、複数の交互に配置されたチャネル領域(58)及びソース/ドレイン領域(64)を含む。各ソース/ドレイン領域(64)上には導電性インターコネクト(72)が配置されており、この導電性インターコネクト(72)はただ1つのその他のソース/ドレイン領域(64)に結合する。この1つのソース/ドレイン領域(64)とは、その列に隣接する第2の列に存在する領域である。導電性インターコネクト(64)は、1つおきの導電性インターコネクト(64)がその列の右側に隣接する列に接続するように、また、1つおきの導電性インターコネクトが、その列の左側に隣接する列に接続するように、配置される。複数のソース/ドレインコントロールライン(70)は、隣接するメモリセル(52)の列間に延在し、また、その隣接する列と列との間を結合する各導電性インターコネクト(72)に電気的に結合する。  (もっと読む)

(もっと読む)

2−トランジスタメモリセル及びその製造方法

本発明は、メモリゲートスタック(1)を有する記憶トランジスタ(1)及び選択トランジスタを有する2-トランジスタメモリセルを基板(50)上に製造する方法であって、トンネル誘電層(51)が前記基板(50)と前記メモリゲートスタック(1)との間にもたらされる方法を提供する。前記方法は、第一の導電層(52)及び第二の導電層(54)をもたらし、前記第二の導電層(54)をエッチし、それによってコントロールゲートを形成し、前記第一の導電層(52)をエッチし、それによってフローティングゲートを形成することによって前記メモリゲートスタック(1)を形成するステップを有する。前記方法は更に、前記第一の導電層(52)がエッチされる前に、前記トンネル誘電層(51)の下に形成されるべきチャネルの方向で前記コントロールゲートに対してスペーサ(81)を形成するステップと、その後、前記第一の導電層(52)をエッチするために前記スペーサ(81)をハードマスクとして使用し、それによって前記フローティングゲートを形成し、それによってフローティングゲートをコントロールゲートに自己整合させるステップとを有することを特徴とする。本発明は、前記コントロールゲート(54)は前記フローティングゲート(52)よりも小さくなり、スペーサ(81)が、前記コントロールゲート(54)に隣接してもたらされるメモリセルも提供する。  (もっと読む)

(もっと読む)

DRAMアクセス・トランジスタ及び形成方法

【構成】自己整列リセス・ゲート構造及び形成方法が開示されている。最初に,絶縁用のフィールド酸化物領域を半導体基板内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。 (もっと読む)

UVチャージングを減少するPECVDシリコンリッチ・シリコン酸化物層

メタライゼーションの前に、UV透過を低減するシリコンリッチ・シリコン酸化物層(500)をPECVDにより層間絶縁膜(300)上にたい積する。これによりVtが減少する。実施形態は、1.7から2.0のR.I.を有するUVを透過しないシリコンリッチ・シリコン酸化物層(500)をたい積するステップを含んでいる。  (もっと読む)

(もっと読む)

垂直方向の突起部を有するフローティングゲート構造

基板面から離れて延在する突起部を有するフローティングゲート構造を開示する。この突起部によって、フローティングゲートとコントロールゲートとを結合するための増加した表面積をフローティングゲートに提供することが可能となる。1つの実施形態では、フローティングゲートの個々の側面でワードラインが下方へ延在して、同じ列の隣接するフローティングゲートを遮蔽する。別の実施形態では、突起部を有するフローティングゲートの組立て製造処理工程を開示する。残りのフローティングゲートに対して自己位置合せを行うために突起部を形成してもよい。  (もっと読む)

(もっと読む)

フューズ及びその形成方法

アクティブフューズはアクティブフューズ構造(120)を備え、この構造を使用して可変抵抗体(106)及び選択トランジスタ(110)の双方を形成する。一の実施形態では、アクティブフューズ構造は、半導体基板(140)の活性領域(160)の一部に形成され、選択ゲート(124)はアクティブフューズ構造の一方の端部(123)の上に配置されてアクティブフューズへの書き込みに使用する一体型選択トランジスタ(110)を形成する。共有型のアクティブフューズ構造を活性領域の内部に使用することによって、面積要件を縮小し、かつ検出マージンを大きくすることができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 より優れたソフトエラー耐性を有するSOI基板を用いた高信頼性のCMOS・SRAMセルを備える半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 SOI基板の表面半導体層上にゲート絶縁膜を介して形成されたゲート電極と、該ゲート電極の両側の表面半導体層に形成された第1導電型ソース/ドレイン領域とから構成される半導体装置であって、前記第1導電型ソース/ドレイン領域の双方又は一方に接して第2導電型引出拡散層が形成され、少なくとも前記第1導電型ソース/ドレイン領域上から第2導電型引出拡散層上にわたってシリサイド層が形成されており、シリサイド層に接地電位が与えられてなる半導体装置。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ビット線とセルコンタクト部の容量接続用コンタクトとのショートを防止し、容量接続用コンタクトとビット線とのマージンを大きくすることができる半導体記憶装置及びその製造方法の提供。

【解決手段】STIにより活性領域が分離形成された半導体基板上の第1の層間絶縁膜4に活性領域まで貫通するコンタクト孔5を設け、その内部に第1の層間絶縁膜上面よりも低い位置まで多結晶シリコン6を充填した後、多結晶シリコン上部にシリサイド膜12を形成し、第1の層間絶縁膜上の所定領域にポリサイド膜又はメタル膜を含むビット線7とビット線の上面及び側面にシリコン窒化膜を形成した後、ビット線で覆われていないコンタクト孔内部のシリサイド膜を除去することにより、シリンダ型容量と接続されるコンタクト孔内部の導電体とそのコンタクト孔に隣接するビット線とを分離する。その後、第2の層間絶縁膜10を堆積し、シリサイド膜を除去したコンタクト孔まで貫通するシリンダ型容量パターンを形成する。

(もっと読む)

1,801 - 1,816 / 1,816

[ Back to top ]