Fターム[5F083JA55]の内容

Fターム[5F083JA55]の下位に属するFターム

Fターム[5F083JA55]に分類される特許

21 - 40 / 42

ガスクラスターイオンビームを用いてメモリセルを形成する方法

可変抵抗メモリセル構造およびその形成方法である。方法は、第一の電極を形成すること、前記第一の電極の上に絶縁材料を形成すること、前記第一の電極の表面を露出させるために前記絶縁材料にビアを形成すること、ガスクラスターイオンビームを使用して前記ビア内にヒーター材料を形成すること、前記ビア内に可変抵抗材料を形成すること、および、前記第一および第二の電極の間に前記ヒーター材料および可変抵抗材料が提供されるように第二の電極を形成すること、を含む。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

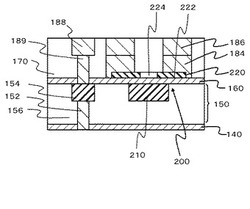

【課題】配線層に新たな機能を有する素子を設けた半導体装置を提供する。

【解決手段】半導体基板上に形成された第1配線層150、及び半導体素子200を備える。第1配線層150は、絶縁層156と、絶縁層156の表面に埋め込まれた第1配線154とを備える。半導体素子200は、半導体層220、ゲート絶縁膜160、及びゲート電極210を備える。半導体層220は、第1配線層150上に位置する。ゲート絶縁膜160は、半導体層220の上又は下に位置する。ゲート電極210は、ゲート絶縁膜160を介して半導体層220の反対側に位置する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】隣接したメモリセル間の干渉を抑制できるようにする。

【解決手段】素子分離絶縁膜4の空洞部の形成領域Rが、浮遊ゲート電極FGaと、浮遊ゲート電極FGc、FGdの直下方に位置する活性領域Saとの間に対向した領域内に設けられるため、当該浮遊ゲート電極FGaと素子分離領域Sbを挟んで対向する活性領域Saとの間の結合容量を低減できる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】ワード線間に空隙を有する不揮発性半導体記憶装置で、従来に比してワード線間の容量の増大を抑えることができる不揮発性半導体記憶装置を提供する。

【解決手段】シリコン基板1上にゲート絶縁膜11、多結晶シリコン膜12、電極間絶縁膜13および多結晶シリコン膜14が順に積層された積層ゲート構造MGと、積層ゲート構造MGの下部のチャネル領域を挟んで形成されるソース/ドレイン領域と、を有するメモリセルトランジスタが複数隣接して配置され、隣接する積層ゲート構造MG間に空隙AG1,AG2ができるように連続したシリコン酸化膜がメモリセルトランジスタ上に形成され、電極間絶縁膜13の形成位置よりも高い位置での基板面に平行な空隙AG1,AG2の開口面積が、その位置よりも低い位置での基板面に平行な空隙AG1,AG2の開口面積よりも狭くなるように、積層ゲート構造MGの側面にシリコン酸化膜20,21が形成される。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】微細な構造でも安定して製造可能な不揮発性記憶装置の製造方法を提供する。

【解決手段】第1の方向に延在する第1の配線と、前記第1の方向と非平行な第2の方向に延在する第2の配線と、前記第1の配線と前記第2の配線との間に挟持され、前記第1の配線と前記第2の配線とを介して供給される電流により、第1の状態と第2の状態との間を可逆的に遷移可能な記録層と、を有する不揮発性記憶装置の製造方法であって、前記第1の配線の層を形成する工程と、前記第1の配線の層の主面上に前記記録層の層を形成する工程と、前記記録層の層と前記第1の配線の層を選択的にエッチングして、前記第1の方向に延在する複数の積層体を形成する工程と、前記複数の積層体の間隙の表面に、気相成長法を用いて第1の絶縁層を形成する工程と、前記第1の絶縁層の上に、塗布法を用いて第2の絶縁層を形成する工程と、を備えたことを特徴とする不揮発性記憶装置の製造方法を提供する。

(もっと読む)

半導体集積回路装置

【課題】微細ピッチで配列するに好ましい垂直配線構造を持つ半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、回路が形成された半導体基板と、前記半導体基板上に複数層積層された機能素子アレイと、前記機能素子アレイの信号線を前記半導体基板上の回路に接続するための垂直配線とを備え、前記垂直配線は、ストライプ状溝が形成されたあとの絶縁層の前記ストライプ状溝の長手方向に分散的に配置されたメタル層の積み重ね構造として構成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】固体電解質メモリには書き換えを繰り返すことで固体電解質中のイオンA量及び電極の形状が変化してしまうため、安定した書き換えが困難であるという課題がある。

【解決手段】固体電解質層の抵抗変化によって情報を記憶または回路接続を変化させる半導体装置において、固体電解質層を例えばCu−Ta−S、それに隣接または近接するイオン供給層をCu−Ta−Oの組成にして、イオン供給層から供給されたイオンが固体電解質層内に導電パスを形成することにより、抵抗の高低により情報が記憶されるようにし、電気パルスを印加することで抵抗を変化させることができる。上記イオン供給層は例えばCu−Ta−O=1:2:6の組成比を持つ結晶であり、安定して書換え動作を行うことができる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】動作速度が向上し、信頼性の高い不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板101上に所定間隔を空けて形成され、順に積層された第1の絶縁膜102、電荷蓄積層103、金属酸化物を含む第2の絶縁膜104、及び制御ゲート電極105をそれぞれ有する複数のワードラインと、ワードラインの側面及びワードライン間の半導体基板表面を覆う膜厚が15nm以下の第3の絶縁膜110と、互いに隣接ワードラインの制御ゲート電極105間に形成された第4の絶縁膜111と、第3の絶縁膜110及び第4の絶縁膜111に囲まれ、互いに隣接するワードラインの電荷蓄積層間103に位置する空洞部112と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】MOSFETにおいて、ショートチャネル効果の抑制と移動度向上を両立させることを可能とする。

【解決手段】半導体基板13上にダミーゲート絶縁膜31を介してダミーゲート34を形成する工程と、ダミーゲート34の両側の半導体基板13にソース・ドレイン不純物領域23,24を形成する工程と、ダミーゲート34の両側の半導体基板13上にエクステンション領域25,26を形成する工程と、ダミーゲート34直下のソース側にソース不純物領域23のオーバーラップ領域27を形成する工程と、ダミーゲート34を除去し、該除去領域に露出したダミーゲート絶縁膜31を除去する工程と、除去領域に露出した半導体基板13にリセス形状15を形成する工程と、リセス形状15を形成した半導体基板13上にゲート絶縁膜21とゲート電極22とを順次形成する工程とを備えている。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】プログラムディスターバンス特性を向上させることができ、メモリセルの間の干渉現象を減らすことができるフラッシュメモリ素子の製造方法を提供する。

【解決手段】セレクトトランジスタ及びメモリセルを形成し、半導体基板にジャンクションを形成した後、ハードマスクパターン112を用いてセレクトトランジスタ及びこれと隣接したメモリセルの間111bの半導体基板100を過度エッチングすることにより、電子の移動を抑制することができるため、プログラムディスターバンス特性を向上させることができ、メモリセルの間にボイド113を形成することにより、メモリセルの間の干渉現象を減らすことができるため、フラッシュメモリ素子の信頼性を向上させることができる方法について開示する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】シリコンピラーを用いた縦型トランジスタを有する改良されたDRAMや相変化メモリ等の半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、シリコンピラー10によってセルトランジスタTrが構成され、シリコンピラー10の下部に位置する第1の拡散層11が基準電位配線PLに共通接続されている。ワード線方向に隣接するシリコンピラー10を覆うゲート電極14は互いに接触している。また、ゲート電極14は、ダミーゲート電極と補助ワード線を介して上層の配線に接続されている。層間絶縁膜61と層間絶縁膜62との間には、空洞60が形成されている。隣り合うキャパシタCpの大部分は、空洞60を介して隣接することから、キャパシタ間の容量が大幅に低減する。

(もっと読む)

半導体装置の製造方法

【課題】ボンディングパッドやヒューズ窓の形成に際して、MISFETの特性の劣化を抑制する。

【解決手段】半導体装置の製造方法は、半導体基板の上部に、MISFETに接続された配線15を形成するステップと、配線15上にパッシベーション膜16を形成するステップと、パッシベーション膜16をエッチングし、配線15の所定部分を露出する開口18を形成するステップと、開口18から露出した配線15を含む半導体基板を、H2ガス雰囲気中でアニールするステップと、を有する。配線15は、順次に積層された、バリアメタル層12、メタル層13、及び、キャップメタル層14を含む。

(もっと読む)

記憶装置及び半導体装置

【課題】記憶機能の信頼性の高い有機化合物を含む層を有する素子が設けられたフレキシブルな記憶装置及び半導体装置を提供する。

【解決手段】第1の電極層及103び第2の電極層106からなる一対の電極間に有機化合物を含む層105を有する記憶素子と、当該記憶素子を有する素子層と、素子層上に形成される封止層111を有し、封止層111には吸湿材108が含まれている記憶装置及び半導体装置である。吸湿材108としては、溶融シリカ、結晶シリカ、アルミナ、窒化珪素、窒化アルミニウム、窒化ホウ素、ゼオライト、アルカリ土類金属の酸化物、硫酸塩、または高吸水性ポリマーの粒子で形成される。

(もっと読む)

トランジスタ、メモリセルアレイ、及びトランジスタの製造方法

【課題】DRAMメモリセルをさらに縮小させると同時に、最適な特性を得る改良されたアクセストランジスタと,その製造方法を提供する。

【解決手段】集積回路のトランジスタ61,62は、第1及び第2のソース/ドレイン領域51,52と、第1及び第2のソース/ドレイン領域51,52に接続するチャネル領域53と、チャネルに流れる電流を制御するように構成されたゲート電極23とを備えている。ゲート電極23は、ゲート溝25に配されており、半導体基板の上表面10に規定されている。第1及び第2のソース/ドレイン領域51,52は、少なくとも深さd1で延びている。ここで、深さd1は、上記基板の上表面10から測定される。ゲート電極23の上表面23aは、上表面10に対する距離が深さd1未満になるように、半導体基板の上表面10の下に配されている。

(もっと読む)

半導体記憶装置、半導体装置、半導体記憶装置の製造方法および半導体装置の製造方法

【課題】メモリセルごとに書き込まれる電位のばらつきを抑えることが可能な半導体記憶装置、半導体装置、半導体記憶装置の製造方法および半導体装置の製造方法を提供する。

【解決手段】半導体記憶装置100は、半導体基板11と、半導体基板11上に形成されたゲート絶縁膜14と、ゲート絶縁膜14上に形成されたゲート電極15と、半導体基板11上部であってゲート電極15下を挟む一対の領域に形成された低濃度拡散領域16と、低濃度拡散領域16上に形成された電荷蓄積部18とを含むメモリセル1と、メモリセル1を覆うように半導体基板11上に形成され、所定波長のUVレーザ光を透過させる絶縁性の第1パッシベーション21と、第1パッシベーション21上に形成され、UVレーザ光を遮断し、電荷蓄積部18上に開口を有する第2パッシベーション23とを有する。

(もっと読む)

半導体装置

【課題】 半導体装置の面積を増大させること無く、半導体装置のドレイン電流を向上させることができる半導体装置を提供する。

【解決手段】 半導体基板10と、半導体基板10上に形成され、ゲート絶縁膜16を介して形成されるゲート電極18と、半導体基板10に形成され、ゲート電極18の両側方に位置する領域に形成されるn型のソース/ドレイン拡散層24と、半導体基板10上のゲート電極18両側部に形成され、ゲート電極18のチャネル領域に応力を与えるtensile膜26と、ソース/ドレイン拡散層24上にtensile膜26を貫通して形成される、導電体材料が埋め込まれたコンタクト30を備える。そして、ゲート電極18とソースコンタクト34間距離が、ゲート電極18とドレインコンタクト32間距離よりも広いことを特徴としている。

(もっと読む)

半導体装置及びその製造方法

【課題】 配線及びパターンの特定箇所を選択的に細らせて配線間隔を広げ、カバレッジの良い成膜条件でもエアギャップを形成することができ、所望の配線間の静電容量を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】 隣接するフローティングゲート電極層について互いの距離が上層から下地基板面までの間で徐々に離れるように上層から下地基板面へ向けて互いの層形状を選択的に細らせ、互いの距離が離れたフローティングゲート電極層の間にエアギャップを有する層間絶縁膜を備える。

(もっと読む)

半導体素子のランディングプラグコンタクト形成方法

【課題】 ランディングプラグコンタクト形成のためのCMP工程時、ポリシリコン膜とゲートハードマスク窒化膜との間の段差を防止できる半導体素子のランディングプラグコンタクト形成方法を提供すること。

【解決手段】 本発明では、ランディングプラグコンタクト(LPC)の分離のためのポリシリコンリセス(Recess)のために、既存のCMP工程を用いず、2ステップのエッチバック工程を用いる。すなわち、第1エッチバック工程では、等方性ドライエッチング(部分エッチング)を通してゲート電極パターンの間の空間(コンタクトホール上部)に発生したポリシリコン膜のシーム(Seam)を除去し、第2エッチバック工程では、ポリシリコン膜とハードマスク窒化膜とのエッチング速度が類似したレシピ(Recipe)を適用して、非等方性ドライエッチングを行う。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は、短チャネル効果を抑制すると共に、半導体基板の表面上に形成された表面ストラップと孔内に形成された導電層との界面に生じる抵抗を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板100の表面部分において、孔140の底部付近の内部表面を覆うキャパシタ絶縁膜150と、孔140の内部を埋め込むキャパシタ電極160と、孔140の内部表面を覆う絶縁膜180と、キャパシタ電極160上に絶縁膜180で覆われた内部を埋め込むように形成された所定の不純物を含む導電層190、210と、導電層210とソース領域290又はドレイン領域300とを電気的に接続するための表面接続層340と、孔140の内部表面を覆うように形成され、表面接続層340と導電層210との界面から所定の深さまで形成された、絶縁膜180より膜厚が薄い不純物拡散防止膜200とを備えることを特徴とする。

(もっと読む)

薄膜キャパシタ

【課題】

薄膜キャパシタに発生する応力を分散・低減して、リーク電流特性の劣化を抑え、歩留まりや信頼性の向上を図る。

【解決手段】

薄膜キャパシタの上部電極18の端部であって、直線的な傾斜20Aを有するように、層間絶縁膜20が形成される。すなわち、A点から上部電極18の端部までの距離をLとし、A−Bの主面上における距離をWとしたときに、W/2>Lの大小関係が成り立つように、層間絶縁膜20の傾斜20Aが形成される。これにより、該界面において薄膜キャパシタ側に生ずる応力が傾斜に沿って分散され、薄膜キャパシタの外に逃げるようになる。従って、薄膜キャパシタ内部に生ずる応力場の集中が緩和され、更にはリーク電流特性の劣化が抑制されるようになる。

(もっと読む)

21 - 40 / 42

[ Back to top ]