Fターム[5F083LA04]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | カラムデコーダ (735)

Fターム[5F083LA04]に分類される特許

101 - 120 / 735

半導体装置

【課題】相変化メモリを低電圧動作および高温の動作又は放置させる場合に、記録保持信頼性を向上させる技術を提供する。

【解決手段】読み出し電圧をセット電圧およびリセット電圧以上として高速動作させ、読み出し後に読み出し前の状態を再書込みする、いわゆる破壊読出しを行う。または、複数個のセルを用いて1ビットの情報を記録する、いわゆるオアセルを用いて、高温時の動作又は放置のける信頼性を向上させる。破壊読出しおよびオアセルを用いた相変化メモリに必要な、回路構成および動作方法を用いる。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bとを有する。駆動対象の記憶素子21に対して、電極215Aと電極215Bとの間に所定の閾値以上の電圧V1を印加して、半導体層212Nと半導体層213Nとの間の領域にそれらの半導体層同士を電気的に繋ぐ導電パスであるフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

半導体装置及びその試験方法

【課題】論理値の反転処理を行う回路をコアチップ側に設けることなく、TSVを含む電流パスラインのショート不良を検出する。

【解決手段】半導体装置10は、第1及び第2の電流パスSa,Sbと、これらとそれぞれ電気的に接続する第1及び第2のラッチ回路100a,100bと、第1のラッチ回路100aに第1のデータD1を供給するとともに、第2のラッチ回路100bに第1のデータとは逆の論理値を有する第2のデータD2を供給するドライバ回路101と、第1のデータD1が第1のラッチ回路100aに供給され、かつ第2のデータD2が第2のラッチ回路100bに供給されない第1の期間と、第2のデータD2が第2のラッチ回路100bに供給され、かつ第1のデータD1が第1のラッチ回路100aに供給されない第2の期間と、が交互に繰り返されるよう、ドライバ回路101を制御する制御回路104と、モニタ回路120とを備える。

(もっと読む)

半導体装置

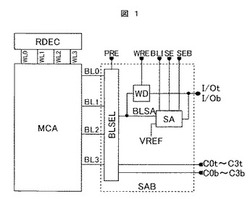

【課題】 電源遮断機能付きで記憶容量の増減変更を伴う設計が容易なSRAMマクロを有する半導体装置を提供する。

【解決手段】 本発明の半導体装置では、SRAMのメモリセルが複数配置されているメモリアレイと、メモリアレイへのデータの書き込みおよびメモリアレイからのデータの読み出しを行う第1の周辺回路と、メモリアレイおよび第1の周辺回路と電源線との接続を遮断するスイッチ群とを含むレイアウトの単位が複数配置されている。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層211P上の半導体層212N,213N間に対応する領域に設けられた下層側の誘電体膜216および上層側の導電体膜217と、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bと、導電体膜217と電気的に接続された電極215Cとを有する。駆動対象の記憶素子21に対して、電極215B,215C間に所定の閾値以上の電圧V1を印加して、誘電体膜216の少なくとも一部分を絶縁破壊させて導電体膜217,半導体層213N間に電流を流し、半導体層212N,213N間の領域にフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

抵抗変化素子の駆動方法、不揮発性記憶装置、抵抗変化素子および多値記憶方法

【課題】多値の記憶状態を安定して読み書きできる抵抗変化素子の駆動法を提供する。

【解決手段】第1電極2を基準とする第2電極4の電位である電極間電圧を抵抗変化素子10に印加することによって第1電極2と第2電極4との間の抵抗値である電極間抵抗値を可逆的に変化させる抵抗変化素子10の駆動方法であって、Vα<Vβ<0およびVγ>0およびRL<RM<RHを満たすVα、Vβ、Vγ、RL、RM、RHについて、電極間電圧Vαの印加によって電極間抵抗値をRLにする書き込み過程と、書き込み過程の後、電極間電圧Vγの印加によって電極間抵抗値をRMにする第1の消去過程と、第1の消去過程の後、電極間電圧Vβの印加によって電極間抵抗値をRHにする第2の消去過程とを有する。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置、およびその作製方法を提供することである。

【解決手段】基板上に下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、第1の加熱処理を行って第2の酸化物半導体膜を形成した後、選択的にエッチングして、第3の酸化物半導体膜を形成し、第1の絶縁膜および第3の酸化物半導体膜上に絶縁膜を形成し、第3の酸化物半導体膜の表面が露出するように絶縁膜の表面を研磨して、少なくとも第3の酸化物半導体膜の側面に接するサイドウォール絶縁膜を形成した後、サイドウォール絶縁膜および第3の酸化物半導体膜上にソース電極およびドレイン電極を形成し、ゲート絶縁膜およびゲート電極を形成する。

(もっと読む)

半導体記憶装置及びその高電圧制御方法

【課題】チャージポンプ等の高電圧生成部の回路面積を削減する。

【解決手段】半導体記憶装置は、ワードライン及びビットラインが接続されマトリクス状に配置された複数のメモリセル21と、ワードラインを駆動する複数のワードラインドライバ23a及び23b、電源電圧を昇圧して高電圧を生成するチャージポンプ11と、複数のメモリセル21のうちアクセスに関係のある箇所には高電圧が印加され、アクセスに関係のない箇所には電源電圧が印加されるように制御するX方向高電圧制御回路31及びY方向高電圧制御回路32とを備える。

(もっと読む)

半導体装置

【課題】上下電極間に有機化合物を設けて記憶素子を形成するが、有機化合物を含む層の

上に電極を形成した場合、電極の形成時の温度によっては有機化合物を含む層への影響が

あるため温度に制限がある。この温度の制限のため形成方法が限定され、希望通りの電極

を形成することができず、素子の微細化を阻害している問題があった。

【解決手段】絶縁表面を有する基板上に記憶素子及びスイッチング素子が配置された半導

体装置とし、前記素子は、同一平面に配置された第1の電極と第2の電極と有機化合物を

含む層とを有し、前記有機化合物を含む層は前記第1の電極と前記第2の電極との間に形

成され、電流は前記第1の電極から前記第2の電極へと流れ、前記第1の電極は、前記ス

イッチング素子と電気的に接続されている半導体装置である。

(もっと読む)

不揮発性半導体記憶装置

【課題】データ保持特性を向上させた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1配線と第2配線との間に配置され、抵抗を変化させる可変抵抗素子を有するメモリセルを備える。メモリセルは、可変抵抗層、第1電極層、第2電極層、及び第1バリアハイト制御層を備える。可変抵抗層は、可変抵抗素子として機能する。可変抵抗層は、炭素(C)、珪素(Si)、及び水素(H)を含み、又は炭素(C)、珪素(Si)、及び水素(H)を含み且つ窒素(N)及び酸素(O)の少なくともいずれか一方を含む。第1電極層は、可変抵抗素子の一方の面側に設けられている。第2電極層は、可変抵抗素子の他方の面側に設けられている。第1バリアハイト制御層は、絶縁物からなり且つ可変抵抗層の一方の面と第1電極層との間に構成されている。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置の駆動方法

【課題】新たな構造の半導体装置、及びその駆動方法を提供することを目的の一とする。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のpチャネル型トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電荷を保持させることで行う。また、保持期間において、メモリセルを選択状態とし、且つ、読み出し用トランジスタのソース電極およびドレイン電極を同電位とすることで、ノードに蓄積された電荷を保持する。

(もっと読む)

記憶装置

【課題】誤書込みを防止することが可能な記憶装置を提供する。

【解決手段】複数のメモリセルが直列に接続されたNANDセルユニットと、NANDセルユニットの一方の端子に接続する第1の選択トランジスタと、NANDセルユニットの他方の端子に接続する第2の選択トランジスタと、第1の選択トランジスタと接続するソース線と、該ソース線と交差し、且つ第2の選択トランジスタと接続するビット線とを有し、第1の選択トランジスタ及び第2の選択トランジスタは、チャネル領域が酸化物半導体層で形成されたトランジスタである。

(もっと読む)

半導体装置

【課題】制御チップと複数の被制御チップが積層されたタイプの半導体装置において、コマンド信号よりも層アドレス信号を早く伝送させる。

【解決手段】互いに異なる層情報を保持する複数の被制御チップCC0〜CC7と、被制御チップCC0〜CC7に対して層アドレス信号A13〜A15及びコマンド信号ICMDを共通に供給する制御チップIFとを備える。層アドレス信号A13〜A15を構成する各ビットは、複数の第1の貫通電極のうち、被制御チップごとに並列接続された少なくとも2本の貫通電極を経由して伝送され、コマンド信号ICMDを構成する各ビットは、出力切り替え回路及び入力切り替え回路によって選択された対応する1本の貫通電極を経由して伝送される。これにより、コマンド信号ICMDよりも先に層アドレス信号A13〜A15が各被制御チップに到達する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供すること。

【解決手段】トランジスタと、容量素子と、を有し、トランジスタは、第1の酸化物半導体層と、第1の酸化物半導体層と接するソース電極およびドレイン電極と、第1の酸化物半導体層と重なるゲート電極と、第1の酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、容量素子は、ソース電極またはドレイン電極と、ソース電極またはドレイン電極と接する第2の酸化物半導体層と、第2の酸化物半導体層と接する容量素子電極と、を有する半導体装置である。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルアレイおよび周辺回路領域の素子分離領域の深さを調節しつつ、周辺回路部の素子分離領域に形成されるマイクロトレンチ形状の影響を抑制し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板上に設けられデータを記憶する複数のメモリセルを含むメモリセルアレイと、半導体基板上に設けられメモリセルアレイを制御する周辺回路部とを備えている。素子分離部は、複数のメモリセルおよび周辺回路部が形成されるアクティブエリア間に設けられている。側壁膜は、周辺回路部におけるアクティブエリアの側面に設けられている。

(もっと読む)

不揮発性半導体記憶装置

【課題】面積の縮小を図る。

【解決手段】不揮発性半導体記憶装置は、複数のメモリストリング200を具備し、各メモリストリングは、一対の柱状部A、および一対の柱状部の下端を連結させるように形成された連結部Bを有する半導体層SPと、柱状部に直交したコントロールゲートCGと、一対の柱状部の一方と直交し、コントロールゲートの上方に形成された第1選択ゲートSGSと、一対の柱状部の他方と直交し、コントロールゲートの上方に形成され、第1選択ゲートと同一レベルでかつ一体である第2選択ゲートSGDと、柱状部とコントロールゲートとの各交差部に形成されたメモリセルトランジスタMTrと、柱状部と第1選択ゲートとの交差部に形成された第1選択トランジスタSSTrと、柱状部と第2選択ゲートとの交差部に形成された第2選択トランジスタSDTrと、を含む。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

101 - 120 / 735

[ Back to top ]