Fターム[5F083LA04]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | カラムデコーダ (735)

Fターム[5F083LA04]に分類される特許

721 - 735 / 735

非揮発性メモリの可変プログラミング

システムと方法は、様々な実施形態に従って非揮発性半導体メモリのプログラム妨害を抑制することを提供する。一実施形態では、NANDストリングの最後のワードラインに接続されているもの等のような選択メモリセルが、他のセル又はワードラインをプログラムするために利用される対応レベルと異なる一又は複数のプログラムベリファイレベル又は電圧を利用してプログラムされる。一実施形態は、プログラムオペレーションの間にストリングのためにプログラムされるべき最後のワードラインをプログラミングする際に、選択シジカル状態のためにより低い閾電圧ベリファイレベルを利用することを含む。他の実施形態は、選択シジカル状態に最後のワードラインのメモリセルをプログラムするために、より低いプログラム電圧を供給することを含む。いくつかの実施例においてより低いベリファイレベルを利用してプログラムされた状態を読み込むために、追加の読み込みレベルが設けられる。一実施形態では、NANDストリングのためにプログラムされるべき最後のワードラインのような選択メモリセル又はワードラインをプログラミングする際に、通常のステップサイズより大きい第2プログラム電圧ステップサイズが利用される。  (もっと読む)

(もっと読む)

電荷を非対称に捕獲する多値メモリセル

【課題】高メモリ密度、低電力消費、及び高信頼性を達成可能なNAND型多値メモリセルを提供する。

【解決手段】NAND型多値メモリセルは、2つのドレイン/ソース領域を基板に有する。2つのドレイン/ソース領域の間における基板の上方には、酸化物−窒化物−酸化物構造体が形成される。このうち窒化物層は、電荷を非対称に捕獲する層として機能する。酸化物−窒化物−酸化物構造体の上方には、制御ゲートが配置される。ドレイン/ソース領域に非対称のバイアスをかけることで、ドレイン/ソース領域に高い電圧が生じ、これによってドレイン/ソース領域の略近傍における電荷捕獲層にGIDL(ゲートに起因するドレインでの電流漏れ)正孔注入処理を行い、正孔を非対称な分布で注入する。

(もっと読む)

半導体装置

相変化メモリを低電圧動作および高温の動作又は放置させる場合に、記録保持信頼性を向上させること。

読み出し電圧をセット電圧およびリセット電圧以上として高速動作させ、読み出し後に読み出し前の状態を再書込みする、いわゆる破壊読出しを行う。または、複数個のセルを用いて1ビットの情報を記録する、いわゆるオアセルを用いて、高温時の動作又は放置のける信頼性を向上させる。破壊読出しおよびオアセルを用いた相変化メモリに必要な、回路構成および動作方法を用いる。

(もっと読む)

High−K材料とゲート間プログラミングとを使用する不揮発性メモリ・セル

不揮発性メモリ・デバイスは、ソース/ドレイン領域の間のチャネル領域と、フローティング・ゲートと、制御ゲートと、チャネル領域とフローティング・ゲートとの間の第1の誘電体領域と、フローティング・ゲートと制御ゲートとの間の第2の誘電体領域とを有する。第1の誘電体領域はHigh−K材料を含む。不揮発性メモリ・デバイスは、フローティング・ゲートと制御ゲートとの間で第2の誘電体領域を介して電荷を移動させることによってプログラムおよび/または消去される。 (もっと読む)

記憶素子、メモリ回路、半導体集積回路

【解決手段】第1の可変抵抗(5)は、第1の端子(7)と第3の端子(9)との間に接続され、第1の端子(7)と第3の端子(9)との間に印加されるパルス電圧の極性に応じてその抵抗値を増加/減少させる。第2の可変抵抗(6)は、第3の端子(9)と第2の端子(8)との間に接続され、第3の端子(9)と第2の端子(8)との間に印加されるパルス電圧の極性に応じてその抵抗値を増加/減少させる。第1の端子(7)と第3の端子(9)との間および第3の端子(9)と第2の端子(8)との間に所定のパルス電圧を印加して第1および第2の可変抵抗(5,6)の抵抗値を可逆的に変化させることにより1ビットあるいは多ビットの情報を記録する。 (もっと読む)

縦型スプリットゲートNROMメモリ装置及びその形成方法

【課題】NROMセルの利点と縦型メモリセルの利点とを備えるメモリデバイスを提供する。

【解決手段】スプリットゲート縦型NROMメモリセル(1890)は、複数の酸化物柱状体(1830、1831)から構成される。複数の酸化物柱状体の各々の上部にはソース/ドレイン領域(1840、1841)が形成される。溝部が、酸化物柱状体の各対の間に形成される。ポリシリコン制御ゲート(1800)が、酸化物柱状体の対の間の溝部に形成される。ポリシリコンプログラムゲート(1805、1806)が、制御ゲートと各酸化物柱状体との間に形成される。プログラムゲートは、各酸化物柱状体の側壁に沿って延在する。ゲート絶縁層(1802、1803)が、各プログラムゲートとその近傍の酸化物柱状体との間に形成される。各ゲート絶縁層は、少なくともひとつの電荷を捕獲する電荷捕獲構造を有する。一実施形態において、ゲート絶縁構造は、酸化物−窒化物−酸化物の層である。中間絶縁層(1822、1824)が、プログラムゲートと制御ゲートとの間に形成される。

(もっと読む)

自己整合型電荷分離構造NROMフラッシュメモリ

【課題】電荷捕獲領域が重ならずにセルを小さくすることが可能なトランジスタを提供する。

【解決手段】窒化物リードオンリーメモリ(NROM)セルは、窒化物層を有し、前記窒化物層は、トランジスタの中心部の下方に配置されない。前記窒化物層を有するゲート絶縁層は、2つの部分を有する。各部分は、構造分離された(structurally defined and separated)電荷捕獲領域を有する。電荷は、トランジスタの動作方向に応じて、ある特定の捕獲領域に蓄積される。前記ゲート絶縁層の前記2つの部分は、ポリシリコンゲート構造体の中間部分から外側部分を分離する。

(もっと読む)

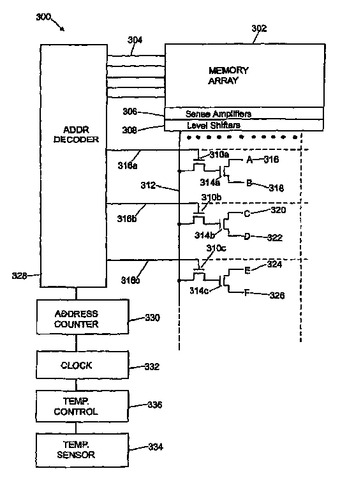

ビットライン間の結合補償のある不揮発性メモリおよび方法

メモリ蓄積ユニットの1つの連続するページをプログラムするとき、メモリ蓄積ユニットは、その目標の状態に達してプログラミングが禁止されるか、或いはそれ以上のプログラミングからロックアウトされる度に、なおプログラムされつつある隣接するメモリ蓄積ユニットに動揺を生じさせる。本発明は、プログラミングの一部として、動揺に対するオフセットがなおプログラムされつつある隣接するメモリ蓄積ユニットに加えられるようになっている回路および方法を提供する。このオフセットは、プログラミングが禁止されているメモリ蓄積ユニットとなおプログラムされつつあるメモリ蓄積ユニットとの隣接するビットライン間の制御された結合によって加えられる。このようにして、高密度メモリ蓄積ユニットを並列にプログラムする動作に固有のエラーが除去されるか、或いは最小にされる。  (もっと読む)

(もっと読む)

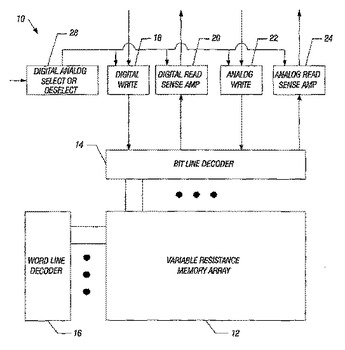

アナログ相変化メモリ

相変化材料を使ってアナログメモリを形成することができる。相変化材料は複数の抵抗状態のうちの一つをとり、それが保存すべき特定のアナログ特性を定義する。  (もっと読む)

(もっと読む)

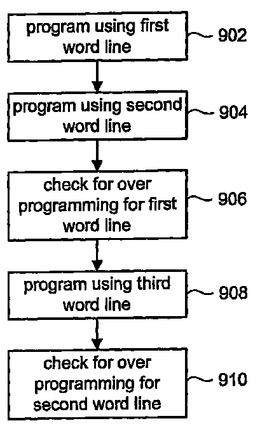

隣接するメモリセルのプログラミングの後にオーバー・プログラミングされたメモリセルを検出する技術

非揮発性半導体メモリシステム(又は他のタイプのメモリシステム)において、メモリセルは、その閾電圧を変更することによってプログラミングされる。システム内の様々なメモリセルに対するプログラミングのタイミングが異なることが原因で、いくつかのメモリセルは、オーバー・プログラミングされてしまう可能性がある。即ち、例えば、セルの閾電圧が、目的とされた値、又は、目的とされた範囲から外れてしまう可能性がある。本発明は、セルに対するプログラミングが原因で、それに隣接する行のメモリセルがオーバー・プログラミングされたか否かを判断することを含んでいる。

(もっと読む)

(もっと読む)

フラッシュ/ダイナミックランダムアクセスメモリフィールドプログラマブルゲートアレイ

集積回路デバイスにおいて2つのノードを選択的に相互接続するための回路は、複数のワード線及び複数のビット線を有するメモリアレイを含む。リフレッシュトランジスタは複数のビット線のうち一本に接続されたソース、ダイナミックランダムアクセスメモリワード線に接続された制御ゲート、及びドレインを有する。スイッチトランジスタはリフレッシュトランジスタのドレインに接続されたゲート、一番目のノードに接続されたソース、及び二番目のノードに接続されたドレインを有する。アドレスデコーダはワード線とダイナミックランダムアクセスメモリワード線に周期信号を供給する。  (もっと読む)

(もっと読む)

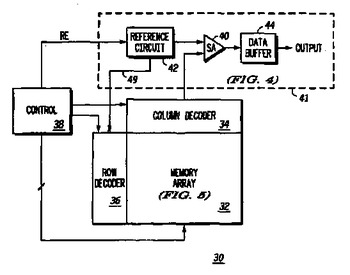

不揮発性メモリにおける基準トランジスタ用可変ゲート・バイアス

不揮発性メモリ(30)はナノクリスタルメモリセル(50、51、53)を備える。メモリセルトランジスタ(50、51、53)のプログラム及び消去閾値電圧は、プログラム/消去動作の回数の関数として上昇する。読み出し動作の間、基準トランジスタ(46)がセル電流と比較するための基準電流を供給する。基準トランジスタ(46)がナノクリスタルを含まないことを除いて、基準トランジスタ(46)は、メモリセルトランジスタ(50、51、53)を製造する際に用いるのと同様のプロセスで製造される。同様のプロセスを用いて基準トランジスタ(46)及びメモリセルトランジスタ(50、51、53)双方を製造することにより、基準トランジスタ(46)の閾値電圧は、メモリセルトランジスタ(50、51、53)の閾値電圧のずれに追従する。基準トランジスタ(46)のゲートにバイアスをかけるために、読み出し制御回路(42)が設けられている。読み出し制御回路(42)は、基準トランジスタ(46)のドレイン電流を検知し、基準電流をセル電流に対して実質的に一定値に維持するように、ゲートバイアス電圧を調節する。  (もっと読む)

(もっと読む)

不揮発性メモリデバイス

不揮発性メモリデバイス(100)は、基板(110)、絶縁層(120)、フィン(210)、複数の誘電層(310〜330)及び制御ゲート(510/520)を備える。絶縁層(120)は、基板(110)上に形成され、フィン(210)は、絶縁層(120)上に形成される。誘電層(310〜330)は、このフィン(210)を覆うように形成され、制御ゲート(510/520)は、誘電層(310〜330)上に形成される。誘電層(310〜330)は、メモリデバイス(100)の電荷格納構造として機能する酸化物−窒化物−酸化物層を備える。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】 多ビットのデータを入出力可能であって、動作速度の遅延や消費電力の増大を抑えたDRAMを提供する。

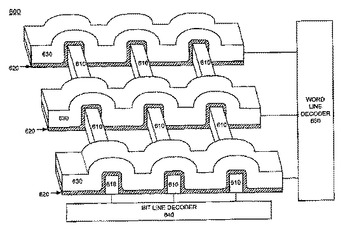

【解決手段】 このDRAMでは、多数のグローバル入出力線対GIOがサブワードドライバ領域24間のメモリセルアレイ上を走る。ローカル入出力線対LIOはメモリサブブロック26ごとに複数に分割される。グローバル入出力線対GIOとローカル入出力線対LIOを接続するスイッチング素子30はセンスアンプ領域22上に分散して配置される。1つのローカル入出力線対LIOには複数のビット線対が共通に接続される。

(もっと読む)

不揮発性半導体記憶装置

【課題】NANDセル型EEPROMのデータ消去後に、ビット線コンタクト部とセルPウエルとの接合の順方向電流によるラッチアップを防止する。

【解決手段】NANDセル型EEPROMにおいて、浮遊ゲートおよび制御ゲートを有する不揮発性のメモリセルを少なくとも1つ含むメモリセルユニットと、メモリセルユニットが形成されるメモリセルウエルCPWELL、CNWELLと、メモリセルユニットの一端に接続された第1の信号線BLi と、メモリセルユニットの他端に接続された第2の信号線CELSRCと、メモリセルの記憶データを消去する際、メモリセルウエルに消去電圧を所定期間印加して消去動作を行わせた後、第1の信号線および第2の信号線をフローティング状態にして、メモリセルウエルの消去電圧を放電させるように制御する制御回路を具備する。

(もっと読む)

721 - 735 / 735

[ Back to top ]