Fターム[5F083LA19]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | 配線レイアウト (4,019) | プレート線 (97)

Fターム[5F083LA19]に分類される特許

1 - 20 / 97

半導体メモリ装置およびその駆動方法

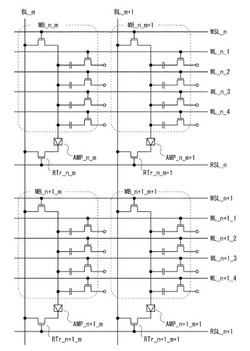

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。第n行のメモリブロックはサブビット線SBL_n_mと複数のメモリセルを有する。メモリセルはトランジスタと容量素子を直列に接続し、容量素子の電極の一をサブビット線SBL_n_mに接続する。さらに第n行のメモリブロックは書き込みトランジスタWTr_n_mと読み出しトランジスタRTr_n_mを有し、また、読み出しトランジスタRTr_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの電位変動を増幅回路AMP_n_mで増幅する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】 可変抵抗素子への電圧印加極性が異なる2種類の書き込み動作後の各ベリファイ動作を夫々低消費電力且つ高速に実行可能な半導体記憶装置を提供する。

【解決手段】 書き込み回路22が、メモリセルの一端側から可変抵抗素子を経由して他端側へ電流を流すことで可変抵抗素子の電気抵抗を低抵抗化させるセット動作と、メモリセルの他端側から可変抵抗素子を経由して一端側へ電流を流すことで可変抵抗素子の電気抵抗を高抵抗化させるリセット動作を夫々実行可能に構成され、読み出し回路21が、メモリセルの一端側から可変抵抗素子を経由して他端側へ電流を流すことで可変抵抗素子の抵抗状態を読み出す第1読み出し動作と、メモリセルの他端側から可変抵抗素子を経由して一端側へ電流を流すことで可変抵抗素子の抵抗状態を読み出す第2読み出し動作を夫々実行可能に構成されている。

(もっと読む)

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

半導体装置

【課題】一定時間電力が供給されない状況でも記憶内容の保持が可能な半導体装置を提供すること。さらに、半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させること。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料として、ワイドバンドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、トランジスタの下に設けた配線層と、酸化物半導体膜の高抵抗領域と、ソース電極とを用いて容量素子を形成することで、トランジスタと容量素子の占有面積の低減を図る。

(もっと読む)

半導体装置および半導体装置の制御方法

【課題】信頼性を確保しつつ、高速動作を実現することができる半導体装置を提供する。

【解決手段】抵抗変化素子10を有するメモリセル11と、メモリセル11に印加する電圧を制御する制御部80と、を備え、抵抗変化素子10は、第1の金属材料を含有する下部電極14と、第2の金属材料を含有する上部電極16と、酸素を含有する絶縁膜12と、を有しており、第1の金属材料は、第2の金属材料よりも規格化酸化物生成エネルギーが大きく、制御部80は、絶縁膜12の抵抗値を高抵抗化させる動作時および低抵抗化させる動作時において上部電極16に正電圧を印加し、絶縁膜12の抵抗値を読み出す動作時において下部電極14に正電圧を印加する。

(もっと読む)

半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供する

ことを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウ

ム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて

、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化

物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以

下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有

し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でス

パッタリングを行う。

(もっと読む)

記憶素子、信号処理回路および記憶素子の駆動方法

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路を提供する。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。例えば、容量素子の一方の電極を位相反転素子の入力あるいは出力に接続し、他方の電極をスイッチング素子に接続する。上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

半導体記憶装置

【課題】CMOSプロセスで、ダイナミック型半導体記憶装置を形成し、ロジックとの混載に適したダイナミック型半導体記憶装置を実現する。

【解決手段】メモリセル(MC)のワード線(WL)を形成する導電線(3)とメモリセルセルプレート電極(CP)を形成する導電線(5)とを、異なる配線層に形成する。対をなすビット線に並行してメモリセルを接続し、2つのメモリセルで1ビットのデータを記憶する。

(もっと読む)

半導体基板の作製方法

【課題】半導体基板の欠陥を低減する。また、歩留まり高く欠陥の少ない半導体基板を作製する。また、歩留まり高く半導体装置を作製する。

【解決手段】支持基板に酸化絶縁層を介して半導体層を設け、該半導体層の端部における、支持基板及び酸化絶縁層の密着性を高めた後、半導体層の表面の絶縁層を除去し、半導体層にレーザ光を照射して、平坦化された半導体層を得る。半導体層の端部において、支持基板及び酸化絶縁層の密着性を高めるために、半導体層の表面から、レーザ光を照射する。

(もっと読む)

強誘電体メモリおよびその動作方法

【課題】ワード線を昇圧せずにセル内のノードを電源電圧に駆動する。

【解決手段】強誘電体メモリは,複数のワード線と複数のプレート線と複数のビット線対と複数のチャージ線とメモリセルとを有する。メモリセルは,ワード線にゲートが接続されビット線対に第一のソース・ドレインがそれぞれ接続された一対の第一導電型MOSFETと,一対の第一導電型MOSFETの第二のソース・ドレインとプレート線との間にそれぞれ設けられた一対の強誘電体キャパシタと,一対の強誘電体キャパシタとチャージ線との間に設けられゲートとドレインとが交差接続された一対の第二導電型MOSFETとをそれぞれ有する。そして,チャージ線駆動回路は,読み出し動作時および書き込み動作時にチャージ線を電源電圧に駆動する。

(もっと読む)

強誘電体メモリおよびその制御方法

【課題】セルデータ読み出しのシグナルマージンを向上させることができる強誘電体メモリおよびその制御方法を実現する。

【解決手段】本発明の実施形態における強誘電体メモリは、セルキャパシタとセルトランジスタとが並列接続された複数のメモリセルと、隣り合う2つのメモリセルにおいてセルキャパシタの下部電極同士または上部電極同士が接続されるよう複数のメモリセルが直列に接続されて、その一端がビット線(/BL、BL)に接続され、他端がプレート線(/PL0、PL0)に接続されたセルブロック(MB0、MB1)と、下部電極がプレート線(/PL0、PL0)に電気的に接続される場合と、上部電極がプレート線(/PL0、PL0)に電気的に接続される場合とでセルキャパシタの電極間にかかる電界が同じ方向に印加されるようにプレート線(/PL0、PL0)およびビット線(/BL、BL)を制御する制御回路11および12を有する。

(もっと読む)

半導体記憶装置

【課題】ワード線間の寄生容量が相対的に大きくなっても性能が低下しない半導体記憶装置を提供する。

【解決手段】第1の方向に配線された複数のワード線と、第1の方向と交差する方向に配線された複数のビット線と、複数のワード線とビット線との交点に対応して設けられた複数のDRAMセルを備えるメモリセルアレイと、複数のワード線を駆動するワード線ドライバと、複数のワード線それぞれに接続されメモリセルアレイを間に挟んで、ワード線ドライバに対して反対側に配置され、当該ワード線に隣接するワード線が選択されたときに導通して当該ワード線を非選択電位に接続し、当該ワード線が選択されたときに非導通となる複数のワード線電位安定化トランジスタと、を備える。

(もっと読む)

半導体装置の製造方法

【課題】シリンダ状下部電極の型材となる犠牲層間絶縁膜を除去する際に、倒壊を防止する梁が形成されることで、梁と下部電極の接続部でキャパシタのリーク電流が増加する。

【解決手段】梁となる層、例えばカーボン膜86を介装した犠牲層間絶縁膜24にシリンダホールを形成し、シリンダ孔内にキャパシタの下部電極51を形成し、続いて、犠牲層間絶縁膜24をウェットエッチングにて選択的に除去した後、カーボン膜86をドライ条件で選択的に除去する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】電極に挟み込まれる強誘電体膜を特性のばらつきなく形成することのできる半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板Sと、半導体基板S上に形成された一対のソース/ドレイン拡散層11を有するセルトランジスタTと、セルトランジスタTに接続された強誘電体キャパシタCとを備える。セルトランジスタT及び強誘電体キャパシタCにより1つのメモリセルが構成される。強誘電体キャパシタCは、半導体基板Sの表面に垂直な方向を長手方向として延びる電極31と、電極31の側面に接するように設けられた強誘電体膜32と、半導体基板Sの表面に垂直な方向を長手方向として延び且つ電極31との間に強誘電体膜32を挟み込むように設けられた電極31とを備える。強誘電体膜32は、有機材料により構成されている。

(もっと読む)

半導体記憶装置

【課題】データ伝送速度を高めつつ、メモリ面積も縮小する。

【解決手段】メモリ領域1のビット線BLは、Y方向に延びて第1センスアンプ領域2に形成された第1センスアンプ回路SA1に接続される。ローカルデータ線LDQ、BLDSが、第1センスアンプ領域2、配線領域5を介して第2センスアンプ領域3まで配設される。第2センスアンプ領域3の第2センスアンプ回路SA2からは、メインデータ線MDQ、BMDQが、X方向に延びてメモリ領域1上に最上層のM4配線として配設される。

(もっと読む)

半導体装置

【課題】 従来の比例縮小側(係数α、α>1)を適用した平面型MOSTのしきい電圧のばらつきの標準偏差σ(VT)が、微細化とともに、すなわちαを大きくするとともに大きくなり、動作電圧が低くできないという問題がある。

【解決手段】 フィンの高さをチャンネル長よりも高くしたFinFET構造によって上記の問題を解決する。

(もっと読む)

半導体記憶装置、および半導体集積回路

【課題】不揮発性半導体メモリでは、プロセスの微細化、搭載容量の増加、低電圧化が進んでビット単位での保持電荷量が減少し、高温下環境などではさらに保持電荷量が低下し、保持データが読み出せないエラーが発生しがちなのを防止する。

【解決手段】高信頼性領域8に対してデータの書き込み、読み出しが行われる場合には、1つのワードドライバ13によって2本のワード線WLが駆動されるとともに、1つのセルプレートドライバによって2本のセルプレート線CPが駆動される。そこで、同一のビット線対BL/XBLに接続される2つずつの17が同時に選択される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】選択トランジスタと抵抗変化素子との間の配線抵抗を低減して、抵抗変化素子の消去動作を安定して行うことを可能にする半導体記憶装置とその製造方法を提供する。

【解決手段】半導体基板11に形成された第1MOSトランジスタ2と、半導体基板11に形成されていて第1MOSトランジスタ2の二つの第1拡散層16A,17Aの一つの第1拡散層17Aを共通の拡散層とする第2MOSトランジスタ3と、第1MOSトランジスタ2の第1ゲート電極13Aと第2MOSトランジスタ3の第2ゲート電極13Bとの間に第1,第2サイドウォール絶縁膜15A,15Bを介して形成されていて共通の拡散層18に接続された抵抗変化素子4を有する。抵抗変化層22は、金属酸化物膜からなる記憶層24と、記憶層24に金属イオンを供給もしくは記憶層24に供給した金属イオンを受給するイオン源層25からなる。

(もっと読む)

半導体装置

【課題】高速アクセス動作を実現する半導体記憶装置を提供する。

【解決手段】複数の正規メモリセルを含むメモリセルアレイと複数のセンスアンプ回路からなる半導体記憶装置において、メモリセルアレイには、所望のデータの書込み及び読出し動作に利用する正規メモリセルMCと、電源ノイズを低減するための平滑容量(具体的には平滑容量に利用するダミーセルDMC)を有する。また、ダミーセルDMCのワード線は、正規メモリセルMCのワード線と同じタイミングで活性化する。また、データ線のプリチャージレベルはVDDとし、ダミーセルDMCの一部を参照レベル発生用のメモリセルとして利用しても良い。この場合、正規メモリセルMCのワード線の非活性化をダミーセルDMCのワード線の非活性化よりも先行的に実施する。さらに、隣接データ線同士を短絡するための回路を付加しても良い。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体膜の局所的な損傷を抑制しながらリーク電流を十分に低減することができる構造の強誘電体キャパシタを備えた半導体装置及びその製造方法を提供する。

【解決手段】素子領域21が延びる方向に対して45度程度傾斜した方向に延びるゲート電極4(ワード線)がゲート絶縁膜を介して半導体基板上に形成されている。2本のゲート電極4により、各素子領域21が3分割されている。各素子領域21には、2個ずつMOSトランジスタが形成されており、各素子領域21の中央部に設けられたWプラグ10にビット線11が接続され、両端部に設けられたWプラグ9に強誘電体キャパシタ15の下部電極が接続されている。ビット線11が延びる方向は、素子領域21が延びる方向から45度程度傾斜している。

(もっと読む)

1 - 20 / 97

[ Back to top ]