Fターム[5F083MA01]の内容

Fターム[5F083MA01]の下位に属するFターム

セルフアラインコンタクト (383)

コンタクト下地層を有するもの (205)

コンタクト部にバリア層を有するもの (830)

プラグを有するもの (4,125)

Fターム[5F083MA01]に分類される特許

101 - 115 / 115

半導体装置の製造方法及び半導体装置

【課題】MTJ特性が高く、かつ、低消費電力化を図った半導体装置の製造方法を得る。

【解決手段】MTJ素子を覆って全面に層間絶縁膜16を形成した後、層間絶縁膜16を選択的に貫通させ、ハードマスク層15上の層間絶縁膜16の一部にビアホール17を形成する。このビアホール17の形成深さd17は、コンタクトプラグ形成用の導電膜のCMP処理時に生じる最大オーバー除去量CX2より小さい値に設定され、ハードマスク層15の膜厚t15及びビアホール17の形成深さd17と最大オーバー除去量CXとの関係において、{d17+t15>CX2}(第3の設定条件)を満足するように形成する。その後、全面に導電膜を堆積後、上記CMP処理を施すことによりビアホール17内にコンタクトプラグを形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】 リフレッシュ動作を必要とせず、かつ、高集積化・大容量化を実現する半導体記憶装置を提供する。

【解決手段】 半導体基板1上に形成されたメモリセルと、第1電荷保持部と、第2電荷保持部と、第1アクセストランジスタと、第1リークトランジスタ522Aと、第2アクセストランジスタと、第2リークトランジスタと、層間絶縁膜16と、層間絶縁膜16上に形成され、第1電荷保持部に接続されたメモリセル内の第1MISFET56A(Metal-Insulator-Semiconductor Field Effect Transistor)と、層間絶縁膜16上に形成され、第2電荷保持部と接続されたメモリセル内の第2MISFET(Metal-Insulator-Semiconductor Field Effect Transistor)とを備える。

(もっと読む)

薄膜キャパシタ

【課題】

薄膜キャパシタに発生する応力を分散・低減して、リーク電流特性の劣化を抑え、歩留まりや信頼性の向上を図る。

【解決手段】

薄膜キャパシタの上部電極18の端部であって、直線的な傾斜20Aを有するように、層間絶縁膜20が形成される。すなわち、A点から上部電極18の端部までの距離をLとし、A−Bの主面上における距離をWとしたときに、W/2>Lの大小関係が成り立つように、層間絶縁膜20の傾斜20Aが形成される。これにより、該界面において薄膜キャパシタ側に生ずる応力が傾斜に沿って分散され、薄膜キャパシタの外に逃げるようになる。従って、薄膜キャパシタ内部に生ずる応力場の集中が緩和され、更にはリーク電流特性の劣化が抑制されるようになる。

(もっと読む)

半導体装置の製造方法

【課題】ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】ソース/ドレイン領域の一方になり、かつビット線にもなる第1の不純物拡散層24の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜13が設けられる。キャパシタ絶縁膜13を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化に有利で信頼性を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、ゲート電極上に金属層31を備えたトランジスタSTと、順次設けられた第1バリア膜23、第1絶縁層24、第2バリア膜25、第2絶縁層26と、前記第2バリア膜に第1幅W1で開口し第1方向に伸びる溝と、前記第2絶縁層を貫通して前記第2バリア膜中に底部40を有し前記底部が前記第1方向に交差する第2方向に前記第1幅よりも大きい第2幅W2を有するコンタクトホール上部39−1と、前記コンタクトホール上部から前記溝を介して前記第1絶縁層および第1バリア膜を貫通して前記拡散層上に設けられ前記第2方向に上面が前記1幅W1を有するコンタクトホール下部39−2と、前記コンタクトホール上部内および前記コンタクトホール下部内に連続して導電体が埋め込まれたコンタクト39を具備する。

(もっと読む)

強誘電体メモリとその製造方法

【課題】 キャパシタの面積を増加させずに高い信頼性が得られる強誘電体メモリとその製造方法を提供する。

【解決手段】 記憶素子選択用のトランジスタ2を含む回路が形成された半導体基板1の上に層間絶縁膜4を形成し、この層間絶縁膜4に対してCHF3 を含むガス系をエッチングガスとするプラズマエッチング法でコンタクトホールを形成する。これにより、強誘電体キャパシタ10側が広く、トランジスタ2の拡散層2a側が狭く形成されたコンタクトホールが得られる。コンタクトホールにタングステン等の導電性材料を充填するとき、材料ガスがコンタクトホール内にむらなく供給されるので、中央部にシームと呼ばれる空隙が発生しない。これにより、セルプラグ20の表面が均一で平坦に仕上がり、このセルプラグ20上に特性の良い強誘電体キャパシタ10を形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 コンタクトホール側壁に形成するスペーサ用絶縁膜がシリコン基板と接触しない構成とし、且つRIE加工工数を低減する。

【解決手段】 NANDフラッシュメモリで、メモリセル領域2のゲート電極5、5間のコンタクトホール8と周辺回路領域3の高耐圧トランジスタ6のコンタクトホール9とに、層間絶縁膜20の側壁にスペーサとしてのシリコン窒化膜21を形成する構成である。シリコン窒化膜21の下端部は、シリコン基板1との間に、シリコン酸化膜17もしくは18を介在させている。シリコン基板1へのストレスを緩和してゲート酸化膜の電子トラップを低減する。また、シリコン窒化膜のRIE加工回数を減らすことができる。

(もっと読む)

スタガ配置のメモリ・セル・アレイ

セルをアレイ中に配置する方法が開示されている。方法は、第1のアレイ中にセルを複数回(600、602、604)配置する工程を含む。セルは、また第2のアレイ中にも複数回(606、608、610)配置される。第2のアレイは、第1のアレイからオフセット距離(O2)だけ離して隣接して配置される。  (もっと読む)

(もっと読む)

相変化記憶素子及びその製造方法

【課題】 相変化膜の相変化に必要とする書込電流を低めることができる相変化記憶素子及びその製造方法を提供する。

【解決手段】 下部構造を有する半導体基板上に形成、基板所定部分を露出させる第1、第2コンタクトホールを有する第1絶縁膜、第1コンタクトホールを埋込む導電プラグ、第1絶縁膜上に形成、第2コンタクトホールを埋込むビットライン、第1絶縁膜上に形成した第2絶縁膜、第2絶縁膜上に順次形成した上部電極、相変化膜パターン及びハードマスク膜、第2絶縁膜上に形成、ハードマスク膜上部表面を露出させる第3絶縁膜、第3、第2絶縁膜内を貫通形成し導電プラグを露出させる第3コンタクトホール、ハードマスク膜上に形成、相変化膜パターンを露出させる第4コンタクトホール、第3、第4コンタクトホールを埋込む第1、第2下部電極コンタクト、第3絶縁膜上に形成、第1、第2下部電極コンタクトが各々連結された下部電極を有する。

(もっと読む)

半導体装置及び強誘電体メモリ、半導体装置の製造方法

【課題】 スタック型でありながら必要なサイズにまで微細化してもリーク電流が許容できる半導体装置を提供する。

【解決手段】 基板100に設けられた不純物層117上のSiO2層119上に設けられた下部電極111、下部電極111上に設けられた強誘電体層109、強誘電体層109上に設けられた上部電極107によってキャパシタ部102を形成する。さらに、上部電極107と配線105とを電気的に絶縁するSiO2層118と、不純物層117と下部電極111とを電気的に接続するためのWプラグ113を形成するコンタクトホール103aと、下部電極111と配線105とを電気的に接続するためのコンタクトホール103bとを備える。コンタクトホール103aとコンタクトホール103bとは、平面視において、キャパシタ部102の中心から偏った位置に開口される。

(もっと読む)

半導体装置及び強誘電体メモリ、半導体装置の製造方法

【課題】 スタック型でありながら必要なサイズにまで微細化してもリーク電流が許容できる半導体装置を提供する。

【解決手段】 基板100に設けられた不純物層117上のSiO2層119上に設けられた下部電極111、下部電極111上に設けられた強誘電体層109、強誘電体層109上に設けられた上部電極107によってキャパシタ部102を形成する。さらに、上部電極107と配線105とを電気的に絶縁するSiO2層118と、不純物層117と下部電極111とを電気的に接続するためのWプラグ113を形成するコンタクトホール103aと、下部電極111と配線105とを電気的に接続するためのコンタクトホール103bとを備える。コンタクトホール103aとコンタクトホール103bとは、キャパシタ部102の平面視において、互いに偏った位置に開口される

(もっと読む)

ナノワイヤによってコンタクトがとられる導電性材料の層を有する電子装置を製造する方法

本発明による電子装置(100)は、第1値と第2値との間で電気的にスイッチ可能な電気抵抗率を有するメモリ材料の層(107)を備える。メモリ材料は相変化材料でもよい。電子装置(100)は電子装置の第1端子(172)とメモリ材料の層(107)を電気的に接続する一組のナノワイヤ(NW)をさらに備え、それによって、第1端子からナノワイヤ(NW)及びメモリ材料の層(107)を介して電子装置の第2端子(272)への電流の伝導を可能にする。各ナノワイヤ(NW)は各々のコンタクト領域でメモリ材料の層(107)に電気的にコンタクトがとられる。全てのコンタクト領域ほぼ同一である。本発明による方法は、本発明による電子装置(100)を製造するのに適している。  (もっと読む)

(もっと読む)

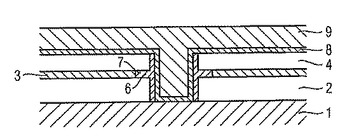

デバイス内にバリア層を有するコンタクトホールを形成する方法及び得られるデバイス

デバイスの下層(2)にコンタクトを形成する方法は、コンタクトホール(5)を形成するステップと、デバイスのコンタクトホール内にバリア材からなるコンタクトホールバリア層(7)を形成するステップと、コンタクトホールの底面のコンタクトホールバリア層をエッチングするステップと、コンタクトホール内にライナ材(8)を堆積するステップと、コンタクトホールに導電性材料(9)を充填するステップとを有する。半導体、受動素子、キャパシタ又はFeRAMなどのデバイスが上記方法に従って形成される。コンタクトホールの側壁にあるコンタクトホールバリア層(7)が、水素及び/又は酸素の側方拡散を抑制する。コンタクトホールバリア層は、ウェットエッチングプロセスによって生じる既存のバリア層(3)内のボイド(6)を充填するために上記プロセス後に、又は既存のバリア層への損傷を抑制するために上記プロセス前に行うことができる。

(もっと読む)

(もっと読む)

垂直方向の突起部を有するフローティングゲート構造

基板面から離れて延在する突起部を有するフローティングゲート構造を開示する。この突起部によって、フローティングゲートとコントロールゲートとを結合するための増加した表面積をフローティングゲートに提供することが可能となる。1つの実施形態では、フローティングゲートの個々の側面でワードラインが下方へ延在して、同じ列の隣接するフローティングゲートを遮蔽する。別の実施形態では、突起部を有するフローティングゲートの組立て製造処理工程を開示する。残りのフローティングゲートに対して自己位置合せを行うために突起部を形成してもよい。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】 多ビットのデータを入出力可能であって、動作速度の遅延や消費電力の増大を抑えたDRAMを提供する。

【解決手段】 このDRAMでは、多数のグローバル入出力線対GIOがサブワードドライバ領域24間のメモリセルアレイ上を走る。ローカル入出力線対LIOはメモリサブブロック26ごとに複数に分割される。グローバル入出力線対GIOとローカル入出力線対LIOを接続するスイッチング素子30はセンスアンプ領域22上に分散して配置される。1つのローカル入出力線対LIOには複数のビット線対が共通に接続される。

(もっと読む)

101 - 115 / 115

[ Back to top ]