Fターム[5F083MA15]の内容

Fターム[5F083MA15]の下位に属するFターム

複数の配線層間 (1,403)

拡散層とキャパシタ電極間 (1,386)

配線層とキャパシタ電極間 (481)

拡散層と配線層間 (3,894)

Fターム[5F083MA15]に分類される特許

41 - 60 / 105

記憶素子および記憶装置

【課題】トレードオフの関係にある繰り返し動作回数と低電圧動作特性とを同時に満足させることの可能な記憶素子を提供する。

【解決手段】下部電極3と上部電極6の間に高抵抗層4とイオン源層5とを備える。高抵抗層4は、Teを含む酸化物から構成されている。Te以外の他の元素、例えばAlや、Zr,Ta,Hf,Si,Ge,Ni,Co,CuおよびAuのいずれかを添加してもよい。TeにAlを添加し、更にCuおよびZrを加えたものとする場合、高抵抗層4の組成比は、酸素を除いて、30≦Te≦100原子%、0≦Al≦70原子%、および0≦Cu+Zr≦36原子%の範囲で調整することが望ましい。イオン源層5は、少なくとも一種の金属元素と、Te,SおよびSeのうち少なくとも一種類のカルコゲン元素とから構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】露光条件が最適化される領域の配線と異なる方向の配線を必要とする領域の露光マージン不足を回避する。

【解決手段】半導体基板と、

前記半導体基板上に形成された層間絶縁膜と、

前記層間絶縁膜上の第1の領域において、第1のデザインルールを適用して形成された、特定方向に沿って走る、複数の第1の配線と、

前記層間絶縁膜上の第2の領域において、前記第1のデザインルールと同じ第2のデザインルールを適用して形成された、前記特定方向に沿って走る、複数の第2の配線と、

前記層間絶縁膜中に形成され、同一電位となるべき少なくとも2つの前記第2の配線を電気的に接続して所望の配線パターンを形成する、接続部材と、

を備える。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】占有面積を縮小化した不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1メタル27、第1メタル27と交差する第2メタル36、第1メタル27及び第2メタル36の交差部でそれらの間に接続されたメモリセルMCを有する単位セルアレイMATを備える。周辺領域Ar2において、所定位置からカラム方向の(4m−3)番目(mは正の整数)及び(4m−2)番目に位置する第1メタル27は、そのロウ方向の一端側にコンタクト接続部27bを有する。周辺領域において、所定位置からカラム方向の(4m−1)番目及び4m番目に位置する第1メタル27は、そのロウ方向の他端側にコンタクト接続部27aを有する。

(もっと読む)

抵抗変化素子、抵抗変化素子の製造方法および半導体メモリ

【課題】低いフォーミング電圧により抵抗部を形成し、抵抗変化素子およびその他の素子の信頼性を向上する半導体メモリを提供する。

【解決手段】抵抗変化素子RESは、第1電極EL1と第2電極EL2との間に並列に配置された複数の絶縁部INS1、INS2と、フォーミングによって絶縁部INS1、INS2の少なくともいずれかに形成され、第1および第2電極EL1、EL2に印加する電圧に応じて抵抗値が変化する抵抗部R1、R2とを有している。抵抗部R1、R2は、絶縁部INS1、INS2のうちブレークダウン電圧が低い絶縁部に形成される。このため、低いフォーミング電圧により抵抗部R1またはR2を形成できる。フォーミング電圧を低くできるため、抵抗変化素子RESおよびその他の素子の信頼性を向上できる。

(もっと読む)

記憶素子及び記憶装置

【課題】圧電素子を用いずに印加された圧力を記憶することができる記憶素子及び記憶装置を提供する。

【解決手段】複数の記憶素子が縦横に並べて配置されている。各記憶素子には、抵抗変化素子を備えた抵抗変化部1、及び印加された圧力に応じて流れる電流が変化する電流変化部2が設けられている。電流変化部2には、定電圧が供給される。抵抗変化部1と電流変化部2との間にはビット線BLが接続され、抵抗変化部1の他端にはトランジスタ3のソース・ドレインの一方が接続されている。トランジスタ3の他方のソース・ドレインは信号線SLに接続され、トランジスタ3のゲートはワード線WLに接続されている。

(もっと読む)

カーボンナノチューブを利用した半導体素子の配線形成方法およびその方法により製造された半導体素子

【課題】高い電流密度を持つカーボンナノチューブを利用した半導体素子の配線形成方法、およびその方法により製造される超高集積度の半導体素子を提供する。

【解決手段】半導体素子の電極120表面を前処理して活性化させる段階と、電極の活性化した表面122上に絶縁層130を形成した後、電極の活性化した表面の一部を露出させるために絶縁層を貫通するコンタクトホール132を形成する段階と、コンタクトホールを通じて電極の活性化した表面に炭素が含まれているガスを供給して前記電極の活性化した表面からカーボンナノチューブ140を成長させて配線を形成する段階と、を具備する半導体素子の配線形成方法およびその方法により製造された半導体素子。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜を介して隣接し、それぞれ低い抵抗値を有する複数のシリサイド層を備え、かつ複数のシリサイド層間の耐電圧特性の劣化および短絡を抑えた半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板上に、絶縁膜を介して前記半導体基板の表面に略平行な方向に隣接する複数のSi系パターン部を形成する工程と、前記複数のSi系パターン部および前記絶縁膜上に、前記複数のSi系パターン部に接するように金属膜を形成する工程と、熱処理により前記複数のSi系パターン部と前記金属膜とをシリサイド反応させ、前記複数のSi系パターン部の全部または上側の一部をそれぞれシリサイド層に加工する工程と、前記複数のシリサイド層に平坦化処理を施し、前記絶縁膜上に形成されたシリサイド層を除去する工程と、を含む。

(もっと読む)

不揮発性メモリならびにその読み出し方法およびその書き込み方法

【課題】高セル密度化と、ビットラインの低抵抗化による高速化が両立し、読み出し、書き込み時の記憶内容への擾乱を受けにくい不揮発性メモリアレイを提供する。

【解決手段】複数のメモリセルは、接続領域411、第1の方向に延びる導電ビット線4010、第2の方向に延びる導電ワード線6030、および導電制御線6010,6020と共に2つの方向に2次元で配置されている。接続領域411は、1つのビット線に接続される4つのセルを含むメモリアレイを通って形成される。接続領域411は、処理を経済的にするために逆導電型領域401と同じ処理ステップで形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセル面積を増加することなく、メモリトランジスタの書き込み電圧および消去電圧を低減する不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルには、第1の島状半導体領域102、フローティングゲート109、コントロールゲート111が有するメモリトランジスタが設けられている。さらに、フローティングゲート109の下方には、絶縁膜を介して第2の島状半導体領域101が形成されている。第2の島状半導体領域101は、コントロールゲート111に電気的に接続されているため、第2の島状半導体領域101とフローティングゲート109間に静電容量が形成される。この静電容量はメモリトランジスタのカップリング比の増加に寄与するため、メモリセルの面積を増加することなく、カップリング比を高くすることが可能になる。また、カップリング比を低下することなく、メモリセルの面積を縮小することが可能になる。

(もっと読む)

半導体装置の製造方法

【課題】メモリセルアレイ領域の微細化を図りつつ選択ゲート領域及び周辺回路領域における抵抗遅延を回避し、かつメモリセルアレイ領域と選択ゲート領域と周辺回路領域とのゲート加工を同時に行う。

【解決手段】半導体装置の製造方法は、半導体層上に第1の絶縁膜12を形成する工程、第1の電極層13を形成する工程、素子分離領域15を形成し、素子領域を分離する工程、第2の絶縁膜16を形成する工程、周辺回路領域10において、第2の絶縁膜を選択的に除去し、第1の電極層の表面を露出する開口部17を形成する工程、第2の絶縁膜及び第1の電極層の露出された表面上に第2の電極層18を形成する工程、第1の電極層、第2の絶縁膜及び第2の電極層を選択的に除去し、ゲート電極を形成する工程、を含む。

(もっと読む)

半導体装置

【課題】セルサイズのさらなる縮小を図ることができる、半導体装置を提供すること。

【解決手段】半導体層2に、トレンチ5が形成されている。半導体層2の表層部には、第1拡散領域3およびドレイン領域が形成されている。第1拡散領域3は、トレンチ5に対して所定方向の一方側に形成され、トレンチ5に隣接している。第2拡散領域6は、所定方向においてトレンチ5に対して第1拡散領域3と反対側に形成され、トレンチ5に隣接している。トレンチ5の底面および側面上には、第1絶縁膜8が形成されている。第1絶縁膜8上には、フローティングゲート11が設けられている。フローティングゲート11は、第1絶縁膜8を挟んで、トレンチ5の底面および側面と対向している。フローティングゲート11上には、第2絶縁膜12が形成されている。第2絶縁膜12上には、コントロールゲート13が設けられている。

(もっと読む)

半導体装置

【課題】メモリセルアレイ領域の微細化を図りつつ選択ゲート領域及び周辺回路領域における抵抗遅延を回避する半導体装置を提供する。

【解決手段】半導体装置は、半導体層上に形成された第1の絶縁膜12と、第1の電極層13と、第1の電極層13及び第1の絶縁膜12を貫通して半導体層内に至るまで形成され、第1の電極層13と自己整合的に形成され、素子領域を分離し、素子分離絶縁膜からなる複数の素子分離領域15と、素子分離領域15を跨いで第1の電極層13上に形成され、第1の電極層13の表面を露出する開口部を有する第2の絶縁膜16と、第2の絶縁膜16上及び第1の電極層13の露出された表面上に形成され、開口部を介して第1の電極層13と電気的に接続され、第1の電極層13よりも抵抗の低い第2の電極層18と、素子分離領域15の上方に位置し、第2の電極層18に電気的に接続されたコンタクトホール20と上層配線21とを具備する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】個々のメモリセルの電荷蓄積量が多い不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】シリコン基板11上に、それぞれ複数の絶縁膜12及び電極膜13を交互に積層して積層体14を形成する。次に、積層体14を積層方向に貫通する貫通孔15を形成する。このとき、貫通孔15における電極膜13内に位置する部分の側面15aを、貫通孔15の中心軸15cを含む断面において、貫通孔15の内側から見て凹状に湾曲させる。その後、貫通孔15の側面上に電荷蓄積層26を形成し、貫通孔15の内部に半導体ピラー17を形成する。

(もっと読む)

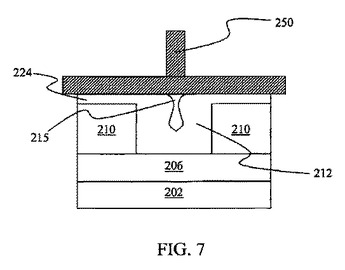

相変化メモリデバイスに電極を形成する方法

サブリソグラフィックな寸法又は高アスペクト比を含む、小寸法の開口内に電極材料を均一に形成する方法を提供する。この方法は、内部に形成された開口を有する絶縁層を提供するステップと、開口の上部及び内部に非等質的導電又は準抵抗性材料を形成するステップと、導電材料を移動化して開港内に圧縮するステップとを有する。この方法は、導電又は準抵抗性材料における空孔又は欠陥密度を堆積されたままの状態に対して低減する。移動化するステップは、押出又は熱的リフローによって達成され、空隙又は欠陥を合体、崩壊、染み透り又は他の方法によって堆積したままの導電又は準抵抗性材料から除去する。  (もっと読む)

(もっと読む)

相変化メモリ素子及びその製造方法

【課題】高集積化が可能であり、相変化物質層と発熱層との接触面積を低減することにより、相変化メモリ素子の動作電流量を減少させることができる相変化メモリ素子及びその製造方法を提供する。

【解決手段】相変化メモリ素子は、下部電極43と、下部電極43を共有する少なくとも2つの相変化メモリセル53と、を備える。各々の相変化メモリセル53は、下部電極43の対応する分離領域上に形成された発熱層45と、発熱層45を覆うように形成された相変化物質層46と、相変化物質層46上に形成された上部電極47とを備える。また、相変化メモリ素子は、発熱層45と下部電極43の分離領域との間を埋め込む第2絶縁膜48をさらに備えることができる。

(もっと読む)

電気機械的スイッチ及びこれの形成方法

【課題】電気機械的スイッチ及びこれの形成方法を提供すること。

【解決手段】メモリ素子は、メモリセル内に具備されるストレージノード、第1、及び第2電極を含む。前記ストレージノードは電荷を保存し、前記第1電極は第2部分と電気的に接続するための第1部分を含む。前記第2電極が活性化された際、前記第1部分は前記ストレージノードと接続するように移動する。

(もっと読む)

抵抗メモリ素子及びその形成方法

【課題】高い集積度で集積化が可能である相変化メモリ素子及びその形成方法を提供する。

【解決手段】高い集積度で集積化が可能である抵抗メモリ素子及びその形成方法が提供される。抵抗メモリ要素130を包む絶縁膜150と抵抗メモリ要素に連結される配線180を包む絶縁膜160が異なる応力、硬度、多孔率、誘電率、または熱伝導率を示す。

(もっと読む)

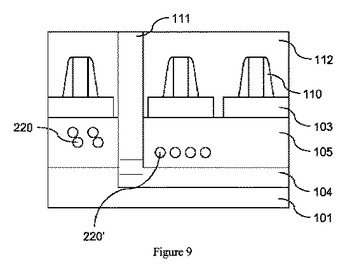

埋め込み型トラッピング層によるトランジスタの閾値電圧の調整方法

方法は、電子サブアセンブリの形成について、調整可能な閾値電圧を有する少なくとも1つの第1のトランジスタ(110)を担持する半導体層(103)が絶縁層(102、105)に接合される組み立てステップと、半導体層および第1のトラッピングゾーンが容量結合されるように、第1のトラッピングゾーン(220)が所定の第1の深さで絶縁層に形成される形成ステップであって、前記第1のトラッピングゾーンが、前記第1のトランジスタのチャネルの少なくとも下に延び、かつ前記第1のトラッピングゾーンの外側のトラップの密度より高い密度のトラップを有する形成ステップとを含み、前記第1のトランジスタからの有用な情報はこのトランジスタ内の電荷移動である。具体的な実施形態において、第2のトランジスタのチャネルの少なくとも下に延びる第2のトラッピングゾーンが、第1のトラッピングゾーンに使用されるのとは異なるエネルギーおよび/または用量および/または原子の第2の注入によって形成される。  (もっと読む)

(もっと読む)

抵抗変化型メモリ

【課題】ディスターブとリテンションを改善する書き込み技術を提案する。

【解決手段】本発明の抵抗変化型メモリは、第1方向に延びる第1及び第2駆動線L1,L2と、第2方向に延びる第3駆動線L3と、一端が第3駆動線L3に接続される抵抗変化素子MCと、アノードが第1駆動線L1に接続され、カソードが抵抗変化素子MCの他端に接続される第1ダイオードD1と、アノードが抵抗変化素子MCの他端に接続され、カソードが第2駆動線L2に接続される第2ダイオードD2と、抵抗変化素子MCに書き込み電流を供給するドライバ/シンカーDSと、抵抗変化素子MCに対する第1データの書き込み時に書き込み電流を第1駆動線L1から第3駆動線L3に向かう方向に流し、抵抗変化素子MCに対する第2データの書き込み時に書き込み電流を第3駆動線L3から第2駆動線L2に向かう方向に流す書き込み制御回路CNTとを備える。

(もっと読む)

インクジェット式記録ヘッドおよびインクジェットプリンタ

【課題】各種特性に優れた電子デバイスを最適な構造で実現することができる電子デバイス用基板、および、かかる電子デバイス用基板を備える電子デバイス、さらに、かかる電子デバイスを備える強誘電体メモリ、電子機器、インクジェット式記録ヘッドおよびインクジェットプリンタを提供する。

【解決手段】電子デバイス用基板100は、アモルファス層15を有する基板11と、アモルファス層15上に、少なくとも厚さ方向に配向方位が揃うよう形成されたバッファ層12と、バッファ層12上にエピタキシャル成長により形成され、ペロブスカイト構造を有する金属酸化物を含む導電性酸化物層13とを有している。バッファ層12は、NaCl構造の金属酸化物、蛍石型構造の金属酸化物のうちの少なくとも1種を含むものであるのが好ましく、また、立方晶(100)配向でエピタキシャル成長したものであるのが好ましい。

(もっと読む)

41 - 60 / 105

[ Back to top ]