Fターム[5F083PR48]の内容

半導体メモリ (164,393) | プロセス (23,970) | メモリセルと周辺回路の同時形成 (5,561) | メモリセル (2,770) | キャパシタ用下部電極 (50)

Fターム[5F083PR48]に分類される特許

1 - 20 / 50

半導体装置の製造方法及び半導体装置

【課題】ガードリング周辺のメモリセル領域から周辺回路領域へのエッチング液の染み込みを防止する。

【解決手段】半導体装置の製造方法は、メモリセル領域及び周辺回路領域が画定された半導体基板上に第1の層間絶縁膜を形成し、第1の層間絶縁膜の一部を除去してメモリセル領域の周囲にガードリング溝を形成し、ガードリング溝を金属導電材で埋めてガードリングとし、ガードリングを覆うように第1の層間絶縁膜上にサポート膜を形成し、メモリセル領域のサポート膜に開口を形成し、開口を通してウエットエッチングを行うことで、周辺回路領域の第1の層間絶縁膜を残したまま、メモリセル領域の第1の層間絶縁膜を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】容量絶縁膜の絶縁性の劣化が生じにくく、かつ容量プレート電極の厚みが薄い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、互いに異なる平面面積を持つメモリセル部と補償容量部とを単一の基板上に備える。メモリセル部と補償容量部とは、同一構成の容量プレート電極を含む。容量プレート電極は、ボロンドープシリコンゲルマニウム膜と金属膜とを含む積層構造を有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】メモリ・ロジック混載型の半導体装置の高性能化を可能にする技術を提供する。

【解決手段】ストッパ膜17は、ストッパ膜13及び層間絶縁膜14から成る絶縁層上に形成されている。コンタクトプラグ16,65,66のそれぞれは、その上面がストッパ膜17から露出するように、ソース・ドレイン領域9,59とそれぞれ電気的に接続されてストッパ膜13、層間絶縁膜14及びストッパ膜17に設けられている。絶縁層20は、ストッパ膜17及びコンタクトプラグ16,65,66の上に設けられている。キャパシタ82の下部電極は、メモリ形成領域において、コンタクトプラグ66の上面とストッパ膜17の上面とに接触するように絶縁層20内に設けられている。

(もっと読む)

半導体装置

【課題】DRAM回路などのように容量を内蔵する半導体装置において、コンタクト容量およびコンタクト抵抗を増加させることなく、容量の容量値を増加させる。

【解決手段】セルコンタクトが形成されるセルコンタクト部にまで容量の形成場所を延長することで、容量値のさらなる増大が可能となる。なお、容量部、容量コンタクト部およびセルコンタクト部にまたがる容量の形成には、ALD法などによるスパッタ装置を用いることが好ましい。

(もっと読む)

半導体装置及び半導体装置を用いたデータ処理システム

【課題】補償容量素子を構成する複数のクラウン型下部電極を備えた容量ブロック間を上部電極で直列接続する際、容量ブロック間に空洞が形成されることを防止する。

【解決手段】2つの隣接する、異なる共通パッド電極(22c、22d)上に形成された容量ブロック(第1ブロック及び第2ブロック)が、上部電極36cで電気的に直列に接続され、上部電極36cで直列接続される2つの隣接する容量ブロック間の間隔D1を、それぞれの容量ブロックの最外周で対向する下部電極間の距離として、2つのブロック間に埋設される上部電極膜の膜厚の2倍以下とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】補償容量素子のキャパシタ構造に起因したリーク電流の増加を抑制するとともに、立体構造のキャパシタ構造を採用して、占有面積を削減した半導体装置を提供する。

【解決手段】メモリセル領域に形成されたクラウン型のキャパシタ21aと、周辺回路領域に形成されたコンケイブ型の補償容量素子10と、を有することを特徴とする半導体装置20を提供する。また、第1層間絶縁膜上にパッド47a,47bを形成する工程と、パッド47a,47b上に有底筒形状の下部電極66a,66bを形成する工程と、メモリセル領域の下部電極66aの内壁面及び外壁面と、周辺回路領域の下部電極66bの内壁面のみを誘電体膜67a,67bで覆う工程と、誘電体膜上に上部電極69a,69bを形成する工程と、を有することを特徴とする半導体装置20の製造方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体膜の表面をレジストに曝すことなく、特性が異なる複数のキャパシタを有する半導体装置を製造する。

【解決手段】半導体装置の製造方法は、基板上方に絶縁膜を形成する工程、絶縁膜上方に下部電極層を形成する工程、下部電極層上に強誘電体膜を形成する工程、強誘電体膜上に第1上部電極層を形成する工程、第1上部電極層上に、第1領域を覆う第1レジストを形成する工程、第1レジストをマスクとしてエッチングを行うことにより、第2領域の第1上部電極層を除去するとともに、第2領域の強誘電体膜を削る工程、第1領域の第1上部電極層上及び第1領域以外の強誘電体膜上に、第2上部電極層を形成する工程、第1領域及び第2領域に第2レジストを形成する工程、第2レジストをマスクとして第1上部電極層、第2上部電極層、強誘電体膜及び下部電極層をエッチングし、第1のキャパシタ及び第2のキャパシタを形成する工程、を有する。

(もっと読む)

半導体装置及びその製造方法

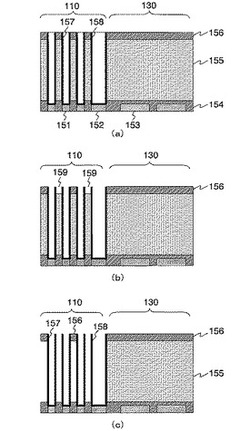

【課題】強誘電体キャパシタ及び常誘電体キャパシタの両方を有する半導体装置を比較的少ない工程で製造できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板110にトランジスタ等を形成した後、メモリセル形成領域及びロジック回路形成領域にそれぞれ強誘電体膜127を電極126a,128aで挟んだ構造の強誘電体キャパシタを形成する。その後、強誘電体キャパシタを覆う層間絶縁膜131を形成し、更にその上にアルミナからなる保護膜132を形成する。そして、ロジック回路形成領域の保護膜132を除去する。これにより、半導体装置の製造工程が完了するまでの間にロジック回路形成領域の強誘電体膜127に水素及び水分が侵入して強誘電体特性が劣化し、強誘電体キャパシタが常誘電体キャパシタとなる。一方、メモリセル形成領域の強誘電体キャパシタは、保護膜132により強誘電体特性が保持される。

(もっと読む)

キャパシタ、該キャパシタを備える半導体装置および半導体装置の製造方法

【課題】アスペクト比の高い電極を上下に接続して、静電容量の大きいキャパシタを形成する際、電極間の剥離を防止し、電極の倒壊を抑制する。

【解決手段】導電膜を外壁に有する下部電極30と、該下部電極の導電膜に対して、容量絶縁膜を介して形成された上部電極とを有するキャパシタにおいて、下部電極は少なくとも2層の積層構造であって、該積層構造は、下層側電極18に設けた掘り込み部に上層側電極22の底部が埋め込まれた構造であるキャパシタ。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜を除去するエッチング中に、異常エッチングを防止する。エッチング工程において加わる水圧や風圧によりガードリングの形状が変形して剥離し、欠陥が発生することを防止する。

【解決手段】半導体装置は、メモリセル領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた周辺回路領域と、ガードリング及び周辺回路領域上に設けられた支持体膜と、周辺回路領域内に設けられたコンタクトプラグとを有する。ガードリングとコンタクトプラグは、同一の導電材料から構成される。

(もっと読む)

半導体装置

【課題】効率的にかつ確実にブロー状態に設定しかつ通常動作モード時に、確実に、プログラム情報を保持する所望の耐圧特性を有するキャパシタ型アンチヒューズを実現する。

【解決手段】プログラムモード時と通常動作モード時とで、キャパシタ型アンチヒューズに対する電圧印加極性を変更する。

(もっと読む)

半導体装置

【課題】動作速度が低下することを抑制することができる半導体装置を提供する。

【解決手段】半導体装置は、MOSトランジスタ9を有するシリコン基板5と、シリコン基板5上に形成され、配線および絶縁膜により構成された配線層が複数積層された多層配線層と、多層配線層内に埋め込まれた、下部電極(下部電極膜91)、容量絶縁膜92、および上部電極(上部電極膜93)を有しており、メモリ素子を構成する容量素子90と、を備え、容量素子90とMOSトランジスタ9との間にダマシン形状の銅配線(第2層配線25)が少なくとも1層以上形成され、1つの配線(第2層配線25)の上面と容量素子90の下面とが略同一平面上にあり、容量素子90上に銅配線(プレート線配線99)が少なくとも1層以上形成されている。

(もっと読む)

半導体装置

【課題】半導体装置の歩留まりを向上させること若しくは製造コストを低減すること又は集積回路の面積を低減する半導体装置を提供する。

【解決手段】半導体装置が有するメモリ素子10のメモリ層12及び抵抗素子20の抵抗層22が同一材料によって構成される。そのため、メモリ層12と、抵抗層22とを同一工程によって形成することで、半導体装置の作製工程数を低減することができる。結果として、半導体装置の歩留まりを向上させること又は製造コストを低減することができる。また、半導体装置は、抵抗値の高い抵抗成分を備えた抵抗素子20を有する。そのため、半導体装置が有する集積回路の面積を低減することができる。

(もっと読む)

半導体装置

【課題】同一の半導体基板上に容量素子を備えたメモリ回路部と論理回路部を有する半導体集積回路装置において、論理回路部のみからなる半導体集積回路装置と完全互換の配線設計パラメーターを確保し、かつ微細化が進んでもセル容量を確保する。

【解決手段】容量素子を備えたメモリ回路部と論理回路部を同一の半導体基板上に有する半導体集積回路装置において、論理回路部に形成される多層配線を絶縁分離する層間絶縁膜の少なくとも複数の配線層にまたがる領域に該容量素子を埋め込むことで、該容量素子の接続に必要な配線をすべて論理回路部の多層配線で構成することにより、論理回路部の設計パラメーターを、該メモリ回路部を有しない半導体集積回路装置と完全に同一とする。また多層配線の複数層に渡るように該容量素子を配置させることで該容量素子の高さを確保し、スケーリングが進んでも必要な容量値を確保する。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリと、精度が低くても高耐圧性が要求されるキャパシタと、耐圧性が低くても高精度が要求されるキャパシタとを備えた半導体装置を比較的少ない工程で製造できる半導体装置の製造方法を提供する。

【解決手段】半導体基板10上に形成されたシリコン膜13により、フラッシュメモリのフローティングゲートと高耐圧キャパシタの下部電極13bとを形成する。この場合、シリコン膜13中の不純物濃度を、フラッシュメモリに適した濃度とする。その後、半導体基板10に不純物をイオン注入して高精度キャパシタの下部電極となる高濃度不純物領域15を形成する際に、高耐圧キャパシタの下部電極13bに不純物を追加注入し、下部電極13bの不純物濃度を向上させる。次いで、高精度キャパシタの誘電体膜12を、増速酸化により形成する。

(もっと読む)

高い絶縁破壊電圧の埋め込まれたMIMキャパシタ構造体

高い絶縁破壊電圧の埋め込まれた複数のキャパシタに関連する方法及び装置が提供される。半導体装置は、絶縁体(209)に埋め込まれたゲート材料(204)、複数の金属接触部(213)及び複数のキャパシタ(C1−C4)を含み得る。複数のキャパシタは、下部電極(217)、下部電極の表面を覆うように形成される誘電体(219)及び誘電体に形成される上部電極(221b、c)を含み得る。さらに、複数の接触部は、複数のキャパシタの下部電極の各々をゲート材料に接続し得る。複数のキャパシタは、ゲート材料を介して直列に接続され得る。  (もっと読む)

(もっと読む)

半導体装置

【課題】回路を形成する領域を確保しつつ、十分な耐圧、容量を備えた容量素子を備える半導体装置を提供する。

【解決手段】半導体装置は、DRAMセルのキャパシタ上部電極19と、上部電極19の下方に形成されたキャパシタ下部電極17とを含む情報記憶部と、情報記憶部へのアクセスを制御するアクセストランジスタとを有するメモリセルと、アクセストランジスタに接続され、情報記憶部にデータの書き込み又は読み出しを行うビット線16と、アクセストランジスタのゲート電極に接続され、アクセストランジスタを制御するワード線と、キャパシタ上部電極19の上方に形成された第1金属配線21と同一層からなる上部電極23と、キャパシタ上部電極19と同一層の下部電極22とを有し、メモリセルが形成された領域外に形成された容量素子とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタの下部電極のダメージを抑制することができる半導体装置およびその製造方法を提供するものである。

【解決手段】本発明の半導体装置は、立設する複数の電極と、前記電極の立設を保持する第1の絶縁膜と、前記電極が貫通するように前記第1の絶縁膜に形成され、各々の前記電極の外周側面の少なくとも一部に接触する複数の孔部と、前記第1の絶縁膜に形成され、前記複数の孔部のうちその一部の孔部に連結する第1の開口と、前記第1の絶縁膜に形成され、前記複数の孔部のいずれの孔部に対してよりも前記溝部に近接する位置に配置すると共に前記複数の孔部のいずれにも連結しない第2の開口とを、備えたことを特徴とすることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】リソグラフィ工程におけるアライメントマークや重ね合わせ検査マークの計測が確実に、精度良くでき、また、マークにとって不要な構成を有さず、半導体装置の製造プロセスの過程で異物が発生することを抑制して製造歩留が低下することを防止した半導体装置の製造方法および半導体装置を提供する。

【解決手段】マーク構造体100はシリコン基板101上に形成されたゲート酸化膜102と、ゲート酸化膜102上に形成されたゲート配線層103と、ゲート配線層103上に形成された絶縁膜104と、絶縁膜104、ゲート配線層103、ゲート酸化膜102の側面に接するように形成されたサイドウォール105とで構成され、層間絶縁膜107の上部からマーク構造体100の上部にかけては、不透明なビット線層113が、ドープトポリシリコン層1131と、タングステンシリサイド層1132のポリサイドとして構成されている。

(もっと読む)

システムオンチップアプリケーション用二重誘電体MIMコンデンサ

【課題】システムオンチップアプリケーション用の二重誘電体MIMコンデンサを提供する。

【解決手段】集積回路構造は、第1領域と第2領域とを有するチップを含む。第1金属‐絶縁体‐金属(MIM)コンデンサは、第1領域に形成される。第1MIMコンデンサは、第1下部電極と、第1下部電極の上の第1上部電極と、第1下部電極と第1上部電極との間に位置および隣接する第1キャパシタ絶縁体とを有する。第2MIMコンデンサは、第2領域に位置し、第1MIMコンデンサと実質的に同じレベルに位置する。第2MIMコンデンサは、第2下部電極と、第2下部電極の上の第2上部電極と、第2下部電極と第2上部電極との間に位置および隣接する第2キャパシタ絶縁体を有する。第2キャパシタ絶縁体は第1キャパシタ絶縁体と異なる。第1上部電極および第1下部電極は、それぞれ第2上部電極および第2下部電極と同時に形成されることができる。

(もっと読む)

1 - 20 / 50

[ Back to top ]