Fターム[5F083PR54]の内容

半導体メモリ (164,393) | プロセス (23,970) | メモリセルと周辺回路の同時形成 (5,561) | 周辺回路 (2,703) | ゲート絶縁膜 (656)

Fターム[5F083PR54]に分類される特許

161 - 180 / 656

半導体記憶装置及び半導体記憶装置の製造方法

【課題】フローティングゲートとコントロールゲートとのオーバーラップ量のバラツキを抑制する。

【解決手段】基板(1)と、ゲート絶縁膜(2)を介してその基板(1)の上に設けたれたフローティングゲート(20)と、トンネル絶縁膜(30)を介してそのフローティングゲート(20)の隣に設けられたコントロールゲート(50)と、そのフローティングゲート(20)の上に設けられたスペーサー絶縁膜(9)と、そのスペーサー絶縁膜(9)とそのコントロールゲート(50)との間に設けられた保護膜(7)とを具備する半導体記憶装置(MC)を構成する。そのような半導体記憶装置(MC)において、その保護膜(7)は、スペーサー絶縁膜(9)以外の部分をエッチングするときに、スペーサー絶縁膜(9)の側面のストッパーとして機能している。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1上に複数のロジック用pチャネル型MISFETQp1と、複数のロジック用nチャネル型MISFETQn1と、複数のメモリ用pチャネル型MISFETQp2と、複数のメモリ用nチャネル型MISFETQn2とが混載されている。複数のロジック用pチャネル型MISFETQp1のうちの少なくとも一部は、シリコンゲルマニウムで構成されたソース・ドレイン領域を有し、複数のロジック用nチャネル型MISFETQn1の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。複数のメモリ用pチャネル型MISFETQp2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有し、複数のメモリ用nチャネル型MISFETQn2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】選択トランジスタの閾値が安定した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置1において、シリコン基板11に複数本のSTI17を形成して、シリコン基板11の上層部分を複数本のアクティブエリアAAに区画する。また、アクティブエリアAA上にトンネル絶縁膜14及び電荷蓄積膜15を設け、STI17を覆うようにブロック絶縁膜18を設け、その上にワード電極WL及び選択ゲート電極SGを設ける。そして、STI17の上面17aにおける選択ゲート電極SGの直下域を、ワード電極WLの直下域よりも上方に位置させることにより、アクティブエリアAAの角部と選択ゲート電極SGとの間の最短距離を、アクティブエリアAAの角部とワード電極WLとの間の最短距離よりも長くする。

(もっと読む)

不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法

【課題】ビット線方向のセル間干渉を解消する不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板1と、半導体基板1を複数の素子領域に分離する素子分離絶縁膜2と、半導体基板1の素子領域上に形成されたトンネル絶縁膜3と、トンネル絶縁膜3上に形成されたフローティングゲート電極4と、積層絶縁膜5を介して、フローティングゲート電極4上及びチャネル幅方向に隣接するフローティングゲート電極4間に形成された第1コントロールゲート電極6と、半導体基板1の素子領域のチャネル幅方向に面する側面に形成されたアシスト絶縁膜7と、アシスト絶縁膜7を介して、複数の素子領域間に形成された第2コントロールゲート電極8と、を備えている。

(もっと読む)

半導体装置

【課題】不揮発性メモリセルの面積を増大することなく、かつ、製造プロセスを変更することなく、不揮発性メモリセルのデータ書き込み速度およびデータ消去速度の向上を図ることのできる技術を提供する。

【解決手段】データ書き込み・消去用の容量部CWE、データ読み出し用のMIS・FETQRおよび容量部Cを互いに異なる位置に分離した状態で配置する。容量部Cの容量電極FGC2を覆う絶縁層6上にキャップ電極CAPを設けることにより、容量部Cは、容量電極FGC2とp型のウエルHPW1との間の容量およびキャップ電極CAPと容量電極FGC2との間の容量を加算した容量を有する。また、データ書き込み・消去用の容量部CWEにおけるデータの書き換えはチャネル全面のFNトンネル電流により行う。

(もっと読む)

半導体装置の製造方法

【課題】不揮発性メモリを有する半導体装置を小型にする。

【解決手段】複数の第1電極4Gと、これに交差する複数のワード線5と、複数の第1電極4Gの隣接間であって複数のワード線5が平面的に重なる部分に配置された複数の浮遊ゲート電極6Gとを有する複数の不揮発性メモリセルMCを持つAND型のフラッシュメモリにおいて、上記複数の浮遊ゲート電極6Gの各々の断面形状を上記第1電極4Gよりも高い凸状とした。これにより、不揮発性メモリセルMCが微細化されても浮遊ゲート電極6Gを容易に加工できる上、不揮発性メモリセルMCの占有面積を増大させることなく浮遊ゲート電極6Gとワード線5の制御ゲート電極とのカップリング比を向上させることができる。

(もっと読む)

ナノ構造ベースNANDフラッシュセルおよびその周辺回路の形成方法

ナノ構造に基づく電荷蓄積領域は、不揮発性メモリ装置に備えられており、選択ゲートおよび周辺回路の製造と一体に製造される。1つ以上のナノ構造コーティングは、メモリアレイ領域および周辺回路領域の基板に塗布される。選択ゲートや周辺トランジスタについての目標領域などの基板の不要な領域から、ナノ構造コーティングを除去するための様々な工程が、行われる。一例では、基盤のアクティブ領域にナノ構造を選択的に形成するために、自己組織化に基づく工程を用いて、1つ以上のナノ構造コーティングが形成される。自己組織化によって、ナノ構造コーティングのパターニングやエッチングを行うことなく、互いに電気的に分離されているナノ構造の個別のライン群を形成することができる。  (もっと読む)

(もっと読む)

不揮発性半導体集積回路装置

【課題】不揮発性半導体集積回路装置のチップサイズを縮小させる。

【解決手段】シリコン基板上に隣り合って配置された第1および第2ゲート電極とそれらの側方下部のシリコン基板に形成された一対のソース・ドレイン領域とを有し、第2ゲート電極とシリコン基板との間に配置された第2ゲート絶縁膜に電荷を蓄えることで情報を記憶するメモリセルにおいて、メモリセルの消去動作時には、消去非選択セルの第1ゲート電極に正電圧を印加する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートコンタクトプラグとシリコン基板とのショートを防ぐ。

【解決手段】半導体装置10は、半導体基板11と、半導体基板11の主面に対して垂直な側面を有するシリコンピラー14Bと、シリコンピラー14Bの側面を覆うゲート絶縁膜15Bと、半導体基板11の主面に対して垂直な内周側面16a及び外周側面16bを有し、ゲート絶縁膜15Bを介して内周側面16aとシリコンピラー14Bの側面とが対向するよう、シリコンピラー14Bの側面を覆うゲート電極16と、ゲート電極16の外周側面16bの少なくとも一部を覆うゲート電極保護膜17と、ゲート電極16及びゲート電極保護膜17の上方に設けられた層間絶縁膜30と、層間絶縁膜30に設けられたコンタクトホールに埋め込まれ、ゲート電極16及びゲート電極保護膜17に接するゲートコンタクトプラグGCとを備える。

(もっと読む)

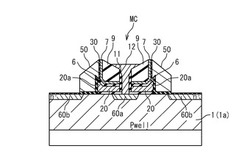

不揮発性半導体記憶装置

【課題】高性能な書きこみ消去特性を有する不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板のp型ウエル2上にゲート絶縁膜6を介して選択ゲート18が形成され、p型ウエル2上に酸化シリコン膜15a、窒化シリコン膜15bおよび酸化シリコン膜15cからなる積層膜15を介してメモリゲート17が形成される。メモリゲート17は、積層膜15を介して選択ゲート18に隣接する。p型ウエル2の選択ゲート18およびメモリゲート17の両側の領域には、ソース、ドレインとしてのn型の不純物拡散層20,21が形成されている。不純物拡散層20,21の間に位置するチャネル領域のうち、選択ゲート18により制御され得る領域51とメモリゲート17により制御され得る領域52とにおける不純物の電荷密度が異なる。

(もっと読む)

半導体装置およびその製造方法

【課題】各々ばらつきの少ない異なる閾値電圧を有する複数のトランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板2上に形成された高誘電率材料を母材料とするゲート絶縁膜11、ゲート電極12、およびゲート絶縁膜11に接するように形成されたSiNを主成分とする絶縁材料からなるオフセットスペーサ13、を有する低閾値電圧MISFET10と、半導体基板2上に形成された高誘電率材料からなるゲート絶縁膜21、ゲート電極22、およびゲート絶縁膜21に接するように形成されたSiNを主成分とする絶縁材料からなるオフセットスペーサ23、を有する高閾値電圧MISFET20と、を有し、オフセットスペーサ23は、オフセットスペーサ13よりも、単位体積当たりのSi−H結合とN−H結合の存在比、単位体積当たりのClの量、および単位体積当たりのHの量の少なくともいずれか1つが大きい。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】微細化が進んだ場合であってもトランジスタのカットオフ特性を改善する。

【解決手段】半導体基板100上に形成されるp型ウェル2には、ビット線BLの長手方向に沿って形成されたトレンチ3に素子分離絶縁膜4が埋め込まれている。素子分離絶縁膜4によりp型ウェル2が分離され、メモリトランジスタが形成される素子形成領域2Aが形成される。素子分離絶縁膜4にはボロン等のp型不純物が注入されており、その不純物濃度は、p型ウェル2の不純物濃度よりも大きい。

(もっと読む)

半導体装置

【課題】回路を形成する領域を確保しつつ、十分な耐圧、容量を備えた容量素子を備える半導体装置を提供する。

【解決手段】半導体装置は、DRAMセルのキャパシタ上部電極19と、上部電極19の下方に形成されたキャパシタ下部電極17とを含む情報記憶部と、情報記憶部へのアクセスを制御するアクセストランジスタとを有するメモリセルと、アクセストランジスタに接続され、情報記憶部にデータの書き込み又は読み出しを行うビット線16と、アクセストランジスタのゲート電極に接続され、アクセストランジスタを制御するワード線と、キャパシタ上部電極19の上方に形成された第1金属配線21と同一層からなる上部電極23と、キャパシタ上部電極19と同一層の下部電極22とを有し、メモリセルが形成された領域外に形成された容量素子とを備える。

(もっと読む)

半導体装置

【課題】第1導電型の半導体層とトンネルウィンドウが対向する第2導電型の不純物拡散領域との高い接合耐圧を得ることができる、半導体装置を提供する。

【解決手段】各メモリセルにおいて、半導体基板2の表層部には、N型の第1不純物拡散領域3が形成されている。また、半導体基板2の表層部には、第1不純物拡散領域3に対して所定方向の一方側に、第1不純物拡散領域3と間隔を空けて、N型の第2不純物拡散領域4が形成されている。半導体基板2上には、第1絶縁膜6が形成されている。第1絶縁膜6には、第1厚膜部8が形成されており、第2不純物拡散領域4の全周縁は、第1厚膜部8の直下に位置している。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

表示装置

【課題】アクティブマトリクス型の表示装置の画素に組み込むことが可能な超小型のメモリ素子を提供する。

【解決手段】メモリ素子1は、薄膜トランジスタTFTと抵抗変化素子ReRAMとの並列接続からなる。抵抗変化素子ReRAMは、薄膜トランジスタTFTの入力端側に接続する一方の導電層と、薄膜トランジスタTFTの出力端側に接続する他方の導電層と、両導電層の間に配された少なくとも一層の酸化膜層とからなり、ゲートに印加される電圧に応じて薄膜トランジスタTFTがオフ状態にある時、抵抗変化素子ReRAMは、入力端から印加される電圧に応じて、低抵抗状態LRSと高抵抗状態HRSとで変化し、対応する二値データが書込まれる。

(もっと読む)

半導体装置とその製造方法

【課題】周辺回路領域に形成されるロジック回路等に不具合が発生するのを防ぐことができるフラッシュメモリセルを備えた半導体装置とその製造方法を提供すること。

【解決手段】第1導電体25aのコンタクト領域CR上の第2絶縁膜26を除去する工程と、第2絶縁膜26の上に第2導電膜30を形成する工程と、第1導電体25aのコンタクト領域CR上の第2導電膜30を除去し、該第2導電膜30を第2導電体30aとする工程と、第2導電体30aを覆う層間絶縁膜(第3絶縁膜)44を形成する工程と、コンタクト領域CR上の層間絶縁膜44に第1ホール44aを形成する工程と、コンタクト領域CRと電気的に接続される導電性プラグ45aを第1ホール44a内に形成する工程と、を有することを特徴とする半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】ストレージ拡散層を介したリーク電流の抑制が図られたメモリセルの作製に適した、半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、第1導電型領域上に、ゲート絶縁膜とゲート電極の積層構造、及びキャパシタ絶縁膜とキャパシタ電極の積層構造を有する半導体基板を準備する工程と、ゲート電極とキャパシタ電極とを覆って半導体基板上に絶縁膜を形成する工程と、ゲート電極とキャパシタ電極との間の第2領域、及びゲート電極に対しキャパシタ電極と反対側の第3領域に、絶縁膜を通して第1導電型と反対の第2導電型の不純物を注入する工程と、絶縁膜をエッチングしてゲート電極側壁上にサイドウォールを残す工程と、第2領域上にマスク部材を形成する工程と、ゲート電極と、キャパシタ電極と、マスク部材と、ゲート電極側壁上のサイドウォールをマスクとし、第3領域に第2導電型不純物を注入する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 LDD構造を有するMISFETの低濃度部を形成するためのサイドウォールスペーサが、ゲート電極同士を近づけて配置する妨げになる。

【解決手段】 活性領域の上に、ゲート絶縁膜とゲート電極とを含むゲート積層構造を形成する。ゲート積層構造をマスクとして第1不純物を導入する。ゲート積層構造を、絶縁材料の第1の膜で覆う。第1の膜の上に、絶縁材料の第2の膜を形成する。第2の膜及び第1の膜を異方性エッチングして第1の活性領域を露出させ、ゲート積層構造の側面上に、第1の膜と第2の膜との少なくとも2層を含むサイドウォールを残す。ゲート積層構造及びサイドウォールをマスクとして、第2不純物を導入する。サイドウォールを構成する2層のうち、第2の膜を選択的に除去する。ゲート積層構造、残存する第1の膜、及び活性領域を覆うように、層間絶縁膜を形成する。層間絶縁膜内に、活性領域に電気的に接続される導電プラグを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】写真製版プロセスのマージンを大幅に拡大でき、かつマイクロローディング効果を低減することによって「開口不良」を抑制できるとともに「ショート」のプロセス裕度を確保しやすくし、かつコンタクト抵抗を低減できる半導体装置の製造方法を提供する。

【解決手段】活性領域に対して傾斜して延びるようにゲート電極層50と窒素を含む絶縁膜2とが積層される。シリコン酸化膜5が形成される。活性領域の幅より大きくかつ互いに隣り合う活性領域のピッチより小さい帯状の開口パターンが絶縁膜2に形成され、開口パターンから1対の不純物拡散領域の各々が露出させられる。開口パターンが導電層23で埋め込まれる。導電層23から1対の不純物拡散領域の各々に電気的に接続されたプラグ導電層23a、23bが形成されるとともに、プラグ導電層23a、23bの各上面と絶縁膜2の上面とが同一平面とされる。

(もっと読む)

161 - 180 / 656

[ Back to top ]